# Design of radiation-hard CMOS sensors for particle detection applications

Berdalović, Ivan

Doctoral thesis / Disertacija

2019

Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Zagreb, Faculty of Electrical Engineering and Computing / Sveučilište u Zagrebu, Fakultet elektrotehnike i računarstva

Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:168:593406

Rights / Prava: In copyright/Zaštićeno autorskim pravom.

Download date / Datum preuzimanja: 2025-01-13

Repository / Repozitorij:

FER Repository - University of Zagreb Faculty of Electrical Engineering and Computing repozitory

### University of Zagreb

FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Ivan Berdalović

### DESIGN OF RADIATION-HARD CMOS SENSORS FOR PARTICLE DETECTION APPLICATIONS

DOCTORAL THESIS

Zagreb, 2019

### University of Zagreb

FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Ivan Berdalović

### DESIGN OF RADIATION-HARD CMOS SENSORS FOR PARTICLE DETECTION APPLICATIONS

DOCTORAL THESIS

Supervisor: Professor Tomislav Suligoj, PhD

Zagreb, 2019

### Sveučilište u Zagrebu FAKULTET ELEKTROTEHNIKE I RAČUNARSTVA

Ivan Berdalović

# PROJEKTIRANJE CMOS SENZORA OTPORNIH NA ZRAČENJE ZA PRIMJENU U DETEKCIJI ČESTICA

DOKTORSKI RAD

Mentor: Prof. dr. sc. Tomislav Suligoj

Zagreb, 2019.

The doctoral thesis was done at the University of Zagreb, Faculty of Electrical Engineering and Computing, at the Department of electronics, microelectronics, computer and intelligent systems.

Supervisor: Professor Tomislav Suligoj, PhD

The doctoral thesis contains: 120 pages

Doctoral thesis no.:

#### About the Supervisor

Tomislav Suligoj received his Engineer Diploma, MSc and PhD degrees in electrical engineering from the University of Zagreb, Faculty of Electrical Engineering and Computing (FER), Croatia, in 1995, 1998 and 2001, respectively. Currently, he is a full professor at FER, Department of Electronics, Microelectronics, Computer and Intelligent Systems, teaching the courses in the area of electronics and microelectronics. He was a visiting researcher at the University of California, Los Angeles (1999-2001) and a postdoctoral researcher at the Hong Kong University of Science and Technology (2001-2002). He has been a Principal Investigator of more than 20 projects so far, supported by government agencies, international companies and universities. He has published 19 patents and more than 140 papers in journals and conference proceedings in the area of design, measurements and modelling of electron devices, micro- and nano- electronics, semiconductor technology and integrated circuit design. Prof. Suligoj has received 14 scientific awards including the National Science Award in 2015; the Golden plaque at the innovation exhibition ARCA; Best paper awards at the MIPRO MEET conference, Faculty medals "Josip Lončar" for outstanding Doctoral Dissertation, and a Fulbright scholarship. He is a Technical Program Committee member and a Chairman of Device Physics Subcommittee at IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM). He is a Steering Committee member of the MIPRO MEET conference. He was the President of the Electron Devices/Solid-State Circuits Joint Chapter, IEEE Croatia Section from 2010 until 2013. He gave numerous invited talks at conferences, universities, institutions and companies.

#### **O** mentoru

Tomislav Suligoj je diplomirao, magistrirao i doktorirao u polju elektrotehnike na Sveučilištu u Zagrebu, Fakultetu elektrotehnike i računarstva (FER), 1995., 1998. odnosno 2001. godine. Trenutno je redoviti profesor na Zavodu za elektroniku, mikroelektroniku, računalne i inteligentne sustave FER-a, gdje predaje kolegije u području elektronike i mikroelektronike. Bio je gostujući istraživač na University of California, Los Angeles od 1999. do 2001. godine te na poslijedoktorskom usavršavanju na Hong Kong University of Science and Technology od 2001. do 2002. Do sada je vodio više od 20 projekata financiranih od strane državnih institucija, međunarodnih kompanija i sveučilišta. Objavio je 19 patenata i više od 140 radova u časopisima i zbornicima konferencija u području projektiranja, mjerenja i modeliranja elektroničkih elemenata, mikro- i nano- elektronike, poluvodičke tehnologije i projektiranja integriranih sklopova. Prof. Suligoj dobitnik je 14 nagrada uključujući Državnu nagradu za znanost 2015. g., Zlatnu plaketu na izložbi inovacija ARCA, Best paper award na MIPRO MEET konferenciji, srebrnu plaketu "Josip Lončar" za posebno istaknutu doktorsku disertaciju te Fulbrightovu stipendiju. Član je Technical Program Committee i Chairman of Device Physics Subcommittee konferencije IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM). Član je Steering Committee konferencije MIPRO MEET. Bio je predsjednik Odjela za elektroničke elemente i poluvodičke integrirane sklopove Hrvatske sekcije IEEE 2010.-2013. Održao je velik broj pozvanih predavanja na međunarodnim konferencijama, sveučilištima, institutima i kompanijama.

### Acknowledgement

I would like to thank my supervisors at CERN, Dr. Heinz Pernegger and Dr. Walter Snoeys for their help and guidance throughout this PhD project. Working with you has been an honour and an experience I will never forget. I would also like to thank my supervisor at the University of Zagreb, Prof. Tomislav Suligoj for his support during the PhD and for letting me pursue the topics I was interested in, never pressuring me to do anything that was not in my best interest. Thanks to Thanushan Kugathasan, Cesar Augusto Marin Tobon, Enrico Junior Schioppa, Carlos Solans Sanchez and everyone else in the EP-ESE-ME and EP-ADE-ID groups who made this work possible. Special thanks to Valerio Dao, whose firmware and software expertise are responsible for a lot of the fancy plots included in this thesis. Thanks also to my office mates, Roberto Cardella, Francesco Piro and Leyre Flores for endless discussions on everything related to electronics and physics, especially during philosophical Fridays. Finally, thanks to my family, who have supported me every step of the way, even from a thousand kilometres away. You continue to provide inspiration and motivation for everything I want to do in life.

This research project has been supported by a Marie Skłodowska-Curie Innovative Training Network Fellowship of the European Commission's Horizon 2020 Programme under contract number 675587 STREAM.

#### Abstract

The work focuses on the design of large-scale radiation-hard monolithic CMOS sensors for the upgrades of the detectors in the high-energy physics experiments at CERN. The sensors are manufactured using a novel process modification implemented in the TowerJazz 180 nm CMOS process, which uses small collection electrodes to achieve a low sensor capacitance in the order of a few femtofarads, resulting in low noise and low analogue power consumption. The process modification provides full depletion of the sensitive layer and a radiation hardness promising to meet the requirements of the pixel detectors in CERN's largest experiments. The sensors implement a matrix of small pixels (in the order of 30 micrometres) containing a fast, low-noise front-end amplifier and a novel asynchronous digital readout architecture. Measurement results from these sensors before and after irradiation are also discussed.

**Keywords**: Active pixel sensors, CMOS integrated circuits, position sensitive particle detectors, radiation effects, radiation hardening (electronics), semiconductor detectors, solid-state circuit design

### Projektiranje CMOS senzora otpornih na zračenje za primjenu u detekciji čestica

Potraga za novim otkrićima u fizici čestica u Velikom hadronskom sudaraču (engl. Large Hadron Collider, LHC) u Europskoj organizaciji za nuklearna istraživanja (CERN) temelji se na detekciji čestica nastalih u sudarima protona ili teških iona. Protoni se kroz kompleks akceleratora ubrzavaju do energija od 6.5 TeV te se sudaraju u četiri najveća eksperimenta: ATLAS, CMS, ALICE i LHCb. Eksperimenti se sastoje od slojeva detektora koji su postavljeni u koncentričnim cilindrima oko točke sudara te služe za mjerenje naboja, količine gibanja i energije čestica nastalih u sudarima kao i čestica nastalih raspadom kratkoživućih čestica. U slučaju eksperimenta ATLAS, detektori se mogu podijeliti na nekoliko glavnih vrsta. Unutrašnji detektor (engl. Inner Detector, ID) sastoji se od silicijskih piksel i strip detektora visoke rezolucije položaja koji služe za precizno praćenje čestica blizu mjesta sudara. Pomoću njih se obavlja rekonstrukcija putanja čestica u magnetskom polju, gdje zakrivljenost putanje otkriva naboj i količinu gibanja čestica. Elektromagnetski i hadronski kalorimetri služe za mjerenje energije čestica, dok mionski spektrometar obavlja mjerenje količine gibanja miona koji prođu kroz sve ostale slojeve eksperimenta.

Budući da su zanimljivi fizikalni procesi (poput raspada Higgsova bozona) vrlo rijetki, LHC će između 2023. i 2025. biti podvrgnut nadogradnji koja će povećati broj sudara čestica u jedinici vremena za gotovo red veličine. Kako bi se mogli nositi s ovakvim porastom luminoziteta, nekolicinu sustava, uključujući i detektore, također će biti potrebno nadograditi. Veći broj čestica rezultirat će većim brojem detekcija u jedinici vremena, što bi moglo dovesti do smanjenja efikasnosti zbog ograničenja u brzini očitavanja podataka iz detektora. Dodatno ograničenje, osobito kod piksel detektora blizu mjesta sudara, su oštećenja uzrokovana ekstremnim količinama zračenja u tim sredinama tijekom čitavog vremena života detektora. Trenutno svi eksperimenti koriste tzv. hibridne piksel detektore za praćenje čestica u unutrašnjim slojevima. Kod ovakve vrste detektora, sam senzor je proizveden na zasebnoj pločici silicija, dok je elektronika za očitavanje proizvedena na drugoj pločici, obično u standardnom CMOS procesu, te je sa senzorom povezana malim vodljivim spojevima (engl. flip-chip bump-bonding). Senzor je zasebno optimiran za rad u uvjetima visoke razine zračenja, dok sklopovlje za očitavanje projektirano u tehnologiji malih dimenzija omogućuje visoku brzinu i sofisticirano procesiranje podataka.

Iako su zbog dobrih performansi hibridni detektori trenutno standard u detekciji čestica, jedan od glavnih nedostataka jest komplicirana i skupa tehnologija povezivanja dva čipa. Osim toga, disipacija snage i samim time zahtjevi za hlađenjem detektora su visoki, što rezultira velikom količinom materijala, koja pak ograničava rezoluciju količine gibanja zbog raspršenja čestica u materijalu. Zbog toga u novije vrijeme dolazi do razvoja monolitnih CMOS aktivnih piksel senzora (engl. CMOS monolithic active pixel sensors, MAPS), kod kojih su senzor i sklopovlje za očitavanje integrirani unutar jedne pločice silicija. To u potpunosti eliminira potrebu za povezivanjem čipova, što uz korištenje komercijalnih CMOS procesa znači da su cjenovno vrlo povoljni. Osim toga, kod ovih se detektora kapacitet senzora može dovesti do ekstremno niskih razina, što rezultira niskom potrošnjom snage u odnosu na hibridne detektore te smanjenjem količine materijala. Do nedavno, glavni nedostatak ove tehnologije bila je nedovoljna otpornost na zračenje. Međutim, razvojem CMOS senzorskih procesa, kao što je opisano i u ovom radu, dolazi do pojave monolitnih senzora s poboljšanom otpornošću na zračenje, što ih čini kandidatima čak i za najzahtjevnije primjene. Monolitni CMOS senzori u ovom radu projektirani su s ciljem zadovoljavanja zahtjeva za vanjske slojeve piksel detektora u eksperimentu ATLAS nakon nadogradnje LHC-a. Neki od najvažnijih zahtjeva su efikasnost detekecije od preko 97%, vremenska rezolucija od 25 ns, koliko iznosi vrijeme između sudara dva snopa protona, i to uz potrošnju snage ispod 500 mW/cm<sup>2</sup>. Zahtjevi moraju biti zadovoljeni nakon što su detektori podvrgnuti dozi od 10<sup>15</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup> neionizirajućeg zračenja te 50 Mrad ionizirućeg zračenja tijekom čitavog vremena života u eksperimentu.

Osnovni mehanizam za detekciju čestica u siliciju jest stvaranje parova elektron-šupljina u zaporno polariziranom p-n spoju. Broj ioniziranih nosilaca ovisi o gubitku energije čestice koja prolazi kroz materijal, a koji ovisi o vrsti i samoj energiji čestice. Jedan tip ioniziranih nosilaca sakuplja se na jednoj elektrodi p-n spoja. Naboj generiran unutar osiromašenog područja brzo se sakuplja driftom, a ako senzor nije potpuno osiromašen, i difuzija iz kvazineutralnih područja sudjeluje u procesu sakupljanja naboja. Osim ionizacije parova elektron-šupljina, visokoenergetske čestice mogu izbiti jezgre silicija iz položaja u kristalnoj rešetci, što dovodi do stvaranja defekata u kristalu. To rezultira pojavom energetskih nivoa unutar zabranjenog pojasa (tzv. zamki) koji mogu zarobiti ionizirane nosioce naboja i dovesti do gubitka signala. Kako vjerojatnost zarobljavanja nosilaca ovisi o vremenu sakupljanja naboja, glavna strategija za postizanje otpornosti na ovo neionizirajuće zračenje (engl. non-ionising energy loss, NIEL) jest sakupljati naboj driftom i tako smanjiti vrijeme sakupljanja i vjerojatnost zarobljavanja.

Dva su glavna pristupa u izvedbi sakupljačke elektrode u monolitnim piksel detektorima, i to izvedba s malom sakupljačkom elektrodom, gdje elektroda zauzima tek mali dio piksela, a elektronika za očitavanje nalazi se odvojeno od elektrode, te izvedba s velikom sakupljačkom elektrodom, gdje elektroda zauzima većinu površine piksela, a sklopovlje je smješteno unutar elektrode. Prednost male elektrode je izuzetno nizak kapacitet senzora (reda veličine neko-liko femtofarada), što je povoljno za razinu šuma i disipaciju snage analognih sklopova koji slijede. Međutim, nedostatak male elektrode jest činjenica da je teško postići potpuno osiromašenje sloja za detekciju i samim time zadovoljavajuću otpornost na zračenje. Za potpuno osiromašenje i sakupljanje driftom stoga je povoljnije koristiti piksele s velikom elektrodom, koja međutim znači znatno veći ulazni kapacitet i veće preslušavanje iz digitalnih sklopova za očitavanje prema sakupljačkoj elektrodi.

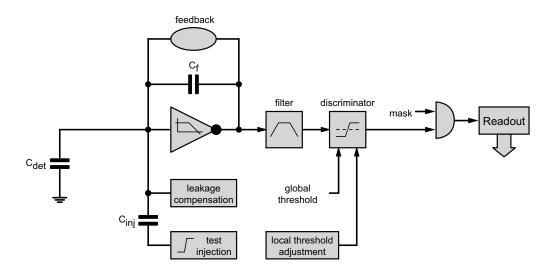

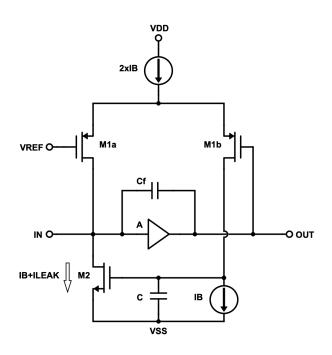

Kako su sakupljeni naboji relativno mali (reda veličine nekoliko femtokulona), signale s elektrode potrebno je pojačati, što se standardno radi pojačalom osjetljivim na naboj s kapacitivnom povratnom vezom unutar piksela. Važno je da pojačalo ima visoko pojačanje te nizak šum, uz visoku brzinu odziva. Nakon pojačala obično slijedi filtar za suzbijanje nisko- i visokofrekventnih komponenti šuma te komparator, koji osigurava da se očitavaju samo signali iznad određenog praga detekcije. Digitalna arhitektura za očitavanje koja slijedi nakon komparatora vrši dodatno procesiranje signala komparatora te mora do izlaza čipa dovesti točnu adresu piksela unutar dvodimenzionalne matrice u kojima je obavljena detekcija, a u nekim primjenama i informaciju o amplitudi detektiranog signala.

Treba napomenuti da zračenje utječe i na sklopovlje za pojačanje i očitavanje. U ovom slučaju, ionizirajuće zračenje (engl. total ionising dose, TID) uzrokuje nakupljanje pozitivnog naboja u silicijevom dioksidu upravljačke elektrode ili u izolacijskom oksidu tranzistora. Naboj na upravljačkoj elektrodi dovodi do promjena u naponu praga tranzistora, dok naboj u izolacijskom oksidu može dovesti do porasta struje curenja između uvoda i odvoda NMOS tranzistora. Ovi se efekti najčešće sprječavaju primjenom tranzistora s kružnom upravljačkom elektrodom (engl. enclosed layout transistors, ELT), čime se osigurava da sva struja teče ispod upravljačke elektrode.

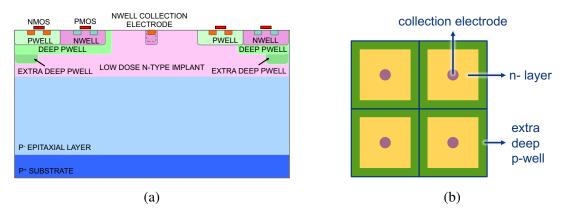

Monolitni CMOS senzori projektirani u ovom radu proizvedeni su u TowerJazz 180 nm CMOS procesu. Ova tehnologija koristi male sakupljačke elektrode n-tipa. Sklopovlje je odvojeno od elektrode i zaštićeno dubokom implantacijom p-tipa kako podloga PMOS tranzistora ne bi sudjelovala u sakupljanju signalnog naboja. Epitaksijalni sloj p-tipa debljine 25-30 µm koristi se kao sloj za detekciju. Visoka otpornost tog sloja pomaže osiromašenju oko sakupljačke elektrode, no da bi se postiglo potpuno osiromašenje epitaksijalnog sloja i zadovoljavajuća otpornost na neionizirajuće zračenje, potrebna je modifikacija procesa dodavanjem niskodopiranog sloja n-tipa preko cijele matrice piksela. Nakon dobrih rezultata na prototipima senzora u ovom modificiranom procesu, započinje projektiranje velikih detektora koji bi zadovoljili specifikacije eksperimenta ATLAS.

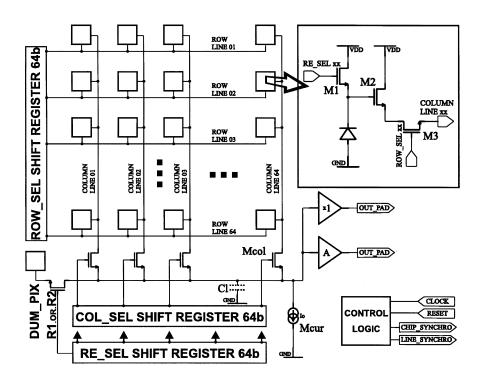

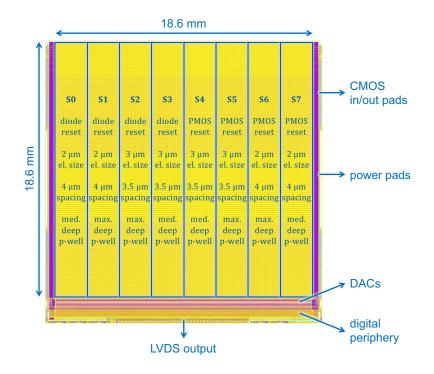

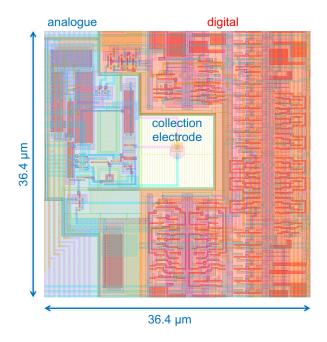

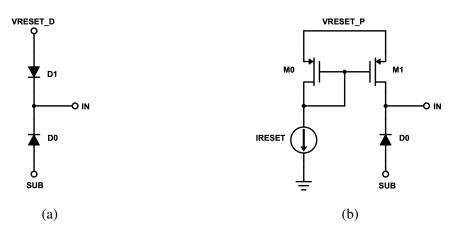

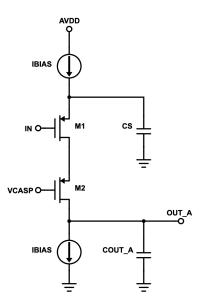

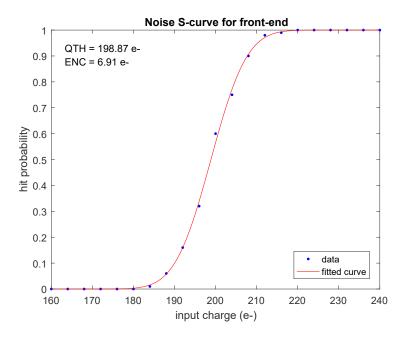

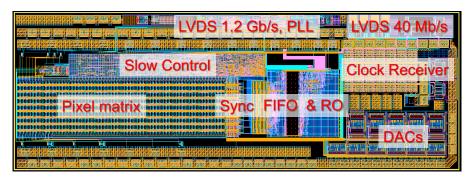

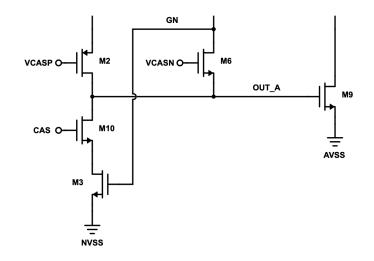

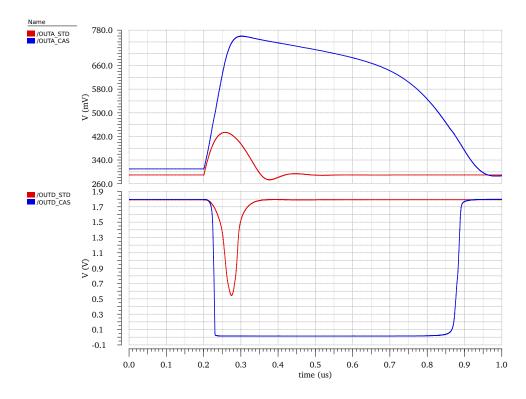

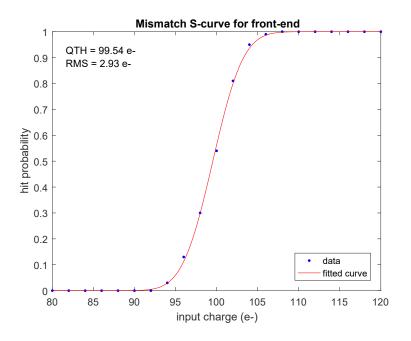

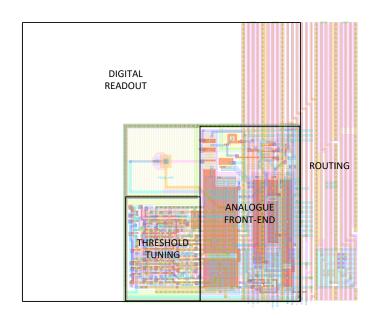

MALTA (engl. Monolithic from ALICE To ATLAS) je senzor koji sadrži matricu od  $512 \times 512$  piksela veličine  $36.4 \times 36.4 \ \mu m^2$ . Svaki piksel osim male sakupljačke elektrode promjera 2-3  $\mu$ m sadrži analogni dio sklopovlja, koji se sastoji od ulaznog pojačala i komparatora, te digitalnu logiku za očitavanje adrese piksela. Ulazno pojačalo temelji se na uvodskom sljedilu koje sakupljeni naboj prenosi s velikog kapaciteta na mali parazitni kapacitet, pri čemu dolazi do visokog naponskog pojačanja. Vrijeme odziva ovisi o sakupljenom naboju, a jedan od glavnih zahtjeva je osigurati dovoljno kratko vrijeme odziva kako bi se svaka detekcija mogla obaviti unutar 25 ns, što je ovom topologijom moguće postići uz disipaciju snage manju od 1  $\mu$ W po pikselu. Pojačalo je optimirano za prag detekcije od 200 e<sup>-</sup>, a pri tome u tranzijentnim simulacijama šuma pokazuje ukupni ekvivalentni šum na ulazu od tek 7 e<sup>-</sup>. Dimenzije tranzistora

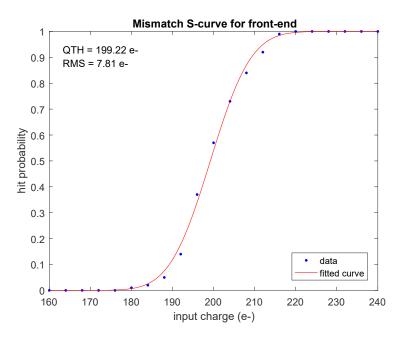

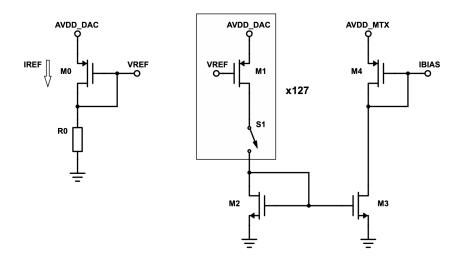

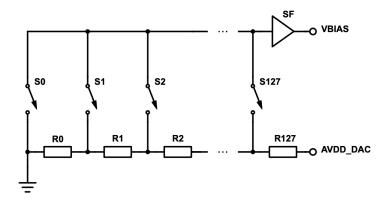

optimirane su i na način da procesne varijacije što manje utječu na rasipanje praga detekcije, te Monte Carlo simulacije pokazuju standardnu devijaciju praga detekcije od samo 8 e<sup>-</sup>. Struje i naponi potrebni za rad pojačala generiraju se pomoću digitalno-analognih pretvornika, a kritični tranzistori u pojačalu i pretvornicima izvedeni su u topologiji s kružnom upravljačkom elektrodom radi otpornosti na ionizirajuće zračenje.

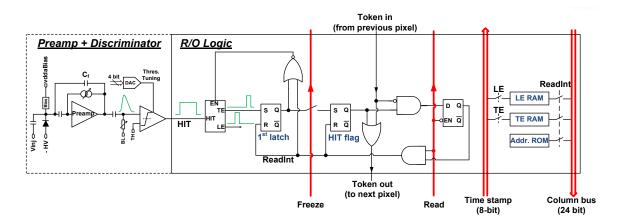

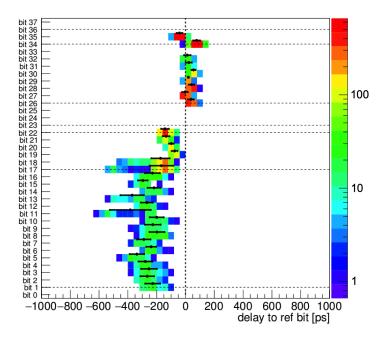

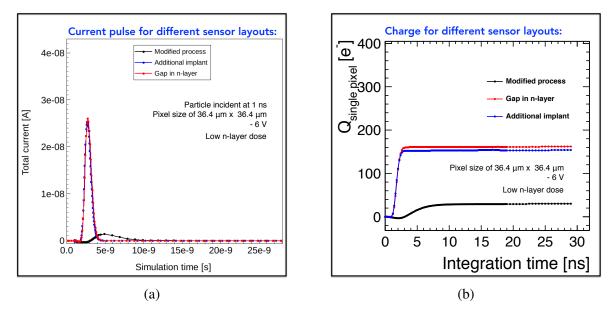

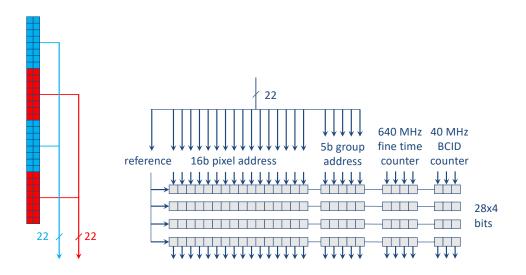

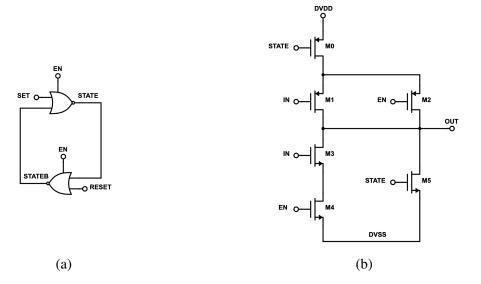

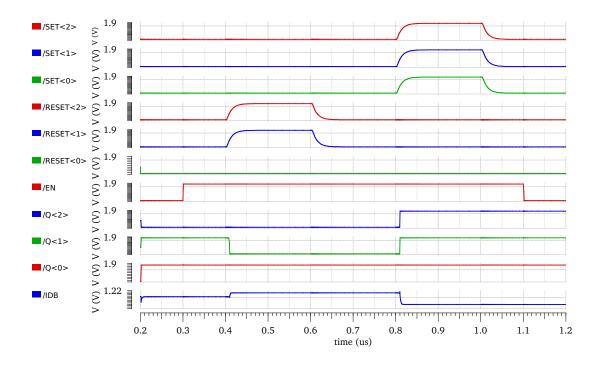

Digitalna elektronika za očitavanje koristi novi, asinkroni način prijenosa podataka unutar matrice piksela. Digitalni impulsi na izlazu komparatora koriste se u generiranju 22-bitnog uzorka kratkih impulsa trajanja do 2 ns, koji se asinkrono šalje niz stupac piksela i sadrži kodiranu adresu piksela u kojem je obavljena detekcija unutar stupca. Prednost asinkronog pristupa je činjenica da nema signala takta unutar velike matrice, što značajno smanjuje digitalnu potrošnju snage, a pritom omogućuje veći broj detekcija u jedinici vremena. Na periferiji čipa, signali iz svih stupaca spajaju se u jednu riječ od 40 bita, koja jednoznačno određuje adresu piksela unutar matrice, te se riječ sa izlaza čipa LVDS standardom šalje do vanjskih sustava za pohranu podataka. Zbog asinkronog prijenosa potrebno je voditi računa o tome da svi signali unutar riječi stignu do izlaza čipa u isto vrijeme, što znači da kapaciteti linija svih bitova u cijelom lancu prijenosa moraju biti potpuno izjednačeni.

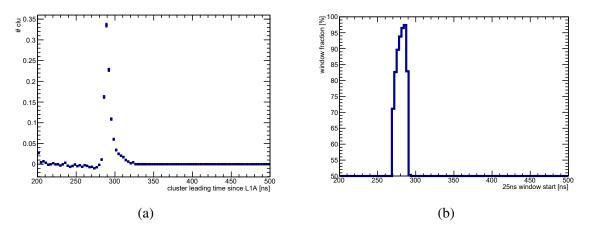

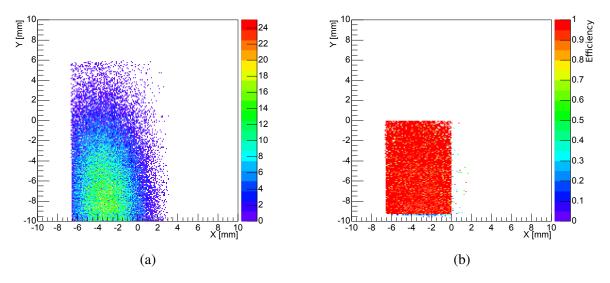

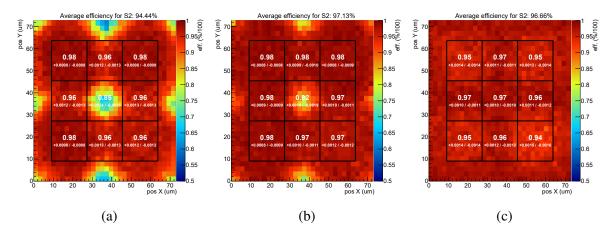

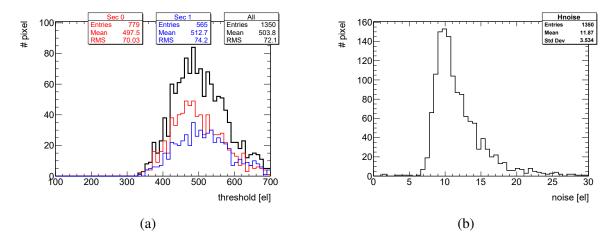

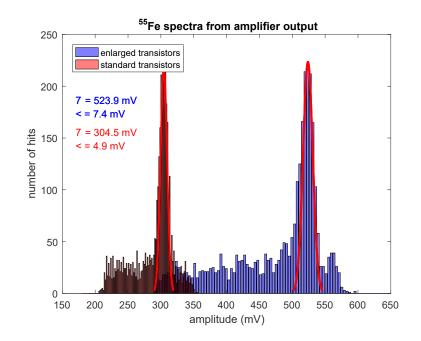

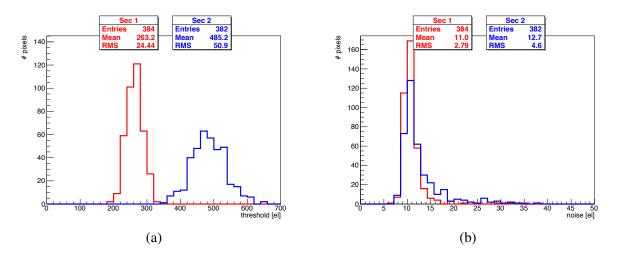

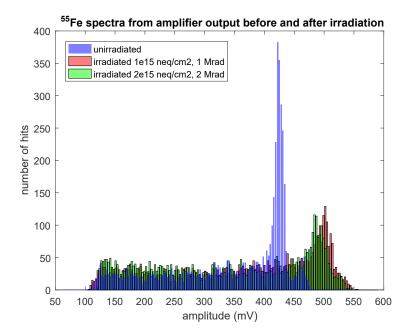

Proizvedeni MALTA senzori okarakterizirani su u laboratoriju i u testiranjima zrakom čestica. Pokazuje se da su analogni ulazni sklopovi potpuno funkcionalni te da vremenski odziv odgovara simuliranim vrijednostima. Uz dovoljno nizak prag detekcije, preko 98% signala detektira se unutar 25 ns, čak i bez korekcije za trajanje propagacije impulsa niz stupac piksela od 8 ns. Srednja vrijednost ekvivalentnog šuma ulaznog pojačala također odgovara simulacijama, no primjećeno je da raspodjela šuma ne odgovara Gaussovoj raspodjeli, što se dovodi u vezu s malim dimenzijama pojedinih tranzistora u pojačalu i time uzrokovanog porasta šuma (engl. random telegraph signal noise, RTS) u pojedinim pikselima. Osim toga, rasipanje praga detekcije unutar matrice je znatno veće od simuliranih vrijednosti, što u kombinaciji s RTS šumom ograničava prag detekcije na iznad 200 e<sup>-</sup>. U testiranjima zrakom čestica zaključuje se da uz najniže moguće pragove detekcije senzor prije zračenja postiže visoku efikasnost detekcije od preko 97%, uniformnu po cijeloj površini piksela.

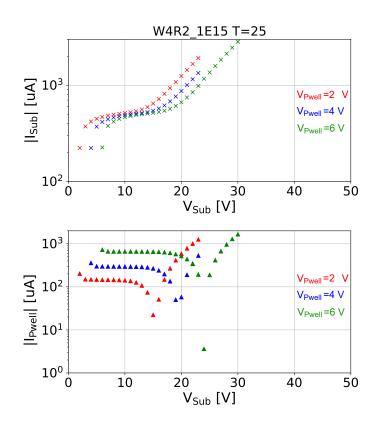

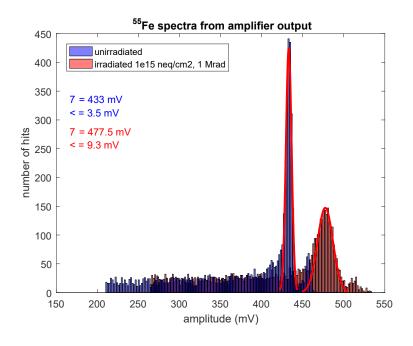

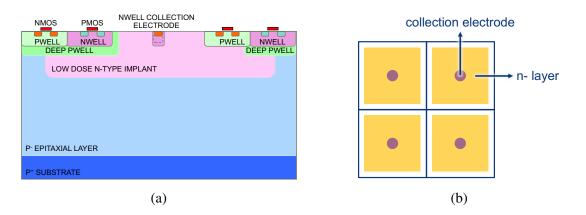

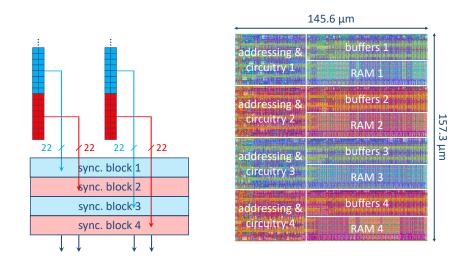

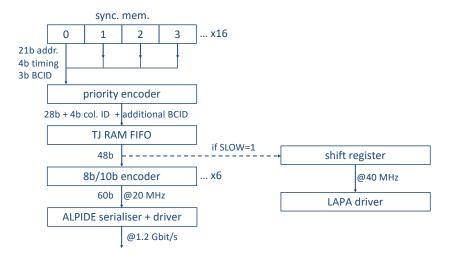

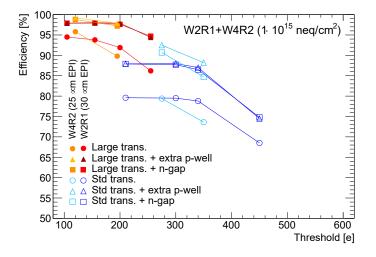

Nakon ozračenja neutronima do  $10^{15} n_{eq}/cm^2$  i x-zrakama do 70 Mrad, analogni i digitalni sklopovi su i dalje funkcionalni, uz nešto veći šum i rasipanje praga detekcije. Pojačanje ulaznog sklopa ne razlikuje se od onog prije zračenja zahvaljujući topologiji otpornoj na ionizirajuće zračenje. Međutim, testiranja zrakom čestica pokazuju znatan pad efikasnosti detekcije pri rubovima piksela, daleko od sakupljačke elektrode. Iako je senzor u modificiranom procesu potpuno osiromašen, gubitak efikasnosti povezan je s manjkom lateralnog električnog polja pri rubovima piksela, što dovodi do zarobljavanja nosilaca u zamkama uzrokovanim neionizirajućim zračenjem i do gubitka signala. Zbog toga maksimalna srednja efikasnost unutar piksela uz najniže dostižne pragove detekcije iznosi tek oko 80%. Kako bi se poboljšala efikasnost detekcije nakon zračenja, pomoću TCAD simulacija razvijene su nove procesne promjene s ciljem povećanja lateralnog električnog polja. Pokazuje se da se uvođenjem dodatne duboke implantacije p-tipa ili uvođenjem razmaka u postojeću implantaciju n-tipa pri rubovima piksela električno polje te samim time nosioci bolje usmjeravaju prema sakupljačkoj elektrodi, te da je ukupni sakupljeni naboj nakon zračenja znatno veći. Zbog toga započinje projektiranje nove, manje verzije MALTA čipa s ovim procesnim promjenama, nazvane miniMALTA. Osim procesnih promjena, unutar matrice piksela povećane su dimenzije kritičnih tranzistora kako bi se suzbio RTS šum i dobilo veće pojačanje. Na periferiji čipa projektirana je i nova generacija digitalnog sklopovlja za očitavanje, koja sinkronizira asinkrone signale iz matrice i olakšava daljnje procesiranje podataka, zadržavajući pritom nisku digitalnu potrošnju snage. Sklop za sinkronizaciju temelji se na polju RAM memorijskih ćelija u koje se pohranjuje informacija o adresi piksela i vremenu detekcije. RAM memorija se zatim sinkrono očitava te se informacija sinkrono šalje s čipa.

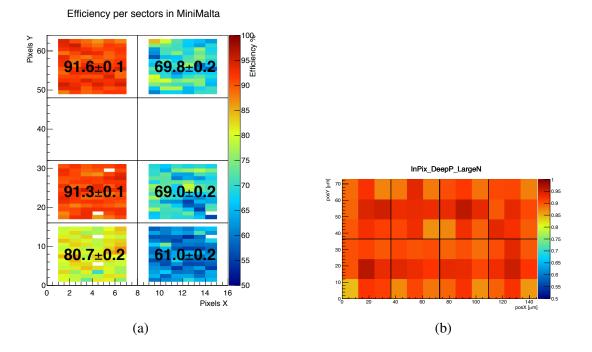

Prvi rezultati mjerenja na ulaznom pojačalu novog miniMALTA čipa pokazuju znatno veće pojačanje zbog većeg izlaznog otpora na izlaznom čvoru pojačala, što znači da se uz iste postavke pojačala mogu postići niži pragovi detekcije. Osim toga, povećanje dimenzija tranzistora gotovo u potpunosti eliminira RTS šum čak i nakon ozračenja, što ponovno znači da je lakše postići niže pragove. Sklopovlje za sinkronizaciju također se pokazalo potpuno funkcionalnim te je moguće očitati točnu adresnu i vremensku informaciju pri svakoj detekciji. U testiranjima zrakom čestica prije zračenja, sektori čipa u kojima su implementirane procesne promjene uz niski prag detekcije od ispod 200 e<sup>-</sup> pokazuju efikasnost od preko 99%. Nakon ozračenja do  $10^{15} n_{eq}/cm^2$ , efikasnost u tim sektorima još uvijek iznosi oko 98%, što znači da povećanje lateralnog električnog polja uz niski prag detekcije dovodi to gotovo potpune efikasnosti detekcije čak i nakon zahtijevanih doza zračenja.

Nakon ovih rezultata, nastavlja se projektiranje sljedećih verzija velikih detektora u Tower-Jazz 180 nm tehnologiji. Dodatna poboljšanja ulaznih sklopova omogućit će još veće pojačanje i niži prag detekcije, a unutar svakog piksela dodano je i sklopovlje za podešavanje praga detekcije, čime će se smanjiti rasipanje praga unutar velike matrice. Uz smanjenje dimenzija piksela na oko 33 µm, to bi trebalo dovesti do još više efikasnosti i još bolje otpornosti na zračenje. Poboljšanja će biti uključena u dva velika detektora s različitim vrstama digitalnih sklopova za očitavanje, koji će biti poslani na proizvodnju krajem 2019.

**Ključne riječi**: Aktivni piksel senzori, CMOS integrirani sklopovi, detektori čestica osjetljivi na položaj, efekti zračenja, otpornost (elektronike) na zračenje, poluvodički detektori, projektiranje poluvodičkih sklopova

# Contents

| 1. | Intro | oductio | <b>n</b>                                                                      | 1  |

|----|-------|---------|-------------------------------------------------------------------------------|----|

|    | 1.1.  | Detect  | ors in the high-energy physics experiments at CERN                            | 1  |

|    | 1.2.  | Pixel d | letectors for the LHC High-Luminosity upgrade                                 | 6  |

| 2. | CM    | OS mon  | olithic active pixel sensors                                                  | 10 |

|    | 2.1.  | Detect  | ion of particles in silicon                                                   | 10 |

|    |       | 2.1.1.  | Energy loss of charged particles                                              | 10 |

|    |       | 2.1.2.  | Signal formation in the sensor                                                | 13 |

|    | 2.2.  | Radiat  | ion effects in the sensor – Non-ionising energy loss                          | 16 |

|    | 2.3.  | Monol   | ithic sensor concepts                                                         | 19 |

|    |       | 2.3.1.  | Small collection electrode designs                                            | 19 |

|    |       | 2.3.2.  | Large collection electrode designs                                            | 21 |

|    |       | 2.3.3.  | Other approaches - DEPFET and SOI                                             | 22 |

|    | 2.4.  | Radiat  | ion effects in the electronics – Total ionising dose and single event effects | 22 |

|    | 2.5.  | Front-e | end and readout concepts                                                      | 25 |

| 3. | Desi  | gn and  | characterisation of radiation-hard CMOS sensors                               | 30 |

|    | 3.1.  | Sensor  | technology                                                                    | 30 |

|    |       | 3.1.1.  | The standard TowerJazz 180 nm process                                         | 30 |

|    |       | 3.1.2.  | Designs in the modified TowerJazz process                                     | 31 |

|    | 3.2.  | Analog  | gue front-end circuit                                                         | 36 |

|    |       | 3.2.1.  | Principle of operation                                                        | 36 |

|    |       | 3.2.2.  | Timing optimisation                                                           | 40 |

|    |       | 3.2.3.  | Noise and mismatch                                                            | 43 |

|    |       | 3.2.4.  | Considerations for radiation hardness                                         | 46 |

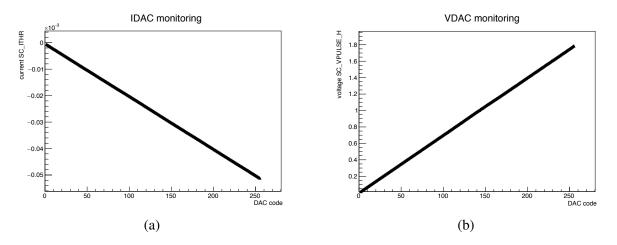

|    |       | 3.2.5.  | Bias generation using digital-to-analogue converters                          | 46 |

|    | 3.3.  | Digital | readout electronics                                                           | 49 |

|    |       | 3.3.1.  | Asynchronous matrix readout                                                   | 49 |

|    |       | 3.3.2.  | End-of-column readout logic                                                   | 54 |

|    | 3.4.   | characterisation before irradiation | 57                                             |     |

|----|--------|-------------------------------------|------------------------------------------------|-----|

|    |        | 3.4.1.                              | Sensor and analogue performance in lab tests   | 57  |

|    |        | 3.4.2.                              | Measurements on readout architecture           | 62  |

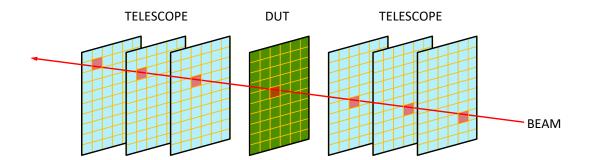

|    |        | 3.4.3.                              | Beam test results                              | 68  |

|    | 3.5.   | Perform                             | nance of irradiated sensors                    | 70  |

|    |        | 3.5.1.                              | Sensor and front-end after irradiation         | 70  |

|    |        | 3.5.2.                              | Efficiency in beam tests                       | 74  |

| 4. | Opti   | imisatio                            | n of pixel matrix and readout electronics      | 78  |

|    | 4.1.   | Proces                              | s improvements for radiation hardness          | 78  |

|    | 4.2.   | Pixel n                             | natrix design changes                          | 80  |

|    | 4.3.   | Synchr                              | onisation at the end-of-column                 | 81  |

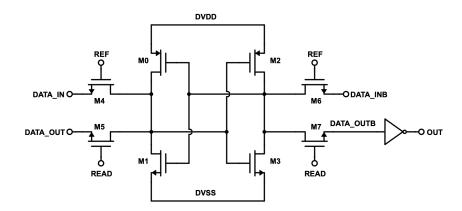

|    |        | 4.3.1.                              | Random-access memory for synchronisation       | 81  |

|    |        | 4.3.2.                              | Peripheral readout logic                       | 83  |

|    | 4.4.   | Test re                             | sults before and after irradiation             | 85  |

| 5. | Outl   | look for                            | future design improvements                     | 100 |

|    | 5.1.   | Further                             | r optimisation of analogue front-end circuitry | 100 |

|    | 5.2.   | In-pixe                             | el threshold tuning                            | 103 |

| 6. | Con    | clusion                             |                                                | 107 |

| Bi | bliogr | aphy .                              |                                                | 109 |

| Bi | ograp  | <b>hy</b>                           |                                                | 117 |

| Ži | votop  | is                                  |                                                | 120 |

# Chapter 1

# Introduction

#### **1.1** Detectors in the high-energy physics experiments at CERN

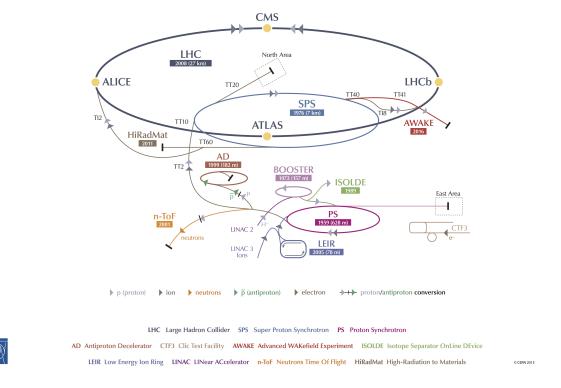

The search for new physics at the Large Hadron Collider (LHC) at the European Organisation for Nuclear Research (CERN) relies on the detection of particles created in proton-proton and heavy ion collisions. Protons in two counter-rotating beams are accelerated through a complex of accelerators, shown in fig. 1.1 [1], reaching a beam energy of up to 6.5 TeV in the largest collider ring, the 27 km circumference LHC. Protons are produced by ionising hydrogen gas with an electric field. The kinetic energy of the protons is increased from about 100 keV up to 1.4 GeV in a linear accelerator (LINAC) using radio-frequency cavities and the Proton Synchrotron Booster (PSB) before being injected into the Proton Synchrotron (PS). The PS and the SPS (Super Proton Synchrotron) accelerate the protons to 25 GeV and 450 GeV, respectively, before the beams are finally injected into the LHC for further acceleration, from 450 GeV to 6.5 TeV per beam.

Superconducting magnets cooled to temperatures below 2 K and operating at magnetic field strengths above 8 T are used to bend the particles in the beam around the circular collider. The beams collide at four crossing points around which the four largest experiments, ATLAS [2], CMS [3], ALICE [4] and LHCb [5] are positioned. The number of events per second generated in the LHC collisions is given by:

$$N = L\sigma, \tag{1.1}$$

where  $\sigma$  is the cross-section for the event in question and *L* is the machine luminosity. *L* is defined only by the beam parameters and can be written as:

$$L = \frac{N_b^2 n_b f_{rev} \gamma_r}{4\pi \varepsilon_n \beta_*} F,$$

(1.2)

where  $N_b$  is the number of particles per bunch,  $n_b$  the number of bunches per beam,  $f_{rev}$  the

#### **CERN's Accelerator Complex**

**Figure 1.1:** An overview of the accelerator complex at CERN and the experiments within it (reproduced from [1]).

revolution frequency,  $\gamma_r$  the relativistic gamma factor,  $\varepsilon_n$  the normalised transverse beam emittance,  $b_*$  the beta function at the collision point, and F the geometric luminosity reduction factor due to the crossing angle at the interaction point [6]. Since the interesting physics events (such as decays of the elusive Higgs boson) are very rare, the study and exploration of these events in the LHC collisions requires both high beam energies and high beam intensities. The two largest general-purpose experiments, ATLAS and CMS, operate with a peak luminosity of about  $L = 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> for proton collisions, while the one dedicated ion experiment, ALICE, aims at a peak luminosity of  $L = 10^{27}$  cm<sup>-2</sup>s<sup>-1</sup> for nominal lead-lead ion operation. Rather than having continuous beams, the protons are bunched together so that interactions between the two beams take place at discrete intervals, 25 ns apart, providing a bunch collision rate of 40 MHz. The particles created in these collisions as well as the decay products of particles with a short lifetime pass through a variety of detectors within the experiments, which provide information about the charge, momentum and energy of the created particles.

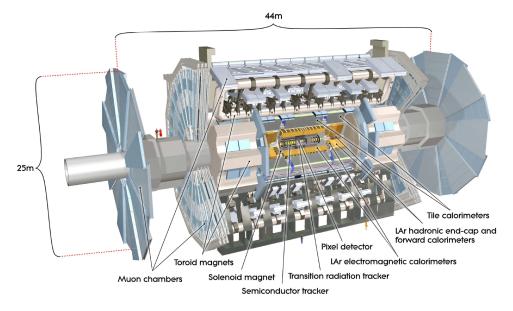

An overview of the detector systems will be given through the example of the ATLAS experiment, illustrated in fig. 1.2. The experiment consists of a series of detectors placed in concentric cylinders around the interaction point where the proton beams from the LHC collide. It can be divided into four major parts: the Inner Detector, the calorimeters, the Muon

Spectrometer and the magnet systems [7]. The two large superconducting magnet systems are used to bend charged particles so that their momenta can be measured. The inner solenoid magnet produces a uniform 2 T magnetic field surrounding the Inner Detector, while the outer toroidal magnetic field surrounds the calorimeters and the muon system.

Figure 1.2: A cut-away view of the ATLAS experiment and its sub-parts (reproduced from [2]).

The Inner Detector itself consists of high-resolution semiconductor pixel and strip detectors in the inner part of the tracking volume, as well as straw-tube tracking detectors with the capability to generate and detect transition radiation in its outer part. The innermost pixel layer begins about 5 cm from the proton beam axis, and the Inner Detector extends to a radius of 1.2 metres as well as 6.2 metres in length along the beam pipe. Its basic function is to track charged particles by detecting their interaction with material at discrete points. The curvature of the particles' track due to the magnetic field present reveals the charge and momentum of the particles. Apart from track reconstruction, the precision tracking detectors, i.e. the pixels and semiconductor trackers (SCT), need to be able to reconstruct the interaction point of the particles from the beam (primary vertices) as well as the decay points of short-lived particles (secondary vertices) with a high resolution. This is achieved by a high granularity in the two-dimensionally segmented silicon pixel detectors used around the vertex region. The high granularity in the order 100 µm over such a large area means that the number of readout channels in the Pixel Detector itself is very high, over 80 million, which is about 50% of the total readout channels of the whole experiment. The total of nearly 1750 pixel modules are arranged in three layers around the beam axis in the barrel region and on three disks perpendicular to the beam axis in the end-cap regions. The pixels in the barrel region provide a spatial resolution of around 10  $\mu$ m in the direction radial to the beam axis and 70  $\mu$ m in the direction along the beam axis for the impact parameter, as well as around 50 µm in the radial direction for the reconstruction of secondary vertices. The impact parameter is defined as the perpendicular distance of the closest approach of a reconstructed track to the primary vertex.

The Semiconductor Tracker (SCT) is the middle component of the Inner Detector and has a similar function to the Pixel Detector, but with long, narrow strips rather than small pixels, making coverage of a larger area more practical. The SCT is critical for the tracking in the plane perpendicular to the beam, since it measures particles over a much larger area than the Pixel Detector, with more sampled points and similar, albeit one-dimensional accuracy. The total number of readout channels in the SCT is approximately 6.3 million. The Transition Radiation Tracker (TRT) is the outermost component of the Inner Detector and is composed of drift tubes (straws), each 4 mm in diameter and up to 144 cm long. The TRT only provides information about the radial position, for which it has an intrinsic accuracy of 130 µm per straw. Each straw is filled with gas that becomes ionised when a charged particle passes through, producing a current pulse in the wire. The pattern of "hit" straws allow the path of the particle to be determined. Ultra-relativistic charged particles produce transition radiation in the material between the straws, resulting in a much stronger signals in some straws and allowing the identification of the lightest charged particles, electrons and positrons. The total number of TRT readout channels is approximately 351 thousand. The expected transverse momentum resolution obtained with the complete Inner Detector is [8]:

$$\frac{\sigma_{pT}}{p_T} = 0.03\% p_T \text{ (GeV)} + 1.2\%.$$

(1.3)

The calorimeters are situated outside the solenoidal magnet that surrounds the Inner Detector. Their purpose is to measure the energy of particles by absorbing it. There are two basic calorimeter systems: an inner Electromagnetic Calorimeter and an outer Hadronic Calorimeter. Both are sampling calorimeters: they absorb energy in high-density metal and periodically sample the shape of the resulting particle shower, inferring the energy of the original particle from this measurement. The Electromagnetic (EM) Calorimeter absorbs energy from particles that interact electromagnetically, and its fine granularity and energy resolution are ideally suited for precision measurements on electrons and photons. The energy-absorbing materials are lead and steel, while liquid argon (LAr) is used as the sampling material. The Hadron Calorimeter absorbs energy from particles that pass through the EM Calorimeter, primarily hadrons. The main part of this calorimeter is the tile calorimeter placed directly outside the EM calorimeter envelope. The energy-absorbing material is steel, with scintillating tiles that sample the energy deposited. The coarser granularity of this part of the calorimeter is sufficient to satisfy the physics requirements. In the end-cap regions, the end-cap and forward calorimeters made of liquid argon, copper and tungsten complete the calorimeter system.

The Muon Spectrometer is a large tracking system designed to accurately measure the momentum of muons, which pass through all the other elements of the detector before reaching the muon systems. It is based on the magnetic deflection of muon tracks in the large superconducting air-core toroid magnets, instrumented with separate high-precision tracking chambers and triggering chambers with a high time resolution. The precise measurement of the track coordinates in the principal bending direction of the magnetic field is provided by Monitored Drift Tubes (MDTs) and Cathode Strip Chamber (CSCs). The trigger chambers, made of Resistive Plate Chambers (RPCs) and Thin Gap Chambers (TGCs) provide bunch-crossing identification and measure the muon coordinate in the direction orthogonal to that determined by the precision-tracking chambers. In the barrel region, tracks are measured in chambers arranged in three cylindrical layers around the beam axis; in the transition and end-cap regions, the chambers are installed in planes perpendicular to the beam, also in three layers.

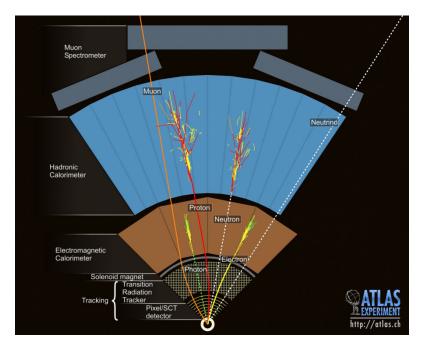

The principle of detecting different types of particles in the experiment is reiterated in fig. 1.3. Charged particles are tracked precisely within the Pixel/SCT Detectors and Transition Radiation Tracker of the Inner Detector and then absorbed in either the Electromagnetic or the Hadronic Calorimeter for energy measurement. Muons, which pass through all the other detector systems, are tracked in the Muon Spectrometer. Neutrinos are the only established stable particles that cannot be detected directly, and their presence is inferred by measuring a momentum imbalance among detected particles.

Figure 1.3: A cross-section through the various layers of detectors used in the ATLAS experiment.

The other large general-purpose detector, CMS, uses the same principles in particle detection, and is composed of an all-silicon tracker, an electromagnetic and hadronic calorimeter as well as a muon system. The principal difference between the two experiments is the magnet system, where CMS uses a single solenoid to generate the 4 T magnetic field penetrating all the detector layers.

#### **1.2** Pixel detectors for the LHC High-Luminosity upgrade

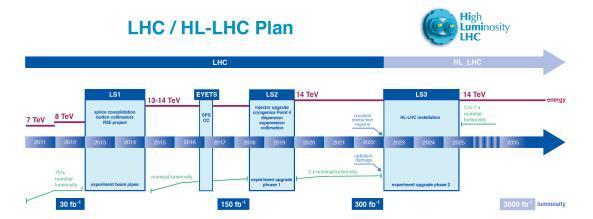

After 2020, the statistical gain in running the accelerator without a significant luminosity increase beyond its design value will become marginal. Therefore, to maintain scientific progress and to explore its full capacity, the LHC will undergo a major upgrade during the long shutdown planned between 2023 and 2025 [9]. The timeline of the upgrade plans is shown in fig. 1.4. After 2025, the peak luminosity will be increased to more than  $5 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, which is a factor of 5-7 higher than the current design value. When integrating the luminosity over the full operation time of the machine, this gives an integrated luminosity value of 3000 fb<sup>-1</sup> that can be reached until 2035. This integrated luminosity is about ten times the expected luminosity reach of the first twelve years of the LHC lifetime. To cope with such an increase in luminosity, a number of systems related to the superconducting magnets, cryogenics and beam collimation will need to be upgraded. A number of detector systems will need to be upgraded as well, since the increased particle fluxes will result in higher detector occupancies and efficiency losses due to readout limitations at high hit rates. Another limitation is the increase in radiation damage over the full lifetime of the detectors, especially in the pixel detectors closest to the particle interaction points.

**Figure 1.4:** Timeline of the upgrade plans for the LHC. After the third long shut-down (LS3), the machine will be in the High-Luminosity configuration (reproduced from [9]).

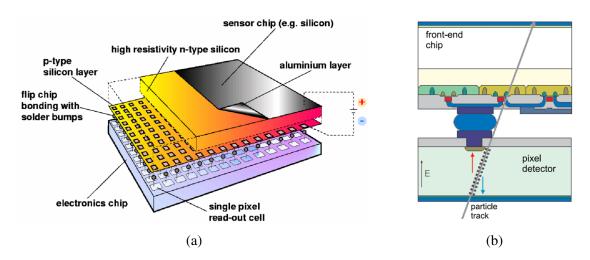

The three-layer pixel system of the ATLAS detector, designed for an instantaneous luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, was already upgraded during the long shut-down in 2013-2014 (LS1) to cope with the gradually increasing luminosity until the LS3 upgrade. In order to retain the excellent secondary vertex reconstruction efficiency in the presence of high pile-up, a fourth pixel detector layer, called the Insertable B-Layer (IBL), was installed inside the three-layer pixel detector, about 3.3 cm from the beam line. As a result, the impact parameter resolution improved by nearly a factor of 2 for low transverse momentum tracks [10]. For the high-luminosity upgrade during LS3, the Inner Detector will be replaced by an all-silicon Inner Tracker (ITk) consisting of five layers of pixel and four layers of strip detectors [11]. Currently, all the experiments at the LHC use hybrid pixel detectors for the tracking of particles in the innermost layers. In this type of detector, the sensor part is produced on dedicated sensor grade silicon material, while the separate pixel readout chip is manufactured using a standard CMOS process. The traversing particle generates a signal in the sensor part, which is read out by the readout chip attached to the sensor by using the flip-chip bump-bonding technology. The readout cells are arranged in the same two-dimensional matrix structure of the pixel cells of the sensor, as shown in fig. 1.5a. A pixel unit cell of the sensor part together with the readout cell and the connecting solder bump is shown in fig. 1.5b.

**Figure 1.5:** (a) A cut-away view and (b) one pixel cell of a hybrid pixel detector. The sensor chip is bump-bonded to the readout chip containing the electronics (reproduced from [12] and [13]).

The large signals collected from the sensor chip optimised for a high-radiation environment combined with the sophisticated analogue and digital functionality provided by the readout chip designed in technologies with small feature sizes results in a superior signal-to-noise ratio as well as comprehensive in-pixel signal processing, rendering the hybrid pixel detector principle the state-of-the-art technology for today's precision vertex detectors in particle physics [13]. Further advantages of hybrid pixels are high rate capability and large radiation tolerance while maintaining a very good spatial resolution.

The three layers of the current ATLAS Pixel Detector utilise planar sensors composed of an array of diodes placed on a low-doped n-type bulk bump-bonded to FE-I3 readout chips [14]. These chips were designed and fabricated in a commercial 250 nm technology and contain a matrix of  $18 \times 160$  pixels with a pixel size of  $50 \times 400 \ \mu\text{m}^2$ . Each chip contains 2880 readout channels with densely packed analogue and digital circuits, and uses radiation tolerant layout rules. On the other hand, the IBL modules use the FE-I4 readout chip [15], an evolution of the FE-I3 designed to cope with the high hit rates very close to the interaction point. The chip was fabricated in the IBM 130 nm technology that allows a high digital design density and radiation tolerance. The pixel array consists of  $80 \times 336$  pixels with a size of  $50 \times 250 \ \mu\text{m}^2$ . These are bump-bonded to planar silicon sensors in one type of modules or 3D silicon sensors in the other

type. The 3D sensors, where the electrodes fully penetrate the silicon substrate, were included for the first time in a large-scale collider experiment to provide superior radiation hardness close to the interaction point.

Despite good performance in the experiments thus far, the hybrid approach does have its disadvantages. The module assembly using the bumping and flip-chip technology is a complex process that drives the cost for large area detectors. The pixel pitches that are easily achievable are still rather large, in the order of 100  $\mu$ m. Moreover, the power consumption and hence the needed cooling power is high, resulting in a large material budget for large detector systems. This deteriorates the momentum and vertex measurement resolution due to the scattering of particles in the material.

To overcome these drawbacks, the next generation of R&D focuses on the development of monolithic active pixel sensors (MAPS). These detectors integrate the sensor and the readout electronics inside the same silicon die, thus completely avoiding bump-bonding. CMOS monolithic active pixel sensors can be produced using commercial CMOS processes and can therefore be very cost effective. Moreover, the extremely low sensor capacitance that can be achieved with this approach allows lower power consumption compared to their hybrid counterparts, as described in the following chapters, which reduces the material budget and limits the probability for the particles to be scattered. So far, radiation hardness has been the main disadvantage of CMOS MAPS. However, recent developments in CMOS sensor processing, also detailed later on, carry the promise of improving the radiation hardness and making MAPS a promising technology even for the most extreme radiation environments, such as the pixel layers of the ATLAS experiment. Therefore, MAPS are being proposed as an alternative to hybrid pixel detectors in the outer pixel layers of the upgraded Inner Tracker, where the cost advantage would be significant due to the large areas that need to be covered.

The monolithic sensors described in this thesis were designed with the aim to meet the requirements of the outermost, fifth pixel layer in the ATLAS ITk. The performance figures in terms of particle rates, timing and radiation hardness after the high-luminosity upgrade are comparable to those for the innermost layer currently installed in the experiment. The main requirements are summarised in table 1.1. A detection efficiency higher than 97% at the end-of-life of the detector is required, with a time resolution of 25 ns in order to separate particles from different bunch crossings. Because of the high particle hit rates in the order of 1 MHz/mm<sup>2</sup>, the detectors need to be able to process large amounts of data in a short time period. The massive data processing inside the detector leads to high power consumption and puts a high demand on power delivery and cooling, which involves large mechanical constructions and an increase in material budget. Still, the total power consumption needs to remain below 500 mW/cm<sup>2</sup> in order to limit the total material budget at 2% of  $x/X_0$  (where  $X_0$  is the radiation length of the material, i.e. the mean path length over which a high-energy electron loses all but 1/e of

its energy). The ITk also introduces unprecedented radiation levels in terms of ionising dose (>50 Mrad even for the outermost layer during the detector lifetime) and non-ionising particle fluence (>10<sup>15</sup> 1 MeV  $n_{eq}/cm^2$  for the outermost layer), which will be discussed in detail in the next chapter. A safety factor of 1.5 is often added on top of the reported values for radiation tolerance.

| Requirement                    | Unit                                   | Value            |

|--------------------------------|----------------------------------------|------------------|

| Detection efficiency           | %                                      | > 97             |

| Time resolution                | ns                                     | 25               |

| Particle rate                  | MHz/mm <sup>2</sup>                    | 1                |

| Non-ionising radiation fluence | 1 MeV n <sub>eq</sub> /cm <sup>2</sup> | 10 <sup>15</sup> |

| Ionising radiation dose        | Mrad                                   | 50               |

| Power consumption              | mW/cm <sup>2</sup>                     | < 500            |

| Material budget                | % of $x/X_0$                           | < 2              |

Table 1.1: Main performance requirements for the outermost pixel layer of the ATLAS ITk.

To achieve the desired tracking resolution, a small pixel size in the order of  $50 \times 50 \ \mu m^2$  is required, which can easily be achieved with the monolithic pixels described later on. In the case of a binary readout, where only the pattern of hit pixels is known, the position resolution of a detector  $\sigma_p$  has a direct dependence on the pixel size *p*. If only a single pixel registers a crossing particle, the position resolution is given by:

$$\sigma_p = \frac{p}{\sqrt{12}}.\tag{1.4}$$

The position resolution is improved in the case when several adjacent pixels register a hit, their number and topology depending on the impact position of the ionising particle [16]. A further improvement of the position resolution can be obtained by having analogue information about the signal generated in each pixel, in which case a center of gravity algorithm can be used for the reconstruction of the impact position.

### Chapter 2

### **CMOS** monolithic active pixel sensors

#### **2.1** Detection of particles in silicon

The basic detection mechanism of silicon detectors is the generation and movement of mobile charges (electrons and holes) in a silicon p-n junction [17]. The number of ionised charges depends on the energy loss of the traversing particle within the material, which is described in the following section. The average number of electron-hole pairs generated by a constant amount of absorbed energy can be obtained by dividing the energy E by the average energy needed to produce an electron-hole pair, w:

$$N = \frac{E}{w} \tag{2.1}$$

In silicon, w = 3.6 eV, which is more than three times the bandgap of 1.12 eV. The difference in energy is used to generate phonons, and since the fraction of energy used to generate e-h pairs and phonons is subject to fluctuations, N will vary by:

$$\left\langle \Delta N^2 \right\rangle = FN = F\frac{E}{w} \tag{2.2}$$

F is the so-called Fano factor [18], which is in the order of 0.1 for most semiconductors and provides the ultimate limit of energy resolution in semiconductor detectors.

#### 2.1.1 Energy loss of charged particles

Moderately relativistic charged particles other than electrons lose energy in matter primarily by ionisation and atomic excitation [19]. The mean rate of energy loss (or stopping power) is given by the Bethe-Bloch equation,

$$-\frac{dE}{dx} = Kz^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ \frac{1}{2} \ln \frac{2m_e c^2 \beta^2 \gamma^2 T_{max}}{I^2} - \beta^2 - \frac{\delta}{2} \right],$$

(2.3)

where z is the charge number of the incident particle, Z the atomic number of the absorber, A the atomic mass of the absorber,  $m_e$  the electron mass, c the speed of light,  $T_{max}$  the maximum kinetic energy which can be imparted to a free electron in a single collision, I the mean excitation energy,  $\delta$  the density-effect correction factor described in [20], and  $\beta$ ,  $\gamma$  and K are defined as follows:

$$\beta = \frac{v}{c},\tag{2.4}$$

$$\gamma = \frac{1}{\sqrt{1 - \frac{v^2}{c^2}}},$$

(2.5)

$$K = 4\pi N_A r_e^2 m_e c^2. (2.6)$$

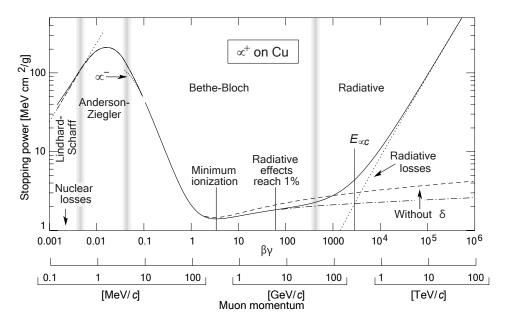

Here, v is the velocity of the incident particle,  $N_A$  is Avogadro's number and  $r_e$  the classical electron radius. With A in gmol<sup>-1</sup> the units are MeVg<sup>-1</sup>cm<sup>2</sup>. An example of the stopping power for positive muons in copper as a function of momentum is shown in fig. 2.1.

**Figure 2.1:** Stopping power (-dE/dx) for positive muons in copper as a function of momentum (reproduced from [19]).

At lower energies (and lower momenta) various corrections have to be applied, while at higher energies radiative effects become important. In practice, most relativistic particles have mean energy loss rates close to the minimum, and are said to be minimum ionising particles (MIPs). However, the mean energy loss per unit absorber thickness given by the Bethe-Bloch equation is subject to statistical fluctuations because of the stochastic nature of the energy losses. The probability density function describing the distribution of energy loss  $\Delta$  in an absorber

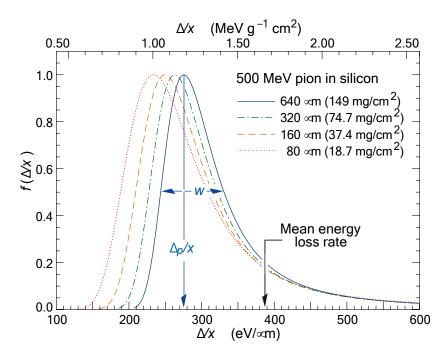

thickness x is called the Landau distribution [21]. This probability density function  $f(\Delta/x)$  for 500 MeV pions in silicon of different thicknesses, normalised to 1 at the most probable value (MPV)  $\Delta_p/x$ , is shown in fig. 2.2. Note that the most probable energy loss is below the mean energy loss predicted by the Bethe-Bloch equation due to the long tail in the distribution (the weight of few high-loss events). It can also be observed that the most probable value decreases with decreasing silicon thickness, and for very thin layers the energy loss distributions are not well described by the classical Landau function, so other models are used [22].

**Figure 2.2:** Normalised distribution of energy loss for 500 MeV pions in silicon of different thicknesses (reproduced from [19]).

Energy loss by electrons and positrons differs from loss by heavy particles because of the kinematics, spin, and the interaction of the incident electron with the electrons it ionises. At low energies, electrons lose energy mainly by ionisation, but the parameter I in the Bethe-Bloch equation needs to be modified based on a combination of experimental data and theoretical considerations [23]. At high energies (typically above a critical energy of a few tens of MeV in most materials), bremsstrahlung, i.e. radiation produced by the deceleration of electrons when deflected by the nuclei, becomes the dominant energy loss mechanism. The mean distance over which a high energy electron loses all but 1/e of its energy by bremsstrahlung is defined as the radiation length  $X_0$ , which has been calculated and tabulated for different elements [24].

When a charged particle traverses a medium, it is deflected by many small-angle scatters, primarily caused by the Coulomb interaction between the particle and the nuclei. The scattering angle when leaving the material after a large number of interactions follows roughly a Gaussian

distribution with a root-mean-square (RMS) value of:

$$\theta_{plane}^{RMS} = \frac{13.6 \text{ MeV}}{\beta pc} z \sqrt{\frac{x}{X_0}} \left[ 1 + 0.038 \ln \frac{x}{X_0} \right], \qquad (2.7)$$

where the angle  $\theta$  is expressed in rad, the particle momentum *p* in MeV. As mentioned earlier, this multiple scattering will have an impact on the position resolution of a silicon detector composed of multiple layers.

#### 2.1.2 Signal formation in the sensor

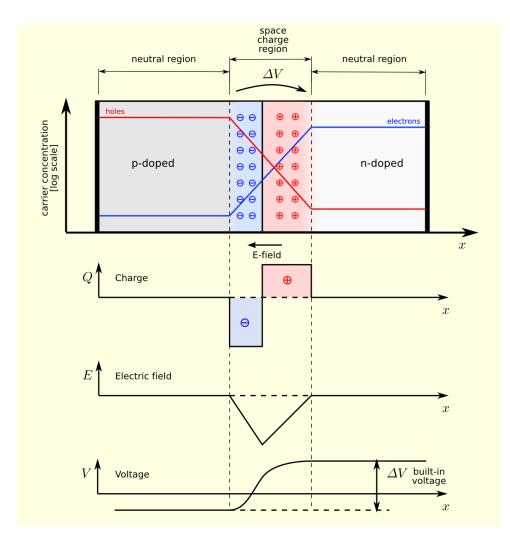

In practically all silicon particle detectors, the basic building block of the sensor is a reversebiased p-n junction. At the transition between the n-type and the p-type material, majority carriers from one side diffuse to the other side and recombine with the majority carriers producing a region depleted of free carriers [26]. The space charge in this depletion region causes an electric field to build up across the junction, as shown in fig. 2.3. The potential difference on

**Figure 2.3:** A p-n junction in thermal equilibrium with zero bias voltage applied. Plots for the charge density, the electric field, and the voltage are also reported (reproduced from [25]).

the two sides can be described by the so-called built-in voltage  $V_{bi}$  ( $\Delta V$  in fig. 2.3), which for an abrupt p-n junction in thermal equilibrium is given by:

$$V_{bi} = \frac{kT}{e} \ln\left(\frac{n_{0n}p_{0p}}{n_i^2}\right) \approx \frac{kT}{e} \ln\left(\frac{N_D N_A}{n_i^2}\right),\tag{2.8}$$

where  $n_{0n}$  and  $p_{0p}$  are the majority carrier concentrations on both sides, and in the case of complete ionisation they can be approximated by the donor and acceptor concentrations,  $N_D$  and  $N_A$ , respectively. *k* is the Boltzmann constant, *T* the temperature and *e* is the electron charge, while  $n_i$  is the intrinsic carrier concentration in silicon.

By applying a reverse bias V over the junction in addition to the built-in voltage, one can further remove majority carriers from each side and extend the depletion region. By solving the one dimensional Poisson equation, the width of the depletion region for a planar junction is obtained as the sum of the depletion region width on both sides:

$$W = x_n + x_p = \sqrt{\frac{2\varepsilon_0\varepsilon_{Si}}{e} \left(\frac{1}{N_D} + \frac{1}{N_A}\right)(V + V_{bi})}.$$

(2.9)

By assuming a reverse bias voltage significantly higher than the built-in voltage and a p-n junction with the n-side much more heavily doped than the p-side, this simplifies to:

$$W = \sqrt{\frac{2\varepsilon_0 \varepsilon_{Si}}{eN_A}V},\tag{2.10}$$

which is an expression widely used to calculate the depletion depth. In this case, the maximum electric field can be obtained as follows:

$$E_{max} = \frac{2V}{W} = \sqrt{\frac{2eN_A}{\varepsilon_0 \varepsilon_{Si}}V}.$$

(2.11)

The resistivity  $\rho$  of a semiconductor is approximately inversely proportional to the doping concentration  $N_A$ , so from eq. 2.10 one can obtain:

$$W \sim \sqrt{\rho V}.$$

(2.12)

From these equations, it is obvious that applying a high reverse bias voltage will result in a wider depletion region and higher electric field, while having a lowly doped junction (high resistivity) also helps to increase the depletion region.

The reverse-biased p-n junction also constitutes a capacitance C. For a planar junction, this capacitance can be estimated using the well known formula for a parallel-plate capacitor:

$$C = \varepsilon_0 \varepsilon_{Si} \frac{A}{d}, \qquad (2.13)$$

where A is the area of the junction and d is to be replaced by the width of the depletion region. It

is important to note that a smaller junction area and a wider depletion region leads to a decrease in the sensor capacitance, which has a significant impact on the timing and noise performance of the detector, as will be discussed later on.

In the absence of radiation, a steady current still flows in a reverse-biased p-n junction. This so-called leakage current stems from the diffusion of carriers from undepleted areas into the depletion region as well as thermal carrier generation within the depletion region. The thermal generation current depends on the depletion volume and is often the dominant leakage current component. It can be calculated as:

$$J_{vol} \approx -e \frac{n_i}{\tau_g} W, \tag{2.14}$$

with  $J_{vol}$  being the volume leakage current per unit area and  $\tau_g$  the carrier generation lifetime. This current has an impact on the operating point of the electronics following the sensor (as discussed in later sections). Since it has an exponential temperature dependence (due to the temperature dependence of  $n_i$  and  $\tau_g$ ), a common way to minimise it and limit the influence on the detector is to operate the sensors at low temperature.

If the reverse bias is increased to sufficiently high values, there is a sharp increase in current referred to as breakdown. This is usually caused by impact ionisation in regions with high electric fields close to the junction, where highly energetic carriers can ionise new carriers in collisions with the lattice and cause carrier multiplication [27]. This process is called avalanche breakdown, and it is the voltage at which this breakdown occurs that usually limits the maximum operating voltage of a sensor.

One polarity of the signal charge generated by a traversing particle is collected by one electrode of the p-n junction. Charge generated inside the depletion region will quickly drift towards the collection electrode. If the sensor is not fully depleted, diffusion in the non-depleted areas also plays an important role in the charge collection process. According to the Ramo theorem [28], a signal is already detectable when the charge carriers of both polarities start moving, and not only when charge arrives to the collection electrode. The instantaneous current induced on an electrode by the movement of a charge e with a drift velocity v (which is often proportional to the electric field) is given by:

$$i = eE_w v, \tag{2.15}$$

where  $E_w$  is the so-called weighting field, which is different from the actual electric field in the sensor and is obtained by applying a unit potential to the electrode under consideration and zero potential to all other electrodes. To calculate the charge Q induced on an electrode by a charge e drifting in the time interval  $[t_1, t_2]$  from position  $x_1$  to  $x_2$ , one has to integrate 2.15 over the

time of charge collection:

$$Q = \int_{t_1}^{t_2} i(t)dt = e\left[\phi_w(x_1) - \phi_w(x_2)\right],$$

(2.16)

where  $\phi_w$  is the weighting potential, also obtained by raising the electrode under consideration to unit potential, setting all others to zero, and solving the Poisson equation [29].

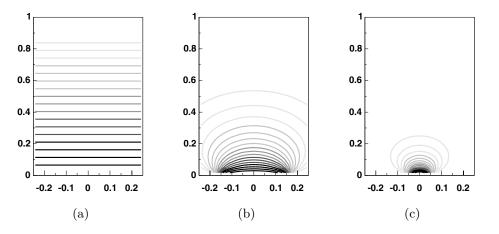

This weighting potential is plotted in fig. 2.4 assuming an arbitrary sensor thickness of 1 in the y-direction, an infinitely wide electrode at y = 1 and a collection electrode of different widths at y = 0 on which the unit potential is applied. Fig. 2.4a shows the weighting potential for two infinite parallel plates, while fig. 2.4b and c show this potential for a collection electrode width of 1/3 and 1/10, respectively. The smaller the electrode, the larger the area where the weighting potential approaches zero, meaning that drift of carriers in this area will induce very little signal on the collection electrode. The closer the charge is to the electrode, the more signal it will induce, as seen by the increasing gradient of the weighting potential, and for small electrodes, most of the signal is induced in this last part of the drift path. Once all the charge has arrived to the collection electrode, the integral of the induced current is the total collected charge. The time it takes to collect the charge by drift in silicon sensors is typically in the order of a few nanoseconds.

**Figure 2.4:** Weighting potential for (a) two infinite parallel plates and a collection electrode width of (b) 1/3 and (c) 1/10 times the sensor thickness (reproduced from [29]).

#### 2.2 Radiation effects in the sensor – Non-ionising energy loss

When interacting with the silicon sensor material, the energy loss of highly energetic particles does not result exclusively in the generation of electron-hole pairs producing the electrical signal, but also with the displacement of nuclei out of their lattice position. This non-ionising energy loss component leads to the creation of defects in the crystal, which may be electrically active and change the electrical properties of the material. The primary lattice defects

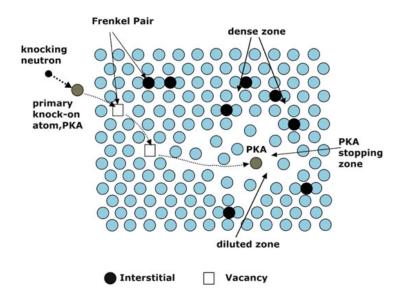

initially created are vacancies and interstitials. A vacancy is the absence of an atom from its normal lattice position. If that displaced atom moves into a non-lattice position, the resulting defect is called an interstitial. A stable configuration of a vacancy and an adjacent interstitial is a secondary point defect known as a Frenkel pair [30]. Apart from point defects, the primary knock-on atom dislodged by the incident particle can displace many other atoms locally, thereby creating a disordered region with a high defect density, a so-called cluster defect. A depiction of the different types of lattice defects produced by an incident neutron with an energy in the order of 1 MeV is given in fig. 2.5 (reproduced from [31]).

Figure 2.5: An example of defect generation in silicon by an impinging high-energy neutron [31].

Different types of particles interact differently with the silicon lattice. For example, charged particles will produce more point defects and less clusters than neutrons due to their electromagnetic interaction with the atom nuclei. To be able to compare the damage caused by different types of particles with different energies, the displacement damage is described through a quantity called non-ionising energy loss (NIEL), which relates the damage caused by a certain fluence of particles to the damage caused by a fluence of 1 MeV neutrons. The displacement damage is hence often described in terms of neutron equivalent fluence,  $n_{eq}/cm^2$ . The hardness factor  $\kappa$  is used to convert the damage caused by a certain type of particle with a certain energy to the damage caused by 1 MeV neutrons, and is e.g. equal to 0.62 for 24 GeV protons provided by the CERN-PS.

The net result of all the defects created in the material is the introduction of energy levels in the bandgap, which can give rise to a number of adverse effects. One of them is the increase in leakage current, since the energy levels in the bandgap act as generation-recombination centres. The radiation-induced energy levels near the middle of the bandgap can cause a significant increase in thermal generation rates, which is the main mechanism for leakage current increases in silicon devices. This increase in volume generation current is proportional to the fluence.

Another effect is the trapping of carriers at a deep level, where a carrier can recombine and be lost for detection, or at a shallow level, where a carrier is temporarily captured at a defect centre and is later emitted to its band. This leads to a reduction in carrier lifetimes and consequently the diffusion length. Given a carrier lifetime  $\tau$ , an initial amount of generated charge  $Q_0$  will decay exponentially with time:

$$Q(t) = Q_0 \ e^{-t/\tau}.$$

(2.17)

Therefore, charge trapping in the sensor material can cause a reduction in sensor signal. Because of that, one of the main approaches to improve the radiation hardness of silicon sensors is to collect the charge by drift rather than diffusion, which strongly reduces the charge collection time and the probability for signal charge to be captured by radiation-induced traps.

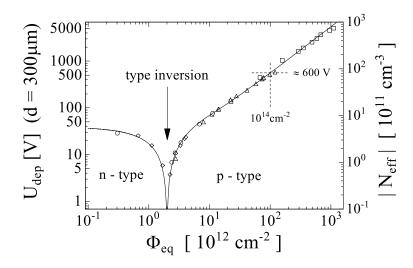

A third important effect is the change in the effective doping concentration caused by charged defects. An example of this is shown in fig. 2.6. The acceptor-like traps in the n-type starting material alter the effective doping concentration (as well as the full depletion voltage) to the point where, after a fluence of around  $10^{12} n_{eq}/cm^2$ , the material starts behaving like p-type. As a consequence of this type inversion (or space charge sign inversion), the pn-junction moves from the p+ side of the sensor to the n+ side and the space charge region grows from there [29].

**Figure 2.6:** Full depletion voltage of a 300-µm-thick silicon sensor and its absolute effective doping versus the normalised fluence (reproduced from [29]).

Note that all these effects can be counteracted to a certain extent by the recombination and rearrangement of defects over time, referred to as annealing. Several material properties, such as minority-carrier lifetime, diffusion length or leakage current show a recovery after either short-term or long-term annealing. These processes depend strongly on the temperature as well as the free carrier concentration within the device [32].

#### 2.3 Monolithic sensor concepts

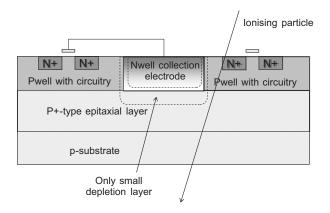

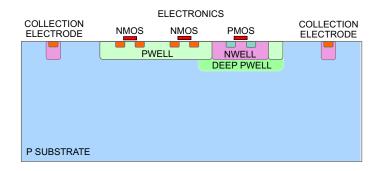

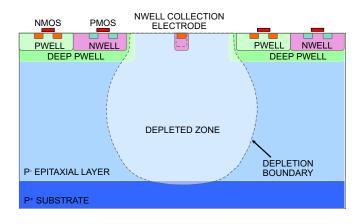

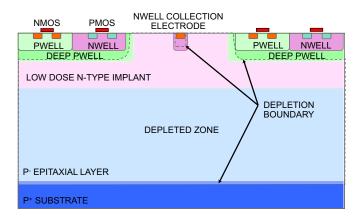

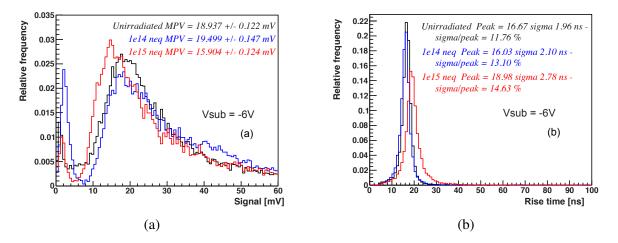

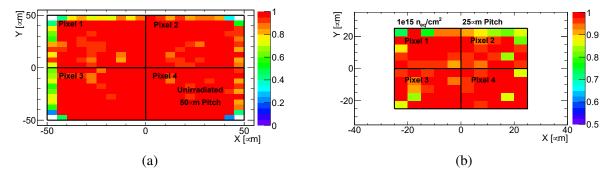

Monolithic active pixel sensors (MAPS) integrate the sensor and the readout electronics on the same chip. Fig. 2.7 shows a cross-section of a typical MAPS detector [33]. The n-well collection electrode on a p-type epitaxial layer collects the charge generated by the traversal of an ionising particle. The p-wells around the collection electrode host the in-pixel electronics consisting of NMOS transistors. In the small depletion region around the collection electrode, the generated charge is collected by drift, but the vast majority of the epitaxial layer remains undepleted and the signal charge is primarily collected by diffusion. In this case, the collection electrode occupies only a small fraction of the total pixel area, so this is referred to as a small collection electrode design. To enhance the depletion and achieve faster charge collection by drift, leading to better radiation tolerance, one can also place the front-end and readout electronics inside the collection electrode. In this case, the electronics will occupy most of the pixel area and this is called a large collection electrode design.

Figure 2.7: Cross-section of a typical MAPS detector (reproduced from [33]).

#### **2.3.1** Small collection electrode designs

The main advantage of the small collection electrode approach is a low sensor capacitance, which can be in the order of a few femtofarads. This capacitance has far-reaching consequences for many design aspects, in particular the noise and power consumption of MAPS. The collection electrode is typically followed by an amplification stage, where the thermal noise in the channel of the input transistor is usually the dominant noise source [34]. Regardless of the operating region of this transistor, its thermal noise expressed as an equivalent series voltage is inversely proportional to the square root of its transconductance  $g_m$ . Since the voltage signal on the collection electrode with a capacitance *C* obtained by collecting a charge *Q* is given by

$$V = \frac{Q}{C},\tag{2.18}$$

for the signal-to-noise ratio one can write:

$$\frac{S}{N} \sim \frac{Q}{C} \sqrt{g_m}.$$

(2.19)

In general,  $g_m$  is either proportional to the transistor bias current (in weak inversion) or to the square root of the bias current (in strong inversion). Assuming that this bias current dominates the overall power consumption P, eq. 2.19 can be rearranged to yield:

$$P \sim \left(\frac{S/N}{Q/C}\right)^{2m},\tag{2.20}$$

where  $1 \le m \le 2$  depending on the operation region of the input transistor. Conversely, the thermal noise of the input device in strong inversion in an open-loop circuit with a flat frequency response over a certain bandwidth, expressed as an equivalent noise charge (i.e. the input charge fluctuation required to cause the voltage noise observed at the output), can be written as:

$$ENC_{thermal}^2 \sim \frac{4}{3} \frac{kT}{g_m} \frac{C^2}{\tau},$$

(2.21)

where k is the Boltzmann constant, T the temperature and  $\tau$  the shaping time of the circuit. As the noise scales linearly with the capacitance, a low capacitance is key for achieving an optimal low-noise performance. All these equations illustrate the interdependence between the sensor capacitance, power consumption, noise and timing in MAPS. One can conclude that a small sensor capacitance and a large Q/C ratio are crucial to achieve a low power consumption for a given bandwidth and signal-to-noise ratio.

The cross-section shown in fig. 2.7 contains only NMOS transistors in the readout electronics. However, MAPS often have to contain more complex circuitry for signal processing. If PMOS transistors are used, the n-wells hosting these transistors normally compete with the collection electrode in the charge collection process, thereby causing the loss of signal charge. To avoid this, a deep p-well can be used to shield the n-wells of the transistors from the substrate, thus allowing the use of full complementary CMOS logic in the pixel (see fig. 2.8).

**Figure 2.8:** Cross-section of a small collection electrode design. A deep p-well is used to shield the n-wells of PMOS transistors, allowing full CMOS in the pixel.

However, with a small collection electrode, reaching full depletion under the deep p-well is still difficult, unless the area of the deep p-well and the circuitry inside it is very small. To increase the depletion region and the drift component in the charge collection, thereby increasing the radiation tolerance, more recent devices use a high-resistivity substrate or epitaxial layer [35]. This can increase the amount of collected charge while maintaining a low capacitance, leading to a higher Q/C and better S/N. Another way to enhance the charge collection electrode. However, this voltage is limited by the breakdown voltage of transistor junctions in standard CMOS processes, and is typically in the range of only several volts. An option is to AC-couple the collection electrode to the following amplifying stage and apply a high positive voltage to the electrode itself, but this has some penalty in sensor capacitance. Changes in the standard fabrication process can also be employed to optimise the sensor for particle detection in high-radiation environments, which will be discussed more in detail in the following chapters.

# 2.3.2 Large collection electrode designs

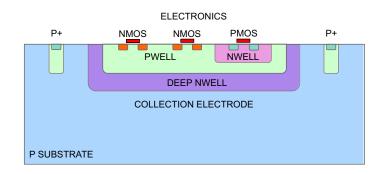

The large collection electrode approach places the front-end and readout circuitry inside a deep n-well collection electrode, as depicted in fig. 2.9. Since the transistor junctions are now isolated from the p-type substrate, a high reverse bias voltage in the order of 50-100 V can be applied to the collection diode [36]. The lowly doped junction combined with the high reverse voltage induces a large depleted area where charge is collected by drift, resulting in a fast charge collection and high radiation tolerance.

Figure 2.9: Cross-section of a large collection electrode high voltage design.

The drawback of a large collection electrode is a large input capacitance in the order of hundreds of femtofarads, mainly because of the junction capacitance between the deep n-well and the p-well housing the electronics. For this reason, to achieve a high Q/C one has to either limit the area and complexity of the readout circuit to achieve a smaller capacitance, or increase the collected charge e.g. by using thick high-resistivity substrates for the sensitive layer. A high

signal is needed to overcome the higher noise levels due to the large input capacitance, thereby achieving a high S/N.

Another potential problem in this approach is the risk of coupling circuit signals into the collection electrode. The bulk of all NMOS transistors is capacitively coupled to the deep n-well and therefore to the sensor cathode, so any disturbance in the p-well caused by the in-pixel digital logic can cause an unwanted signal at the collection node. Therefore, special care needs to be taken in the design of the electronics to reduce this crosstalk to acceptable levels.

#### **2.3.3** Other approaches - DEPFET and SOI

Another structure used in monolithic pixel sensors is the so-called depleted field-effect transistor (DEPFET) [37]. The DEPFET is essentially a PMOS transistor on top of an n-type depleted substrate with a backside junction. Charge generated in the sensor is collected in a potential well under the PMOS channel, and can modulate the source-drain current of the PMOS transistor just as much as a change in the gate voltage. This provides an internal amplification of the signal charge. The small collection electrode capacitance allows low-noise operation. The sensor can be read out by sampling the voltage on the PMOS source or by integrating the drain current. DEPFETs are already used in high-energy physics experiments, but limited radiation hardness due to damage in the MOS structure oxide and a complex development and fabrication of these devices make them less attractive for high-radiation environments.

MAPS have also been fabricated in SOI technology [38]. These devices are composed of a thick, high-resistivity substrate for the sensing part (under the buried oxide) and a thin silicon layer for CMOS circuits. Due to the high bias voltages applied to deplete the sensor, the so-called back-gate effect has traditionally caused problems by affecting the operation of transistors in the front-end and readout electronics. However, this can be mitigated using additional process steps such as implanting a buried p-well under the buried oxide. Good performance of SOI pixels in a particle beam has been demonstrated, and further improvements are being developed for radiation hardness, which has been limited due to the accumulation of radiationinduced charge in the buried oxide affecting the sensor and electronics.

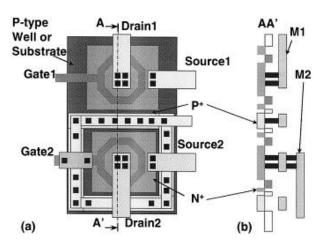

# 2.4 Radiation effects in the electronics – Total ionising dose and single event effects

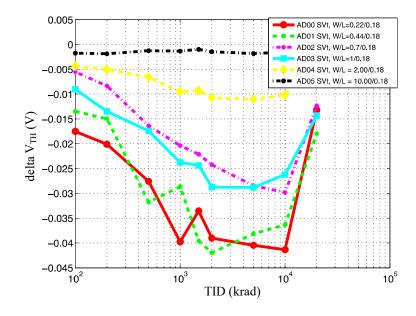

The front-end and readout electronics are mainly affected by ionising radiation because of the damage in the surface oxide layers and at the  $Si-SiO_2$  interface. The damage is described through a quantity called total ionising dose (TID) and is measured in units of rad. TID is known to lead to two types of defects in dielectrics: trapped charges and interface states. The trapped

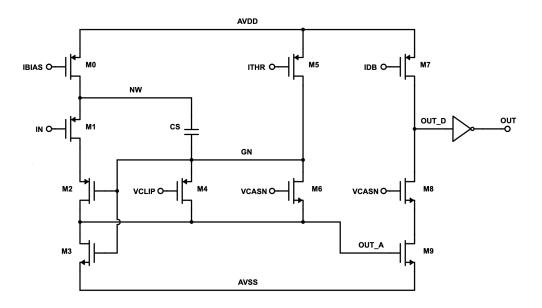

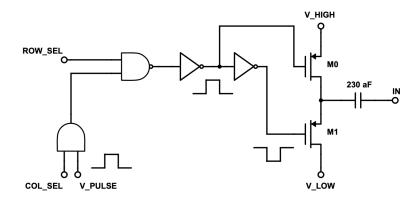

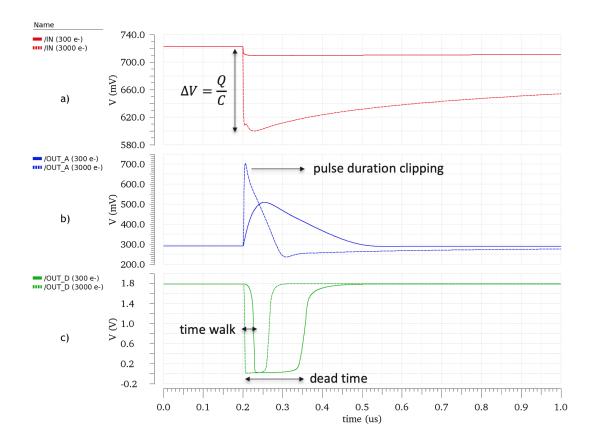

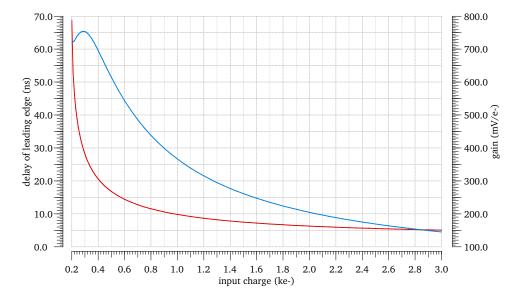

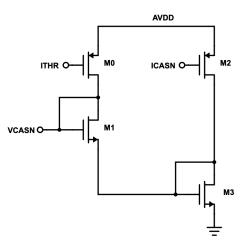

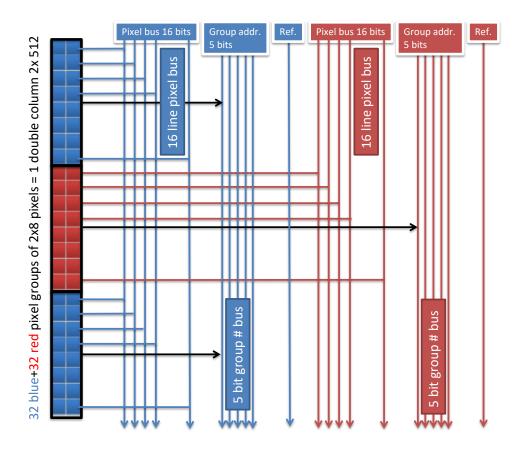

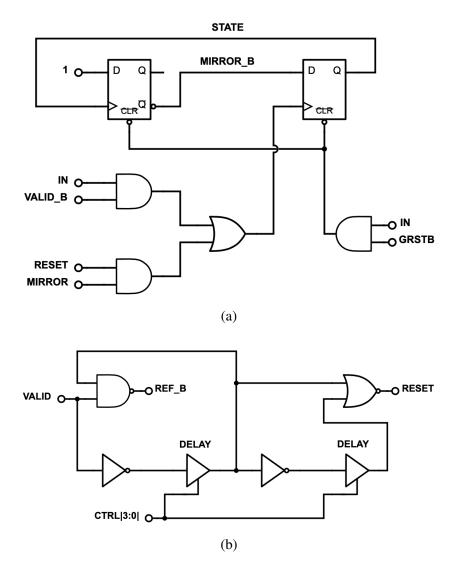

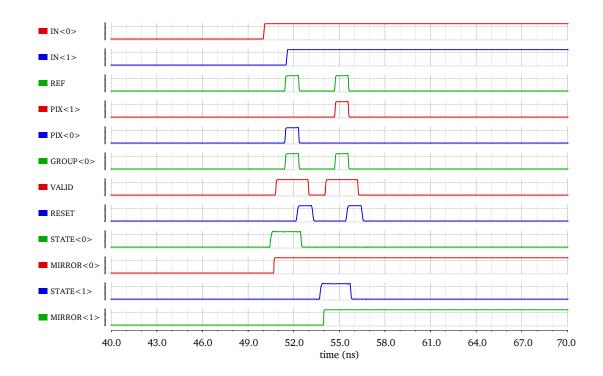

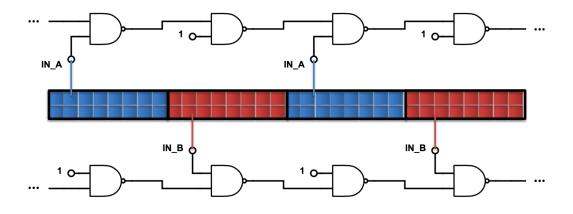

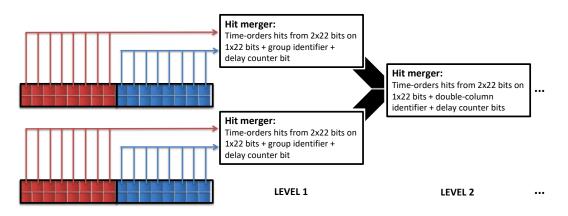

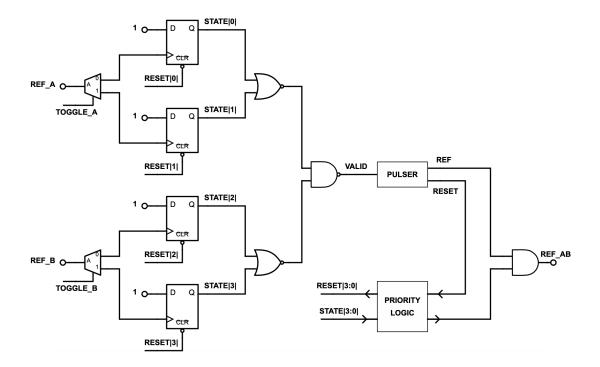

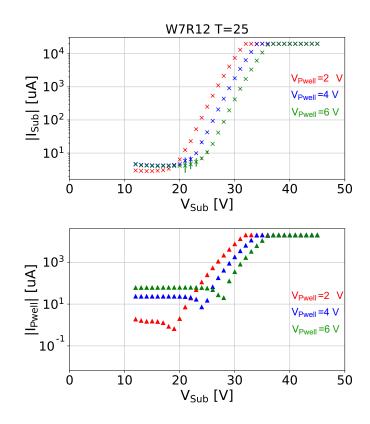

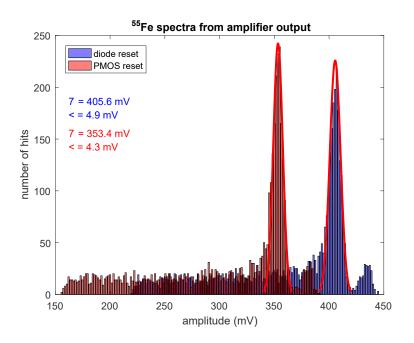

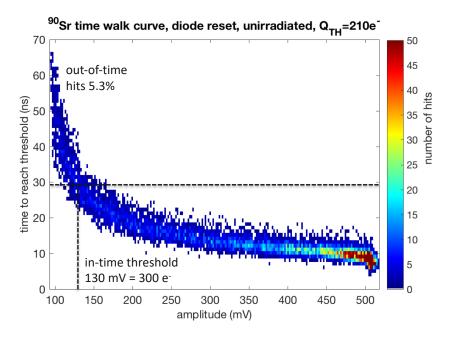

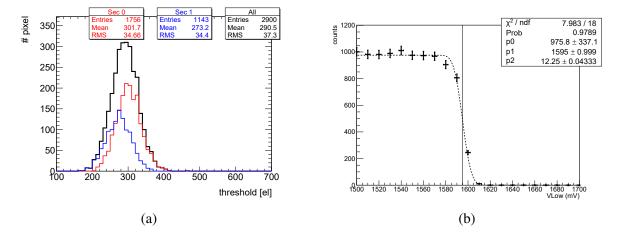

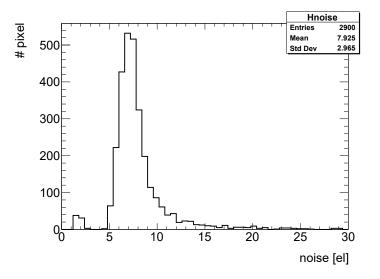

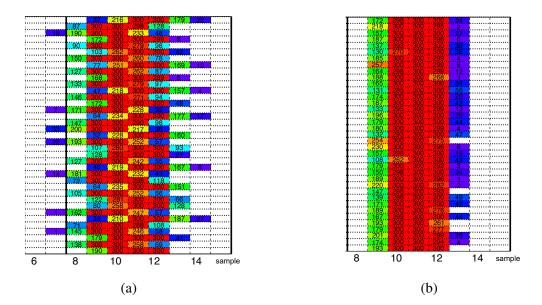

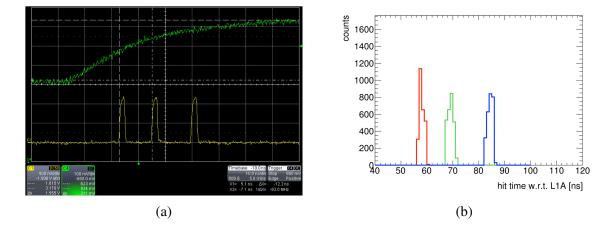

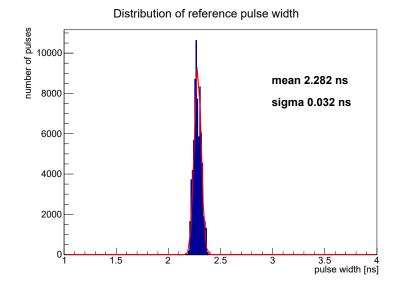

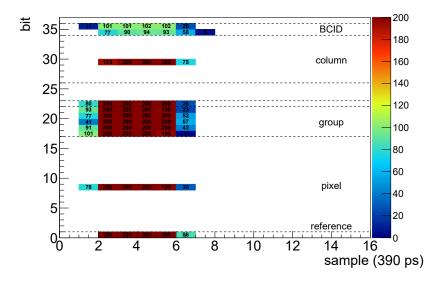

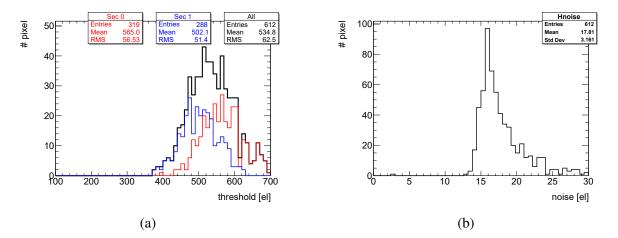

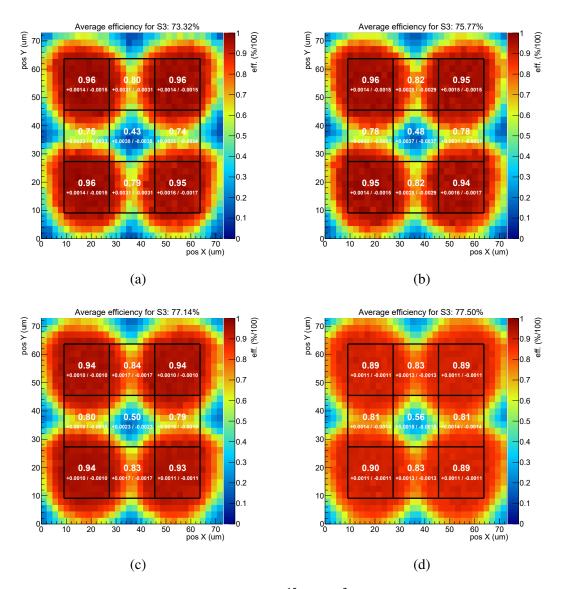

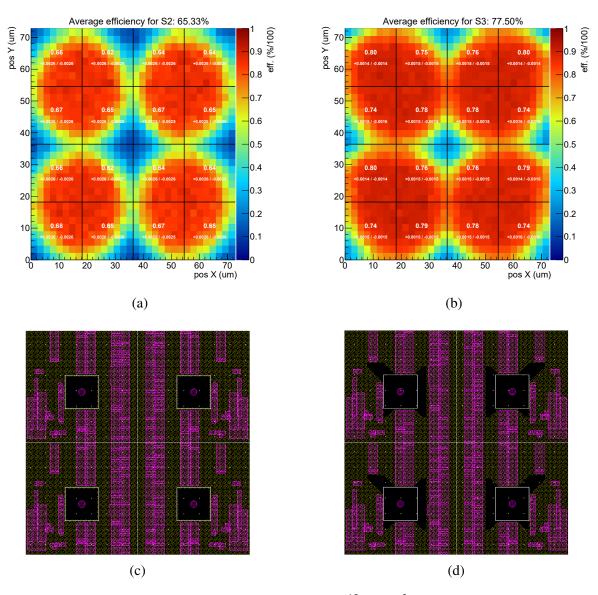

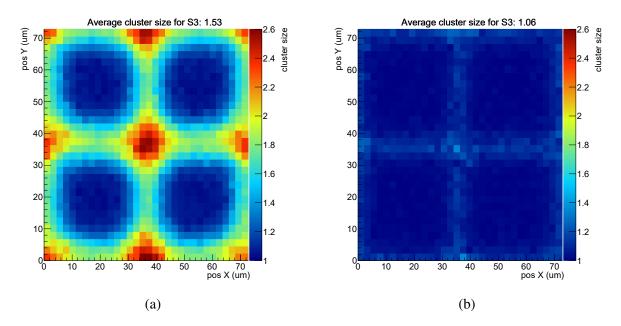

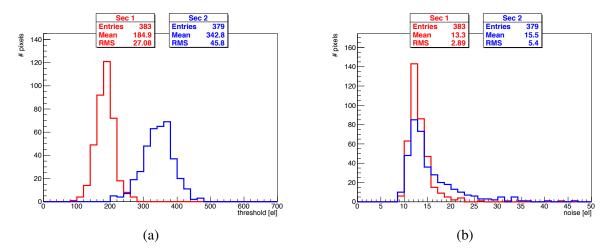

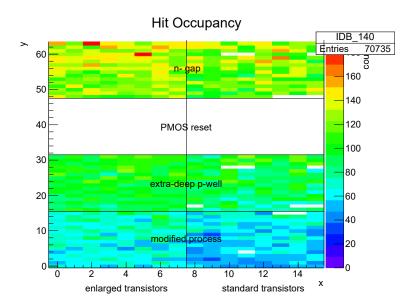

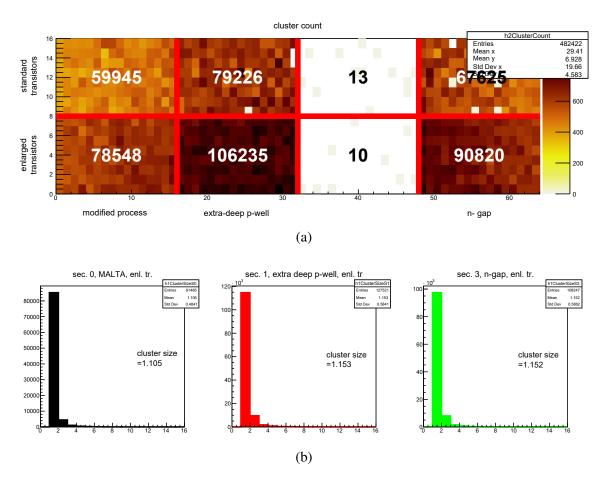

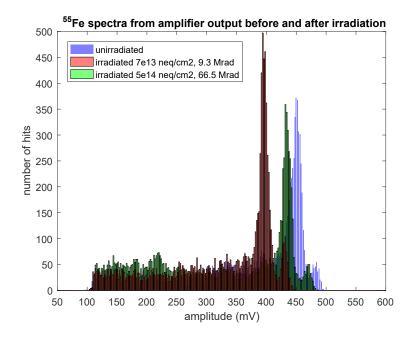

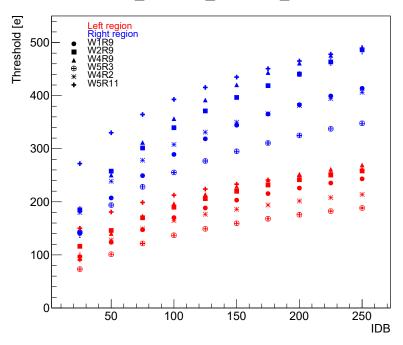

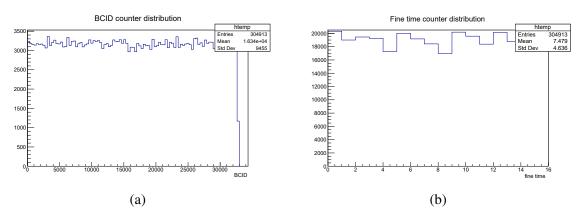

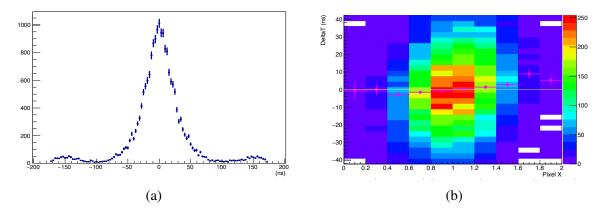

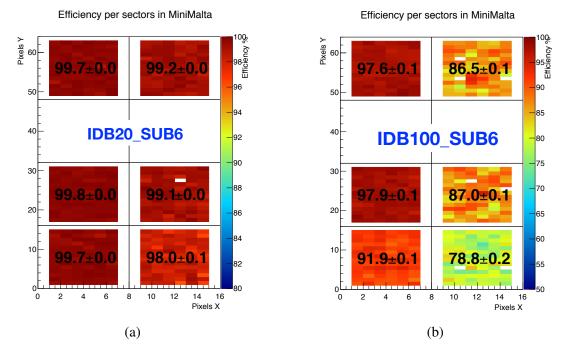

charges are mainly holes, which can get trapped permanently near the  $Si-SiO_2$  interface due to their very low mobility in the oxide. Interface states are dangling Si bonds which introduce energy states in the silicon band gap, at the interface [39].