# Methodology for block-wise behavioural modelling of integrated circuits for electromagnetic compatibility applications

Magerl, Marko

**Doctoral thesis / Disertacija**

2022

Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Zagreb, Faculty of Electrical Engineering and Computing / Sveučilište u Zagrebu, Fakultet elektrotehnike i računarstva

Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:168:111051

Rights / Prava: In copyright/Zaštićeno autorskim pravom.

Download date / Datum preuzimanja: 2024-04-25

Repository / Repozitorij:

FER Repository - University of Zagreb Faculty of Electrical Engineering and Computing repozitory

### FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Marko Magerl

# METHODOLOGY FOR BLOCK-WISE BEHAVIOURAL MODELLING OF INTEGRATED CIRCUITS FOR ELECTROMAGNETIC COMPATIBILITY APPLICATIONS

**DOCTORAL THESIS**

### FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Marko Magerl

# METHODOLOGY FOR BLOCK-WISE BEHAVIOURAL MODELLING OF INTEGRATED CIRCUITS FOR ELECTROMAGNETIC COMPATIBILITY APPLICATIONS

**DOCTORAL THESIS**

Supervisor: Professor Adrijan Barić, PhD

Zagreb, 2022

# FAKULTET ELEKTROTEHNIKE I RAČUNARSTVA

Marko Magerl

# METODOLOGIJA ZA PONAŠAJNO MODELIRANJE BLOKOVA INTEGRIRANIH SKLOPOVA ZA PRIMJENE U ELEKTROMAGNETSKOJ KOMPATIBILNOSTI

**DOKTORSKI RAD**

Mentor: Prof. dr. sc. Adrijan Barić

Zagreb, 2022.

This doctoral thesis was completed at the University of Zagreb Faculty of Electrical Engineering and Computing, Department of Electronics, Microelectronics, Computer and Intelligent Systems.

| Supervisor: Professor Adrijan Barić, Ph | Supervisor: | Professor | Adriian | Barić. | PhD |

|-----------------------------------------|-------------|-----------|---------|--------|-----|

|-----------------------------------------|-------------|-----------|---------|--------|-----|

This doctoral thesis contains 177 pages.

Doctoral thesis No.: \_\_\_\_\_

# About the Supervisor

Adrijan Barić was born in Zagreb in 1958. He received the Dipl. Ing. degree in 1982 and the M.Sc. degree in 1985 from the University of Zagreb (UniZag), Faculty of Electrical Engineering and Computing (FER), Croatia. He received the PhD degree in 1995 from the Dublin City University, Ireland. He is employed by FER since 1984. He was a visiting researcher at the Rutherford Appleton Laboratory, England, and at the Ghent University, Belgium. He was promoted to Full professor in 2013. He was a principal investigator of two projects funded by the Ministry of Science, Education and Sports of Croatia, one BICRO project, and he coordinated the FER research team in one EU FP6 project, one EU FP7 project, and several bilateral and multilateral projects with European companies and universities. He presently coordinates the project "Sensor Fusion" funded by ams-OSRAM AG, Austria, and the project "Fast switching converters based on GaN devices and resonant architectures" funded by the Croatian Science Foundation. He published over 100 papers in scientific journals and scientific conference proceedings in the area of integrated circuits and electromagnetic compatibility. He was the President of the Committee for Research, Development and Technology of the UniZag from 2008 to 2011, and the President of the Council of Technical Faculties of the UniZag from 2013 to 2017. He was a General Chair or Co-Chair of two IEEE conferences, the Finance Chair of one IEEE conference, and the Technical Programme Chair of the IEEE conference EMC Compo 2011. He is a member IEEE, HD MIPRO, KoREMA, and AMAC-FER societies. In 2015, he received the Gold Plaque "Josip Lončar" from FER.

### O mentoru

Adrijan Barić rođen je u Zagrebu 1958. Diplomirao je 1982. i magistrirao 1985. na Fakultetu elektrotehnike i računarstva (FER) Sveučilišta u Zagrebu (SuZ). Doktorirao je 1995. na Dublin City University, Irska. Na FER-u radi od 1984. Bio je gostujući istraživač na Rutherford Appleton Laboratory, Engleska te na Ghent University, Belgija. U redovitog profesora u trajnom zvanju izabran je 2013. Bio je glavni istraživač na dva projekta MZOS-a, jednom BICRO projektu te je vodio je FER-ov tim u jednom EU FP6, jednom EU FP7 projektu te više bilateralnih i multilateralnih projekata s europskim tvrtkama i sveučilištima. Trenutno vodi projekt HRZZ-a "Brzi prekidački pretvornici zasnovani na GaN elementima i rezonantnim arhitekturama" te projekt "Sensor Fusion" s tvrtkom ams-OSRAM AG, Austrija. Objavio je više od 100 radova u znanstvenim časopisima i zbornicima znanstvenih konferencija iz područja integriranih sklopova i elektromagnetske kompatibilnosti. Bio je predsjednik Odbora za istraživanje, razvoj i tehnologiju SuZ-a od 2008. do 2011. te predsjednik Vijeća tehničkog područja SuZ-a od 2013. do 2017. Bio je predsjedatelj ili supredsjedatelj dviju IEEE konferencija, financijski voditelj jedne IEEE konferencije te Technical Programe Chair IEEE konferencije EMC Compo 2011. Član je udruga IEEE, HD MIPRO, KoREMA i AMAC-FER. Godine 2015. primio je FER-ovu Zlatnu plaketu "Josip Lončar".

#### **Abstract**

The echo state network (ESN) is presented as the building block for the behavioural modelling of integrated circuits. The ESN is able to model the nonlinear relationships of time-domain signals observed in integrated circuit simulations. An adaptive algorithm for sampling the nonlinear behaviour of integrated circuits in the time-domain is proposed, that enables building ESN models that cover a wide range of operation of the modelled circuit.

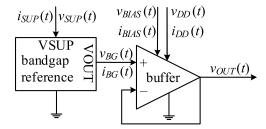

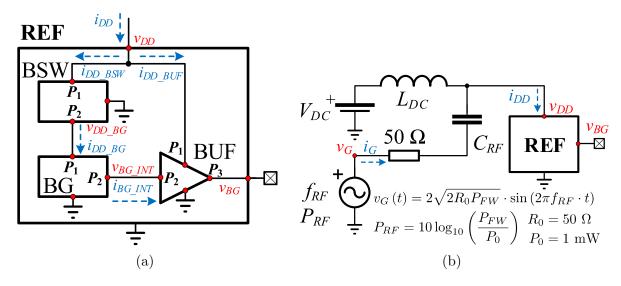

A nonlinear impedance model based on the echo state network is proposed. The model enables building interchangeable behavioural models of integrated circuits in the conducted immunity simulation environment according to the IEC-62132-4 Direct RF Power Injection (DPI) standard, and it is applied to a buffered voltage reference integrated circuit that consists of three subcircuits.

An overview of nonlinear effects observed in the conducted immunity simulations of the modelled circuit is presented, and the methodology for evaluating the accuracy of the modelled time-domain waveforms is introduced. The stability of the presented behavioural models is analysed, including the DC operating point stability, the small-signal stability, and the initial transient stability.

The behavioural modelling principles are also applied to modelling applications in ESD and EMC area. A lumped-distributed model of a transmission line pulsing setup is presented, including a behavioural model of an ESD protection device that exhibits snapback. The behavioural model of an I2C pad of an industrial integrated circuit is presented that enables simulating the RF re-radiation due to RF harmonic distortion in a magnetically coupled wireless system.

**Keywords**: electromagnetic compatibility, behavioural modelling, echo state networks, nonlinear impedance modelling, stability analysis, direct power injection, artificial neural networks, bandgap reference, simulation speed-up, adaptive sampling, conducted immunity

# Extended abstract in Croatian language:

# Metodologija za ponašajno modeliranje blokova integriranih sklopova za primjene u elektromagnetskoj kompatibilnosti

Obzirom na porast složenosti integriranih sklopova u poluvodičkoj industriji, elektromagnetska kompatibilnost (eng. electromagnetic compatibility, EMC) postala je sastavni dio procesa projektiranja i ispitivanja integriranih sklopova. Simulacije ponašanja integriranih sklopova podvrgnutih zračenim ili vođenim elektromagnetskim smetnjama visokih frekvencija i amplituda omogućuju proizvođačima integriranih sklopova smanjivanje troškova projektiranja poluvodičkih proizvoda te njihov brži plasman na tržište.

Potreba za simulacijskim modelima integriranih sklopova koji omogućuju veću brzinu simulacija uz manje memorijske zahtjeve dovela je do vrlo aktivnog istraživačkog rada na području ponašajnog modeliranja. Ponašajni modeli generiraju ponašanje integriranih sklopova koje se opaža na stezaljkama modeliranih sklopova, bez korištenja informacija o njihovom unutarnjem ustrojstvu. Na ovaj način ponašajni modeli omogućuju smanjivanje kompleksnosti simulacijskih modela te zaštitu intelektualnog vlasništva.

Integrirani sklopovi su nelinearni sustavi s memorijom jer su izlazni signali definirani kao nelinearne transformacije ulaznih signala i njihovih prethodnih vrijednosti u vremenskoj domeni. Neuronske mreže s povratnom vezom (eng. recurrent neural networks, RNN) su podskup umjetnih neuronskih mreža koje modeliraju nelinearne sustave s memorijom pomoću povratnih veza između neurona u jednom ili više skrivenih slojeva mreže. Glavni nedostatci RNN mreža su potencijalna nestabilnost modela te sporo vrijeme treniranja, koje se u većini metoda temelji na gradijentnom spuštanju (eng. gradient descent).

Predstavljeni su rezultati istraživanja iz područja izgradnje zamjenjivih ponašajnih modela (eng. interchangeable behavioural models) integriranih sklopova temeljenih na ESN mrežama (eng. echo state network) za primjene u simulacijama otpornosti sklopova na vođene smetnje. ESN mreža je podskup RNN mreža s vrlo kratkim vremenom treniranja i zajamčenom stabilnošću.

Predstavljeni ponašajni modeli ispravno modeliraju nelinearne ulazne i izlazne impedancije integriranih sklopova te zbog toga ispravno opterećuju tranzistorske sklopove s kojima su spojeni u električnoj shemi koja definira sklopovsku simulaciju (eng. test bench). Modeli su precizni u širokom rasponu amplituda vođenih smetnji te ispravno reproduciraju pomak statičke radne točke i pojavu harmonika višeg reda. Ovisno o modelu i primjeni, koeficijenti ubrzanja sklopovskih simulacija iznose od 2 puta do 100 puta uz zadržavanje dobre preciznosti modela.

ESN mreža uvodi se kao temeljna sastavnica za modeliranje ponašanja nelinearnih integriranih sklopova u uvjetima velikog signala. Dana je formalna matematička definicija ESN mreže s postupkom treniranja koji jamči stabilnost modela u smislu ograničenog izlaznog signala uz ograničeni ulazni signal (eng. bounded-input bounded-output, BIBO). Postupci za treniranje i verifikaciju ESN mreža sa slučajno odabranim povratnim vezama u skrivenom sloju koji omogućuju modeliranje općenitih vremenskih nizova prilagođeni su radi modeliranja naponskih i strujnih signala u vremenskoj domeni dobivenih simulacijama integriranih sklopova. Dana je iterativna metoda za ručno odabiranje hiper-parametara ESN mreže, uz smjernice o utjecaju pojedinog hiper-parametra na svojstva mreže.

Predstavljen je adaptivni algoritam za uzorkovanje nelinearnog ponašanja sklopova u domeni definiranoj frekvencijom i snagom smetnje koji omogućuje izgradnju skupa podataka za treniranje ESN mreže. Algoritam smješta više uzoraka u područje rada sklopa s većom nelinearnošću modeliranih valnih oblika te izbjegava nedovoljno uzorkovanje linearnog područja rada. Uvode se dva kriterija za zaustavljanje algoritma, jedan temeljen na unaprijed određenom broju uzoraka i jedan temeljen na Spearmanovoj korelaciji uzastopnih dvodimenzionalnih interpolatora skalarne funkcije nad zadanom domenom.

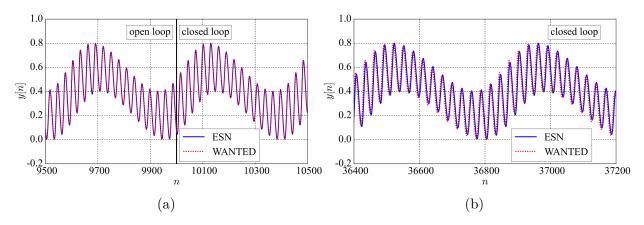

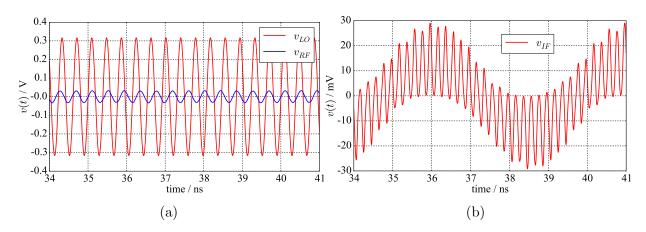

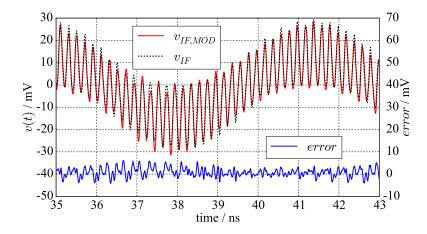

ESN mreža implementirana je u jeziku Verilog A, jeziku za opisivanje sklopovlja (eng. hardware description language, HDL), čime je omogućeno korištenje ESN mreža u komercijalnim sklopovskim simulatorima. Predstavljena metodologija za modeliranje ponašanja integriranih sklopova primijenjena je na pet praktičnih sklopova iz poluvodičke industrije: naponsko sljedilo, upravljački sklop prekidačkog izvora napajanja (eng. DC-DC converter), LIN sučelje, matematički oscilator s povratnom vezom te radiofrekvencijsko mješalo frekvencija (eng. RF mixer). Dobiveni rezultati pokazuju primjenjivost ESN mreža na modeliranje širokog raspona nelinearnog ponašanja opaženog u simulacijama integriranih sklopova. U ova ponašanja uključeni su efekti memorije sklopova, gdje su izlazni signali zakašnjeli u odnosu na ulazne signale za do tisuću vremenskih uzoraka te efekti sklopova koji sadrže dvije vrlo razmaknute vremenske konstante.

Usporedbom modela koji se temelji na ESN mreži s referentnim modelom temeljenim na RNN mreži pokazano je kako ESN mreža ostvaruje usporedivu preciznost izraženu pomoću mjere MSE (eng. mean square error), pri čemu se omogućuje korištenje bržeg i jednostavnijeg postupka treniranja i jamči stabilnost modela. Svojstva uopćavanja (eng. generalization) ESN mreža ograničena su na interpolaciju između podataka za treniranje unutar zadane domene te na ispravan odziv na trenirane ulazne signale na koje je dodan aditivni bijeli šum. U odnosu na tranzistorske modele s ekstrahiranim parazitnim elementima, ESN mreže postižu koeficijente ubrzanja sklopovskih simulacija do 77 puta. Vrijeme izvođenja sklopovskih simulacija s ESN modelima manje je ovisno o harmoničkoj distorziji modeliranih valnih oblika u vremenskoj domeni u odnosu na tranzistorske sklopove.

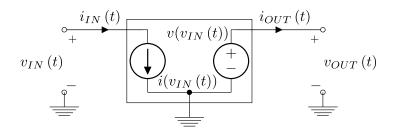

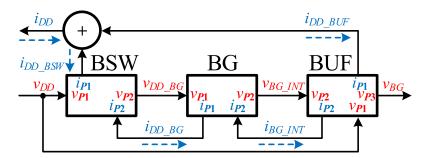

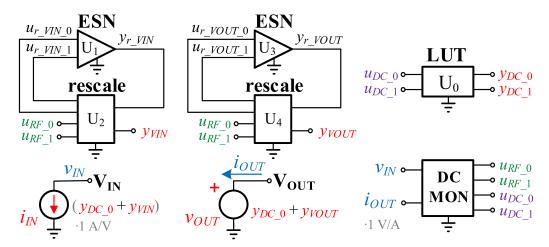

Predstavljena je arhitektura modela nelinearne impedancije temeljena na zavisnim naponskim i strujnim izvorima. Uvođenjem ESN mreže u modeliranje nelinearne impedancije omogućuje se izgradnja ponašajnih modela integriranih sklopova koji mogu zamijeniti tranzistorske modele, stoga se ovakvi ponašajni modeli nazivaju zamjenjivim modelima (eng. interchangeable models). Dana je metodologija za analizu toka signala integriranog sklopa, pri čemu su naponski i strujni signali svakog prolaza (eng. port) modeliranog sklopa podijeljeni u ulazne i izlazne signale ESN mreže. Ispitana su svojstva komercijalnih sklopovskih simulatora obzirom na izvršavanje simulacija otpornosti sklopova na vođene smetnje (eng. conducted immunity simulations), s naglaskom na simuliranje ponašanja u ustaljenom stanju (eng. steady-state) u vremenskoj domeni.

Arhitektura ponašajnog modela proširena je radi omogućavanja neovisnog modeliranja statičkog (eng. direct current, DC) i radiofrekvencijskog (eng. radio-frequency, RF)

ponašanja modeliranog sklopa radi pojednostavljivanja postupka treniranja ESN mreže.

Uvodi se blok za opažanje (eng. monitor) DC signala koji omogućuje odvajanje DC i

RF komponenti naponskih valnih oblika u vremenskoj domeni. Dana je implementacija

proširenog modela u jeziku Verilog A koja omogućuje korištenje modela u DC simulacijama

te u tranzijentnim simulacijama koje započinju iz početnog uvjeta zadanog datotekom.

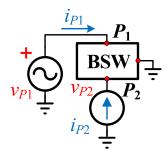

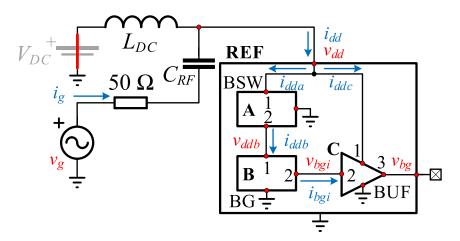

Predstavljeno je okruženje za simulacije otpornosti na vođene smetnje (eng. conducted immunity simulation environment), koje je primijenjeno na sklop naponske reference s odvojnim stupnjem (eng. buffered voltage reference circuit) iz postojećeg poluvodičkog proizvoda na tržištu. Odnosi između RF napona i RF struja u simulacijskom okruženju opisani su dijagramima toka svakog modeliranog podsklopa.

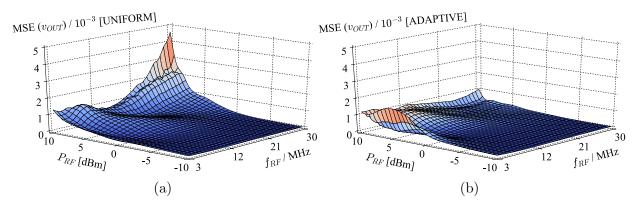

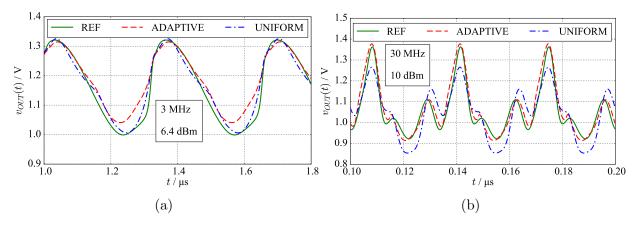

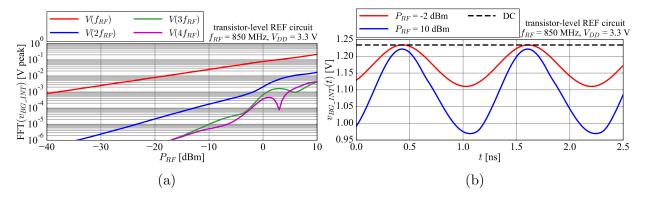

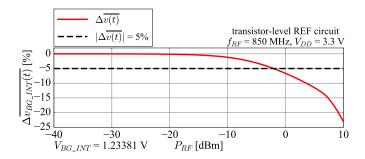

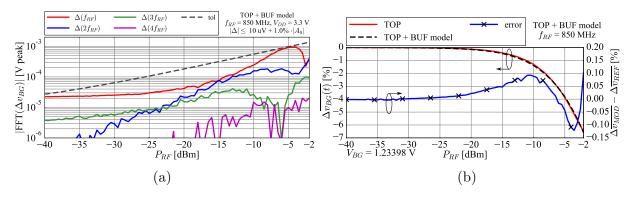

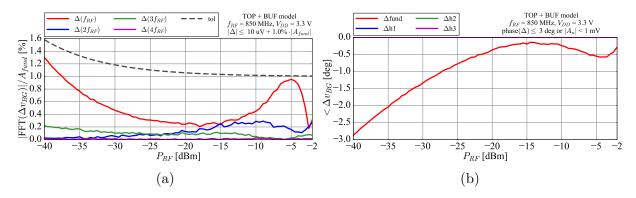

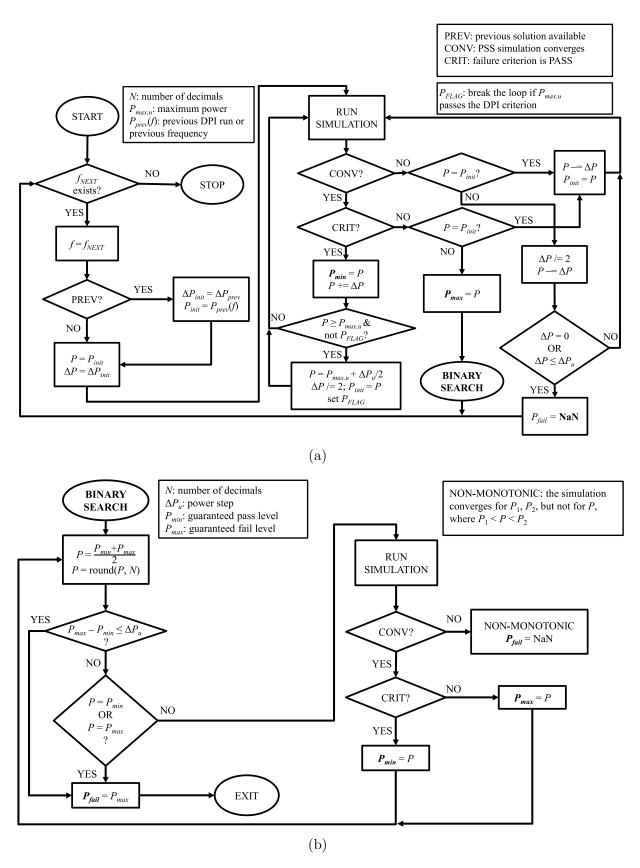

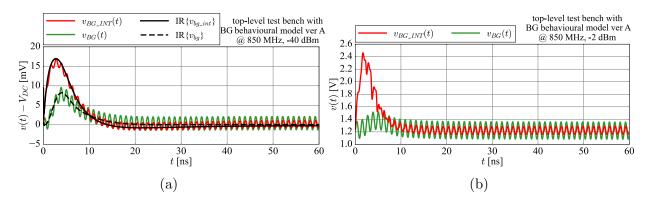

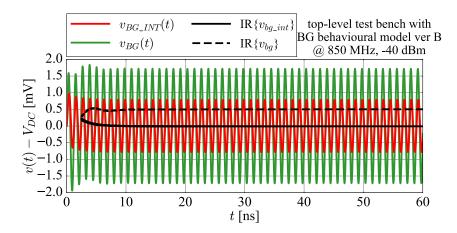

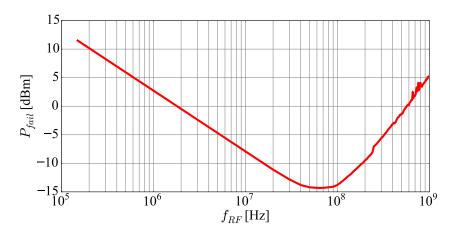

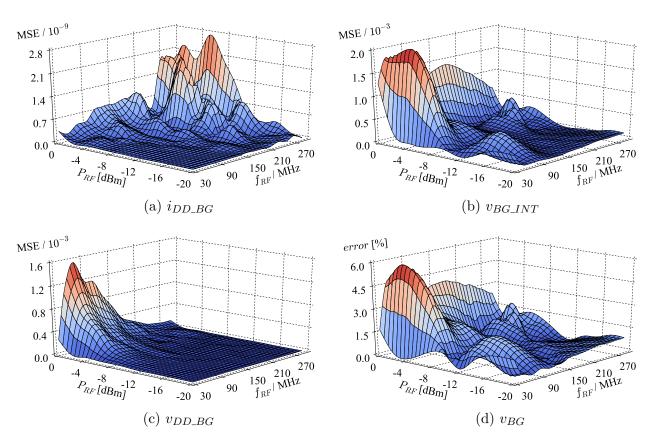

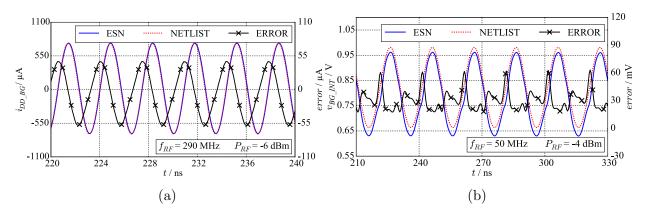

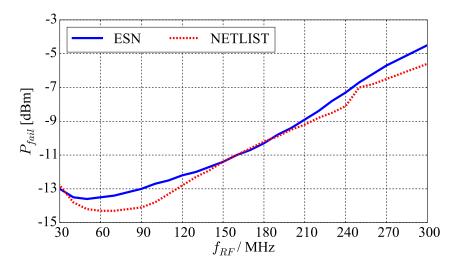

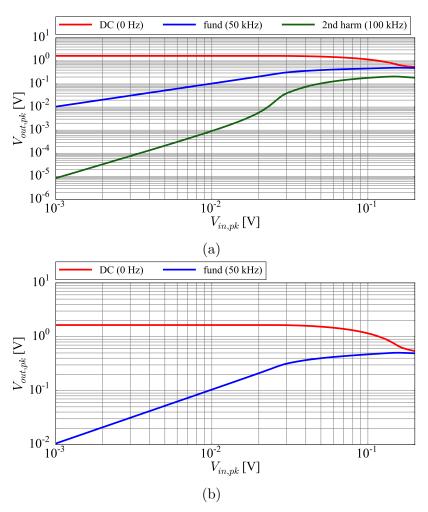

U navedenim simulacijama opažaju se dva dominantna nelinearna efekta: (i) harmonička distorzija RF signala (eng. RF harmonic distortion), (ii) pomak statičke radne točke uzrokovan RF smetnjom (eng. RF-induced DC-shift). Uvodi se metodologija za određivanje preciznosti ponašajnog modela temeljena na usporedbi svojstava vremenskih valnih oblika u frekvencijskoj domeni. Ova metodologija omogućuje tabličnu usporedbu ponašanja sklopova u simulacijskom okruženju gdje su jedan ili više podsklopova zamijenjeni ponašajnim modelom, omogućujući pregledan prikaz ponašanja niza RF napona i RF struja u više sklopovskih varijanti, u ovisnosti o frekvenciji i snazi RF smetnje. Predstavljen je algoritam za provođenje simulacija otpornosti na vođene smetnje prema standardu DPI (eng. direct power injection) kojim se minimizira potreban broj simulacija za određivanje DPI karakteristike metodom pretraživanja pomoću binarnog stabla.

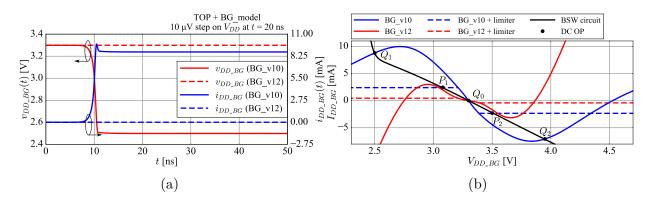

Stabilnost ponašajnih modela u okruženju za simulacije otpornosti sklopova na vođene smetnje analizira se kroz tri aspekta: meta-stabilnost statičke radne točke, stabilnost u uvjetima malog signala te stabilnost početnog tranzijenta. Dana je poveznica između meta-stabilnosti i DC svojstava ESN modela izvan treniranog DC područja rada.

Izveden je dovoljan uvjet za meta-stabilnost zadanog ponašajnog modela. Uvodi se uvjet ravnoteže RF struja modeliranog sklopa te je dan primjer implicitnih veza između podsklopova kroz podlogu silicijske pločice. Razvijen je okvir za analizu interakcije između ESN mreža definiranih u disktrenoj vremenskoj domeni i tranzistorskih sklopova definiranih u kontinuiranoj vremenskoj domeni te je predstavljena metodologija za određivanje karakteristika ponašajnih modela u uvjetima malog signala.

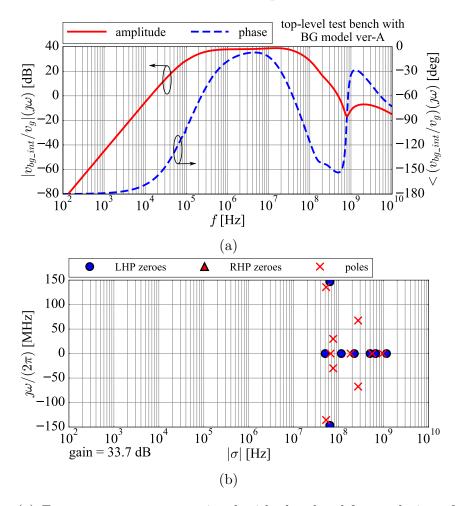

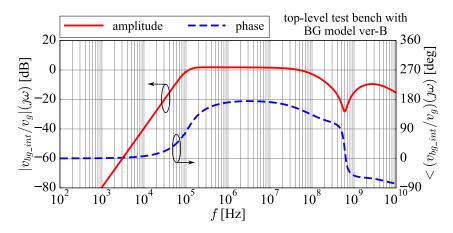

Rješenja lineariziranih jednadžbi koja određuju frekvencijski odziv naponske reference s odvojnim stupnjem u uvjetima malog signala izvedena su na temelju frekvencijskih odziva pojedinih podsklopova. Stabilnost ponašajnog modela u ukupnom sklopu povezana je sa svojstvima modela izvan treniranog frekvencijskog područja. Dana je poveznica između početnih tranzijenata ponašajnih modela prije dostizanja ustaljenog stanja i impulsnog odziva pojedinih naponskih perturbacija u simulacijskoj shemi te koeficijenata trenirane ESN mreže u matrici izlaznih težinskih faktora.

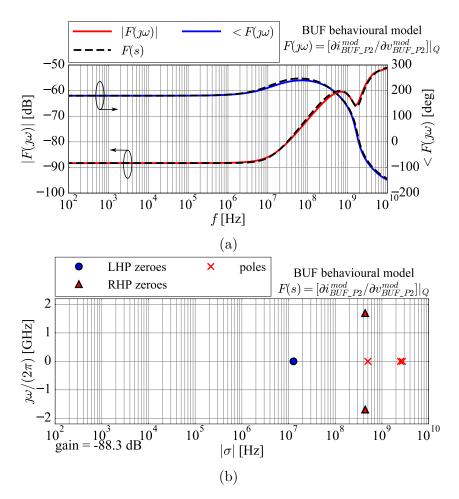

Predstavljena je instanca ponašajnog modela odvojnog stupnja (eng. buffer) koja je stabilna kao zasebni element u BIBO smislu, ali unosi nestabilne polove u ukupni sklop u simulacijskoj shemi koja sadrži druge tranzistorske sklopove, zbog čega simulacija divergira. Izvedena je poveznica između frekvencijskih odziva ponašajnog modela i nestabilnih polova naponskih perturbacija u ukupnom sklopu.

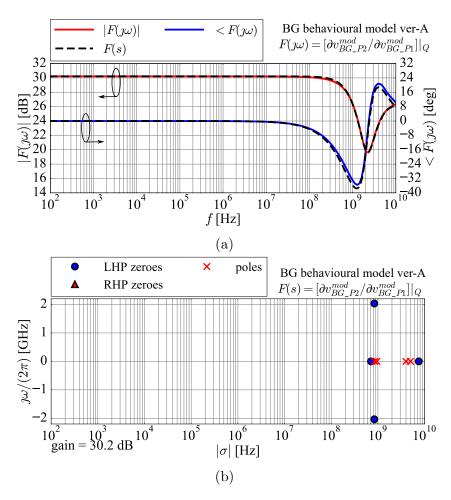

Predstavljena je instanca ponašajnog modela naponske reference (eng. bandgap) koja je stabilna i kao zasebni element u BIBO smislu, i kao dio ukupnog sklopa u simulacijskoj shemi koja sadrži druge tranzistorske sklopove, ali unosi značajna nadvišenja u vremenskom odzivu napona pojedinih čvorova u shemi. Umjetna naponska nadvišenja mogu dovesti tranzistorske sklopove u područje rada za koje ponašajni model nije treniran. Izvedena je poveznica između naponskih nadvišenja i impulsnog odziva pridružene naponske perturbacije te svojstava trenirane ESN mreže.

Predstavljena je instanca ponašajnog modela naponske reference za DPI simulacije sklopa naponske reference s odvojnim stupnjem u frekvencijskom području od 30 MHz do 300 MHz pri RF snagama između -20 dBm i 0 dBm. Preciznost modela izražena je mjerom MSE i usporediva je s rezultatima dostupnima u literaturi.

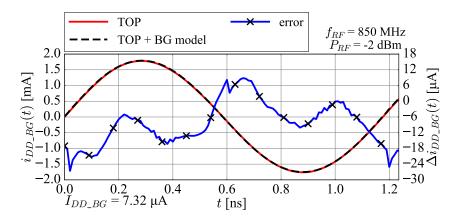

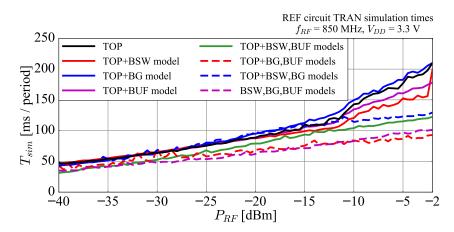

Vrijeme izvršavanja ponašajnog modela u sklopovskoj simulaciji manje je ovisno o snazi RF smetnje u odnosu na tranzisorske sklopove. DPI karakteristika sklopa gdje je naponska referenca zamijenjena ponašajnim modelom nalazi se unutar 1 dB od DPI karakteristike tranzistorskog sklopa. Uskopojasni zamjenjivi ponašajni modeli svih triju podsklopova naponske reference s odvojnim stupnjem modeliraju rad sklopa na frekvenciji od 850 MHz pri snagama RF smetnje od -40 dBm do -2 dBm. Tri ponašajna modela ispitana su predstavljenom metodom za određivanje preciznosti modela te ispravno opterećuju tranzistorske sklopove koji su s njima spojeni.

Arhitektura modela nelinearne impedancije također omogućuje međusobno spajanje dvaju ponašajnih modela koji koriste međusobno dualne topologije modela. Pokazano je kako sva tri ponašajna modela ispravno opterećuju druge ponašajne modele u simulacijskom okruženju. Postignuti su koeficijenti ubrzanja simulacija do dva puta.

Dane su smjernice za nastavak istraživanja ponašajnog modeliranja. Jedan smjer istraživanja odnosi se na modeliranje naponske reference s odvojnim stupnjem koje u obzir uzima opterećenje odvojnog stupnja, koje zahtijeva skaliranje ponašajnih modela na više od dva ulazna signala. Drugi mogući smjer istraživanja odnosi se na modeliranje integriranih sklopova koji uz signale uzrokovane RF smetnjom sadrže i vremenski promjenljive funkcionalne signale niske frekvencije.

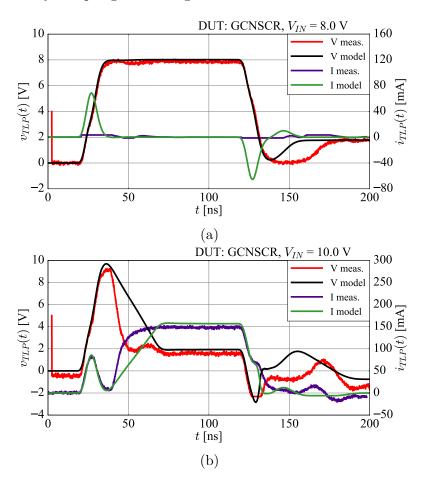

Predstavljena je mjerna metoda pulsiranja prijenosne linije (eng. transmission line pulsing, TLP) te je izveden model TLP generatora s pasivnim i distribuiranim elementima. Ponašajni model silicijski upravljanog ispravljača spregnutog s upravljačkom elektrodom n-kanalnog MOS tranzistora (eng. gate-coupled NMOS silicon-controlled rectifier, GCNSCR), elementa za zaštitu od elektrostatskih izboja (eng. electrostatic discharge, ESD) izgrađen je na temelju podataka dobivenih TLP mjerenjima. Budući da negativni dinamički otpor (eng. snapback) nije uključen u većinu biblioteka sklopovskih modela, ponašajni model GCNSCR elementa implementiran u jeziku Verilog A omogućuje izvršavanje TLP simulacija u vremenskoj domeni. Model ispravno modelira ponašanje elementa tijekom kvazistacionarnog stanja TLP impulsa u oba stanja provodljivosti (eng. off-state, on-state). Predstavljena metoda omogućuje izgradnju brzih i preciznih modela ESD elemenata s negativnim dinamičkim otporom u simulacijskom okruženju za TLP metodu.

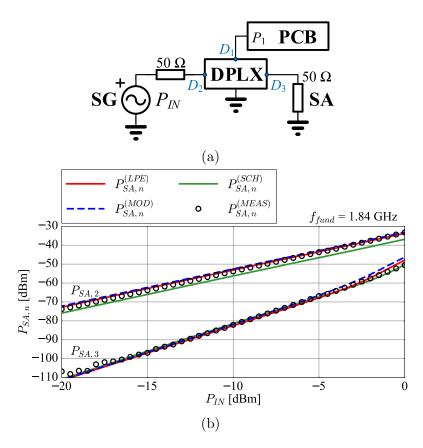

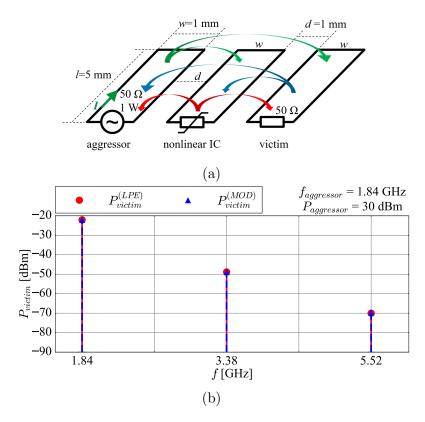

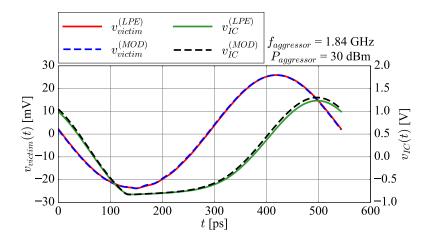

Predstavljen je efekt reradijacije radiofrekvencijskog signala zbog harmoničke distorzije nelinearnih integriranih sklopova u magnetski spregnutom sustavu. Uzrok harmoničke distorzije povezan je s naponski ovisnim dinamičkim otporom i kapacitetom stezaljki za I2C komunikaciju. Predstavljena je metoda za određivanje naponski ovisnih vrijednosti pomoću simulacija u uvjetima malog signala (eng. AC simulations). Pomoću dobivenih karakteristika izgrađen je ponašajni model za simulaciju harmoničke distorzije. Ponašajni model se uspoređuje s mjerenjima metodom dipleksera (eng. diplexer).

Ponašajni modeli postižu koeficijente ubrzanja simulacija do 115 puta u odnosu na korištenje tranzistorskih sklopova s ekstrahiranim parazitnim elementima. Predstavljen je magnetski spregnut sustav koji se sastoji agresorske antene koja radi na 1.84 GHz, antene žrtve koja radi u WiFi pojasu na 5 GHz te od nelinearnog integriranog sklopa. Integrirani sklop prima RF smetnju koju generira agresorska antena te se na stezaljci sklopa zbog nelinearne distorzije generira treća harmonička frekvencija koja se reradijacijom šalje prema anteni žrtvi. Ponašajni model omogućuje uključivanje nelinearnog integriranog sklopa u radiofrekvencijsko simulacijsko okruženje.

Izvorni znanstveni doprinos sastoji se od tri komponente:

- 1. Metoda modeliranja nelinearnih sklopova u uvjetima velikog signala pomoću ESN mreža (eng. *echo state network*).

- 2. Adaptivni algoritam za odabir uzoraka nelinearnog ponašanja sklopova u vremenskoj domeni.

- 3. Metoda modeliranja nelinearne impedancije pomoću zavisnih izvora radi me đusobnog spajanja ponašajnih modela i spajanja s drugim sklopovima.

**Ključni pojmovi**: elektromagnetska kompatibilnost, ponašajno modeliranje, ESN mreže (eng. echo state networks), model nelinearne impedancije, analiza stabilnosti, DPI (eng. direct power injection), umjetne neuronske mreže, bandgap referenca, ubrzanje simulacija, adaptivno uzorkovanje, otpornost na vođene smetnje

# Contents

| 1. | Intro | oductio   | <b>n</b>                                                               |

|----|-------|-----------|------------------------------------------------------------------------|

|    | 1.1.  | Behav     | ioural modelling research area overview                                |

|    | 1.2.  | Overv     | iew of the performed research                                          |

|    | 1.3.  | Origin    | al scientific contribution                                             |

|    | 1.4.  | Thesis    | outline                                                                |

| 2. | Mod   | lelling l | arge-signal nonlinear circuit behaviour using echo state networks . 10 |

|    | 2.1.  | Motiva    | ation                                                                  |

|    | 2.2.  | Echo s    | state networks                                                         |

|    |       | 2.2.1.    | ESN definition in the discrete time-domain                             |

|    |       | 2.2.2.    | ESN training and verification procedures                               |

|    | 2.3.  | Metho     | d for modelling circuit time-domain behaviour                          |

|    |       | 2.3.1.    | ESN hyper-parameter selection                                          |

|    |       | 2.3.2.    | Adaptive algorithm for sampling nonlinear circuit behaviour19          |

|    |       | 2.3.3.    | Hardware description language implementation of the ESN                |

|    | 2.4.  | Model     | ling results                                                           |

|    |       | 2.4.1.    | Test case 1: Voltage follower                                          |

|    |       | 2.4.2.    | Test case 2: DC-DC driver IC                                           |

|    |       | 2.4.3.    | Test case 3: LIN interface                                             |

|    |       | 2.4.4.    | Test case 4: Oscillator with feedback                                  |

|    |       | 2.4.5.    | Test case 5: RF mixer                                                  |

|    | 2.5.  | Discus    | sion                                                                   |

|    | 2.6.  | Summ      | ary                                                                    |

| 3. | Non   | linear i  | mpedance model for behavioural model interconnectivity                 |

|    | 3.1.  | Motiva    | ation                                                                  |

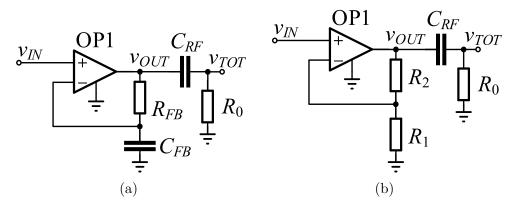

|    | 3.2.  | Intercl   | nangeable behavioural model architecture                               |

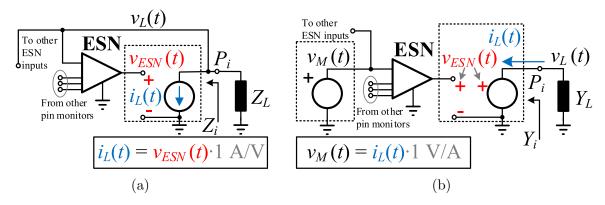

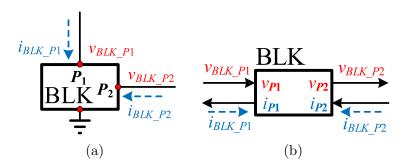

|    |       | 3.2.1.    | Nonlinear impedance model based on controlled sources                  |

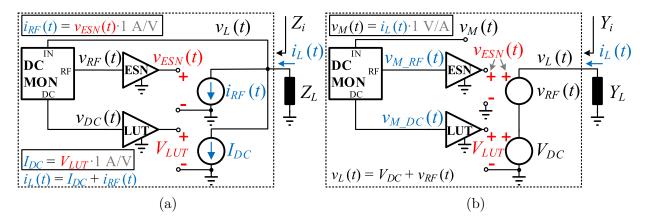

|    |       | 3.2.2.    | Separating the DC and RF sub-models                                    |

| 3.3.    | Conducted immunity simulation environment                                   |

|---------|-----------------------------------------------------------------------------|

|         | 3.3.1. Buffered voltage reference in the top-level test bench               |

|         | 3.3.2. Nonlinear effects in conducted immunity simulations                  |

|         | 3.3.3. Evaluating time-domain waveform modelling accuracy                   |

|         | 3.3.4. Simulating the Direct RF Power Injection (DPI) standard53            |

| 3.4.    | Beahvioural model stability analysis                                        |

|         | 3.4.1. DC operating point stability                                         |

|         | 3.4.2. Implicit substrate connections                                       |

|         | 3.4.3. Discrete-time system stability analysis                              |

|         | 3.4.4. Small-signal stability                                               |

|         | 3.4.5. Initial transient stability                                          |

| 3.5.    | Behavioural modelling results                                               |

|         | 3.5.1. Test case 1: Behavioural model of the bandgap circuit                |

|         | 3.5.2. Test case 2: Models of buffered voltage reference subcircuits75      |

|         | 3.5.3. Test case 3: Connecting multiple behavioural models                  |

| 3.6.    | Discussion                                                                  |

| 3.7.    | Summary                                                                     |

| l. Beh  | avioural modelling in ESD and EMC applications                              |

| 4.1.    | Motivation                                                                  |

| 4.2.    | Transmission line pulse modelling                                           |

|         | 4.2.1. TLP simulation environment                                           |

|         | 4.2.2. Test case: Behavioural model of a GCNSCR exhibiting snapback.88      |

| 4.3.    | RF harmonic distortion modelling                                            |

|         | 4.3.1. Voltage-dependent RC elements                                        |

|         | 4.3.2. RF harmonic distortion simulation environment                        |

|         | 4.3.3. Test case: Re-radiation in a magnetically coupled wireless system.95 |

| 4.4.    | Summary                                                                     |

| 6. Con  | clusion                                                                     |

| Bibliog | raphy 103                                                                   |

| List of | abbreviations                                                               |

|         |                                                                             |

| List of | figures                                                                     |

| A.  | Behavioural model architecture in the hardware description language Verilog A $123$ |

|-----|-------------------------------------------------------------------------------------|

|     | A.1. Interchangeable behavioural model in Verilog A                                 |

|     | A.2. Look-up table sub-model in Verilog A                                           |

|     | A.3. Echo state network sub-model in Verilog A                                      |

|     | A.4. Rescaling block in Verilog A                                                   |

| В.  | Buffered voltage reference small-signal modelling                                   |

|     | B.1. Small-signal transfer function convention                                      |

|     | B.2. Small-signal model of the transistor-level bulk switch circuit                 |

|     | B.3. Small-signal model of the transistor-level output buffer                       |

|     | B.4. Small-signal model of the transistor-level bandgap block                       |

|     | B.5. Small-signal model of the bias-tee                                             |

|     | B.6. Small-signal model of the top-level test bench                                 |

| C.  | Simulations of the DPI injection into the output pin of an amplifier 159            |

|     | C.1. Output reflection coefficient in the time-domain                               |

|     | C.2. Functional simulations                                                         |

|     | C.3. Influence of RF phase on the output reflection coefficient                     |

|     | C.4. DPI simulations                                                                |

|     | C.5. Discussion                                                                     |

| D.  | Determining discrete-time system poles                                              |

|     | D.1. The Cauchy integral                                                            |

|     | D.2. Pole optimization problem                                                      |

|     | D.3. Test case: second-order bandpass filter                                        |

| Bio | ography                                                                             |

| Živ | votopis                                                                             |

# Chapter 1

# Introduction

The complexity of integrated circuits (IC) is growing rapidly, and electromagnetic compatibility (EMC) aware design has become the norm in the IC industry. Being able to simulate EMC behaviour of IC blocks in the design phase reduces the design cost and shortens the time-to-market. The need for more time- and memory-efficient IC models has made behavioural modelling an active research area in recent years [1–7]. In the behavioural modelling approach, the model is built using only the input-output behaviour of the modelled system, without any information about its inner physical structure, enabling model order reduction (MOR), simulation speed-up, and intellectual property (IP) protection. Different methods refer to behavioural models as macromodels [8], [9], empirical models [10], and surrogates [11].

ICs are nonlinear systems with memory, as the outputs are nonlinear transforms of the inputs and their previous values or "system history". Most behavioural modelling methods capture the system history by feeding the input and/or output signals through a delay line. Choosing the number and value of the delays is computationally expensive, involves case-specific knowledge of the modelled circuit, and often does not guarantee stability.

Recurrent neural networks (RNN) are artificial neural networks (ANN) that capture the system history using internal feedback connections between the neurons in one or more hidden layers. The main drawback of using RNNs for behavioural modelling is often slow training algorithms based on gradient descent [12], [13].

The thesis presents the study on building interchangeable behavioural models of ICs for conducted immunity simulations based on echo state networks (ESN) in combination with look-up tables and S-parameters. An ESN is a type of RNN with a very fast training procedure and guaranteed model stability [13].

The chapter is organized as follows. Section 1.1 presents an overview of the research area. Section 1.2 introduces the performed research with the original scientific contributions given in Section 1.3, and Section 1.4 presents the outline of the thesis.

# 1.1 Behavioural modelling research area overview

An artificial neural network (ANN) is a behavioural model consisting of interconnected units or neurons. Each neuron is associated with an activation, a signal in the discrete time-domain that evolves based on the interaction of a neuron with other neurons in the network. The ANN activations are trained to mimic the complex relationships between the input and output signals of the modelled system in the time-domain using the training algorithms that define the connections between the neurons to fit the training data.

Many software packages for generating, training, and testing ANNs are readily available, e.g. the Neural Network Toolbox<sup>™</sup> in MATLAB<sup>®</sup> [14]. In the computer science area, ANNs are evaluated using standard benchmark time-series prediction test cases, such as a 2nd order dynamical system [12], the NARMA series [15], or the Mackey-Glass chaotic series [13], [16], [17]. The network sizes used for these benchmark test cases are in the order of several hundred neurons [13].

ANNs are already successfully used in a variety of applications, e.g. model predictive control [18], active shunt power filters [19], [20], biomedical applications [21]. In the area of integrated circuit modelling, a 3-layer feedforward neural network is presented in [22] that models the response of a digital IC to a radio-frequency (RF) disturbance on its supply pin. The model is implemented in the circuit simulator as a mathematical expression. In [6], the model of an output buffer of a digital IC is built for signal integrity simulations. A combination of feedforward ANNs and recurrent neural networks (RNN) is used. Single-layer feedforward neural networks (SLFN) with 4 neurons are used to model the IV-characteristics of the buffer transistors, and the total buffer output current is modelled by weighting the currents of the output transistors, where the weights are implemented as recurrent neural networks with 10 neurons each. This model overcomes the limitation of using the I/O buffer information specification (IBIS) [23] that cannot properly model analog nonlinear behaviour, such as ringing and attenuation.

Most ANN training algorithms train all connections in the network using methods based on gradient descent, which often have slow convergence or do not converge at all, e.g. due to bifurcations during training [13], [24]. The echo state network (ESN) is a specific type of RNN introduced in [13], where the network is trained by generating random recurrent connections in the hidden layer, and by performing linear regression only on the weights of the readout layer. This approach makes the ESN training procedure computationally efficient and robust, while retaining the desirable properties of RNNs. The ESN models can be implemented in any hardware description language (HDL) for analog and/or mixed signals, e.g. Verilog A, VHDL-AMS, MAST [25]. The HDL implementation of ESN models makes them directly usable in commercial circuit simulators, such as Cadence<sup>®</sup> Spectre<sup>®</sup> and Mentor Graphics<sup>®</sup> Eldo.

The ESN is also used in a variety of modelling applications. In [1], the ESN model with 56 neurons is used for time-series prediction of the temperature in a hot blast stove system. In the power grid area, behavioural modelling is applied to build models of photovoltaic inverters [2] and electric vehicle battery chargers [3]. In the power electronics area, behavioural models of gallium nitride (GaN) transistors and their gate drivers are built [4], [26]. In [18] neural networks are used for the model predictive control (MPC) of an unknown nonlinear system. The ESN is used for system identification, and the control problem is formulated as a quadratic programming (QP) problem that is solved using a simplified dual neural network (SDN) with a single layer.

In [19] and [20], the ESN is used in a harmonic extraction block of a shunt active power filter (SAPF), that eliminates the higher harmonics from the output current caused by nonlinear loads in power systems. The ESN is used to extract the fundamental component of the load current. Although 100 neurons are used in [19], it is shown in [20] that an ESN with only 30 neurons is sufficient to achieve similar model accuracy, that is superior to a feedforward neural network, referred to as the multilayer perceptron (MLP). In [9] an ESN model with 30 neurons models the output current of a digital circuit as a function of the port voltage for signal integrity simulations, capturing the nonlinear RF voltage and RF current relationships observed in simulations of IC blocks.

Methodologies such as [8] are suitable for modelling circuits that operate in a small signal linear regime, while the methods such as [9], [10] model the nonlinear dependence of the currents flowing into the pins of transceiver driver circuits on the independently set voltage excitation signals. Several approaches to modelling the nonlinear behaviour of IC blocks, particularly in RF frequency bands, are presented in literature. In [3], an electric vehicle battery charger is modelled using a nonlinear model that covers different operating points by switching between several linear models. In [4], a GaN transistor gate driver is modelled by capturing the linear behaviour using IV-curves, and by capturing the nonlinear capacitance behaviour using CV-curves. In [26], the S-parameters of a GaN transistor are used to build a nonlinear model based on support vector machines (SVM). In addition to behavioural models built from simulations, behavioural models are also derived from measurements [5], [27].

In the EMC area, the RF immunity and RF emission of integrated circuits is typically measured according to standards, and root cause analysis requires recreating the measured behaviour in circuit simulations. Direct power injection (DPI) is an electromagnetic interference (EMI) conducted immunity test for integrated circuits, defined in the IEC-62132-4 standard [28]. The RF disturbance in the range between 150 kHz and 1 GHz is injected into the pin of the device-under-test (DUT) and the RF forward power is increased until the functionality of the circuit fails according to a failure criterion. It is practice during

the product development phase to run narrow-band simulations of the DPI test bench containing the transistor-level blocks at system-critical frequencies, in order to observe the RF behaviour of the circuit and to improve its conducted immunity using circuit techniques or filtering. A full electrical model of the DPI measurement setup is presented in [29], including the models of the IC package, the printed circuit board (PCB), the injection probe, and the decoupling capacitors.

The main bottleneck in the conducted immunity simulations of integrated circuits is the simulation time that increases with RF forward power levels due to the transistor-level model of the IC that is operating in an increasingly nonlinear regime. Additionally, the slow process of converging to the steady-state due to the large internal time constants of the transistor-level circuits results in long simulation times before reaching the steady-state operation.

The nonlinear modelling approaches such as [9], [10] are only valid if the RF voltage is known. The challenge in building models for DPI simulations is that the exact amplitude of the RF voltage injected into the DUT depends on the nonlinear input impedance seen looking into the DUT pin under test, and it is not known upfront [11], [28].

This issue is addressed in [11], where a behavioural model of a voltage regulator integrated circuit is built to improve the simulation time of the DPI harmonic balance simulations. The behavioural model, referred to as a surrogate, is based on a feed-forward neural network (FFNN) with two hidden layers implemented as an analytical expression. In order to properly load the DPI injection network consisting of a 50- $\Omega$  RF generator and a bias-tee, two FFNN models generate the numerical value of the DC resistance  $R_{IN}$  and the complex-valued small-signal impedance  $Z_{IN}$  as functions of the numerical values of the frequency and the amplitude of the RF disturbance voltage seen at the input pin. This enables the harmonic balance simulator to find the correct solution for the RF voltage amplitude seen at the pin of the modelled IC. A third FFNN model generates the DC value of the output voltage as a function of the same two input variables using an ideal DC voltage source. The training time is in the order of 5 hours, slowing down the process of optimising the hyper-parameters of the model [11].

The behavioural modelling methodologies presented in literature include an implicit or explicit step of design space sampling to obtain the training dataset for building the model. Several adaptive sampling algorithms are evaluated in [30], which combine the exploration sampling strategy that aims at uniformly sampling of the design space, and the exploitation strategy that aims at choosing more samples in the areas where the model accuracy is lower. The LOLA-Voronoi algorithm, introduced in [31], combines both sampling strategies, and it is shown to be superior to random sampling in the case of modelling the input noise current of a low noise amplifier (LNA). In [32], the LOLA-Voronoi algorithm is presented in literature include an implicit and implicit an implic

rithm is used in a metamaterial geometry optimisation method to significantly reduce the required computing time by limiting the size of the dataset. In [11], the training dataset is obtained by sampling the RF design space defined by the RF frequency and RF forward power using the LOLA-Voronoi algorithm, in order to put more focus on the more nonlinear regions of the design space, where the circuit functionality starts to fail.

The original research presented in this thesis is performed within the context of the behavioural modelling of nonlinear effects in integrated circuits. The research is focused on building behavioural models of integrated circuits derived from circuit simulation data, which are able to correctly load the transistor-level circuits in the time-domain simulations.

The modelling approach introduced in [11] models the DC resistance and the small-signal impedance of the modelled circuit, and it is appropriate for the loading of linear networks, such as the DPI injection network. In order to enable the loading of other transistor-level circuits, the approach in [11] is modified in three ways. Firstly, the nonlinear input impedance is modelled using recurrent neural networks instead of feed-forward neural networks, in order to enable modelling the nonlinear and memory properties of the IC impedances. Secondly, instead of modelling the impedance components (i.e. the DC resistance R and the small-signal impedance Z) as functions of the RF frequency and RF amplitude, the time-domain waveform of the RF input current is modelled as a function of the RF input voltage. Thirdly, the model of the output voltage in [11] is extended to include the output impedance instead of an ideal voltage source.

# 1.2 Overview of the performed research

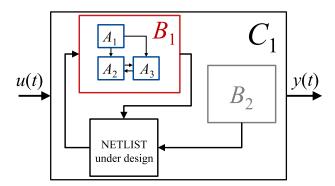

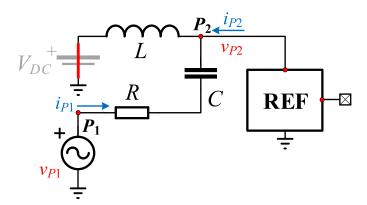

Figure 1.1: The interchangeable behavioural modelling concept presented on an example simulation test bench with three hierarchical levels A, B, C.

A behavioural model is interchangeable if the time-domain voltages and currents at the pins of the modelled transistor-level circuit remain unchanged when the modelled circuit is replaced by the behavioural model. Fig.1.1presents an example simulation test bench with three hierarchical levels labelled as A, B, C. The circuit  $C_1$  consists of three interconnected subcircuits:  $B_1$ ,  $B_2$ , and a netlist under design. The subcircuit  $B_1$  represents a power management circuit that provides the supply voltage to the netlist under design. The subcircuit  $B_1$  consists of three interconnected subcircuits  $A_1$ ,  $A_2$ ,  $A_3$ . The top-level circuit  $C_1$  is simulated in the conducted immunity simulation test bench, where the RF interference signal u(t) is injected into the  $C_1$  supply pin, and its effect on the  $C_1$  output signal u(t) is observed within the RF design space defined by the frequency and amplitude of the RF interference.

Since the conducted immunity simulations of power management circuits can be very slow [11], the iterative process of implementing EMC-aware design techniques into the netlist under design becomes time-consuming, increasing the product development costs and the time-to-market. In order to speed-up the conducted immunity simulations, the power management circuit  $B_1$  is replaced by an interchangeable behavioural model that replicates the behaviour of the modelled circuit  $B_1$  under the given RF interference injection conditions and also reduces the complexity of the simulation test bench. The model of  $B_1$  is built by connecting the behavioural models of its three subcircuits  $A_1$ ,  $A_2$ ,  $A_3$ .

The topic of the research presented in this thesis is the methodology for building interchangeable behavioural models that are used in the conducted immunity simulation environment. The models are able to correctly load the connected transistor-level circuits or other behavioural models by modelling the nonlinear impedance seen at the input and output pins of the modelled circuit. Due to the favourable properties presented in Section1.1, most importantly the fast training time of the model, the echo state network is chosen as the basis for the proposed behavioural modelling approach.

A Python library is developed that includes the tools required to perform the research. The Python module for generating and training ESN models is based on [13]. The Python module includes a Verilog A code generator that enables the use of the ESN models in the Cadence® Spectre® circuit simulator. The circuit simulations are run using the Python module that controls the circuit simulator, and enables sweeping the values of the RF frequency and RF forward power variables in the simulation. The resulting simulation outputs, consisting of DC values, time-domain waveforms, frequency domain spectra, and meta-data such as log files, are stored using [33] into SQL databases that are searchable by the RF frequency and RF forward power parameters for data post-processing.

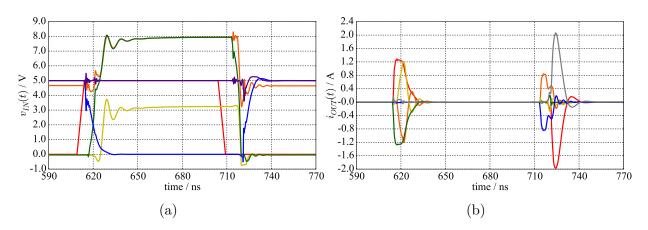

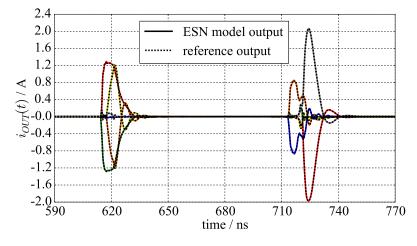

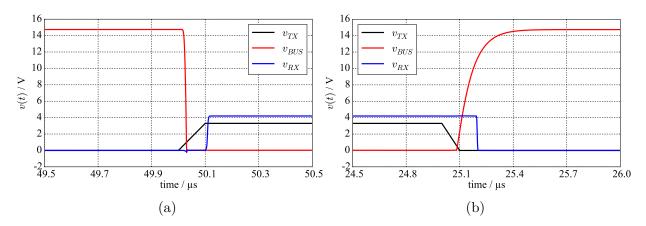

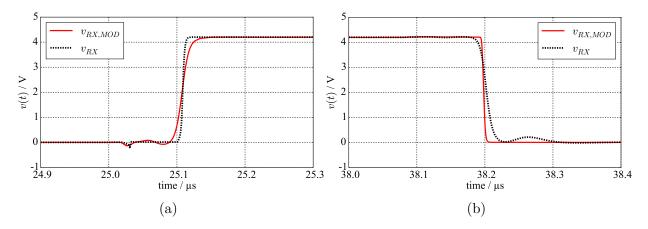

The nonlinear and memory effects observed in the simulations of a range of integrated circuits are investigated. In [34], the ESN is applied to the modelling of the time-domain responses of a DC-DC driver IC and a LIN interface circuit, that exhibit long delay times between changes in the input and output signals due to the memory effects of the modelled ICs. The RF mixer modelling test case in [34] exhibits widely separated time-constants that are captured by the ESN model. In [35], the influence of the phase relationship between the RF interference signal and a low frequency functional signal on the conducted immunity of a non-inverting amplifier is analysed. In [36], a bandgap reference circuit is modelled, that exhibits RF-induced DC-shift of the bandgap voltage with increasing RF forward power in the DPI test bench due to nonlinear rectification.

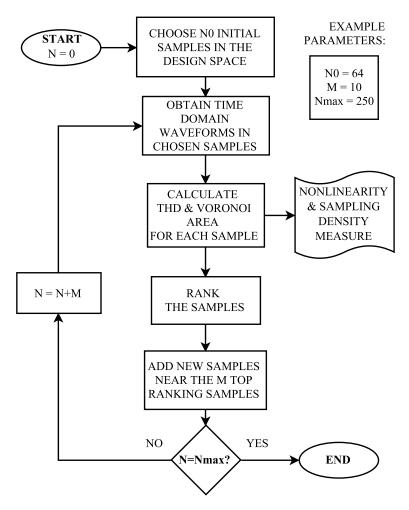

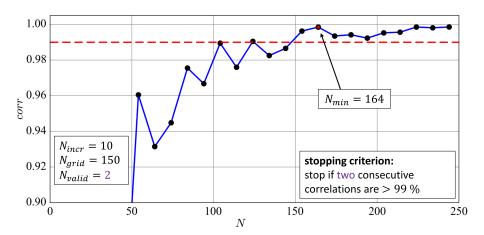

The time-domain waveforms used for building the ESN model in [36] are collected by uniform sampling of the RF design space defined by the frequency and forward power of the RF interference signal. The drawback of this exploration sampling strategy is that the number of samples required to properly sample the nonlinear regions of the circuit may increase significantly. In [37], an adaptive sampling algorithm is proposed for sampling the nonlinear circuit behaviour in the time-domain. The presented algorithm is based on the LOLA-Voronoi algorithm [11], [31], taking into account the nonlinearity of the observed time-domain waveforms, and it enables accurate modelling of nonlinear circuits at high forward power levels of the RF disturbance using a lower number of samples.

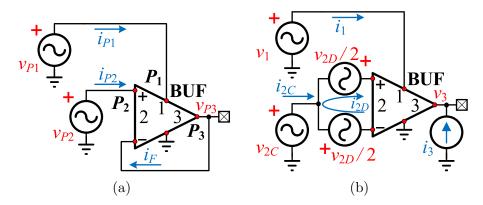

In [38], the ESN modelling methodology proposed in [34] and [36] is extended to enable building interchangeable behavioural models of an industrial buffered voltage reference circuit consisting of three subcircuits. The models preserve the RF voltages and RF currents observed in the time-domain simulation of the top-level test bench where each modelled transistor-level subcircuit is replaced by its behavioural model. The ESN model reproduces not only the DC value of the output voltage as in [11], but also the time-domain voltages and currents observed at the pins of the modelled circuit, including the RF-induced DC-shift. The nonlinear input and output impedances are modelled in the RF conditions using the ESN with controlled sources in a feedback loop [38].

The stability of behavioural models in circuit simulators is defined by: (i) the stability of the ESN model, and (ii) the stability of the feedback loop defined by the ESN model and the controlled sources in the nonlinear impedance model. The bounded-input bounded-output (BIBO) stability of the recurrent connections in the hidden layer of the ESN models is based on the existence of the echo state property [13]. The methods for generating linearized ESN models with guaranteed BIBO stability are presented in [34], [38], [39], and the model stability is verified in [9], [40] by analysing the eigenvalues of the ESN model in the complex z-domain.

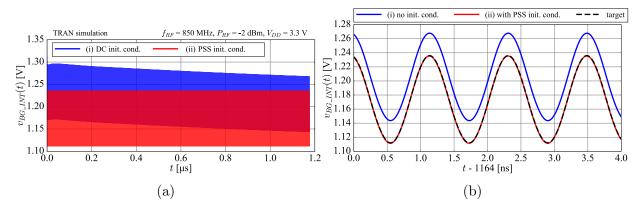

In [38], [41] the stability of the DC operating point stability of the ESN model in the DC simulations is analysed. The root causes for DC operating point instability are linked to the DC behaviour of the ESN model outside of the trained DC range. In order to simplify the model building procedure, the nonlinear impedance model architecture is extended to enable modelling the DC and RF behaviour independently.

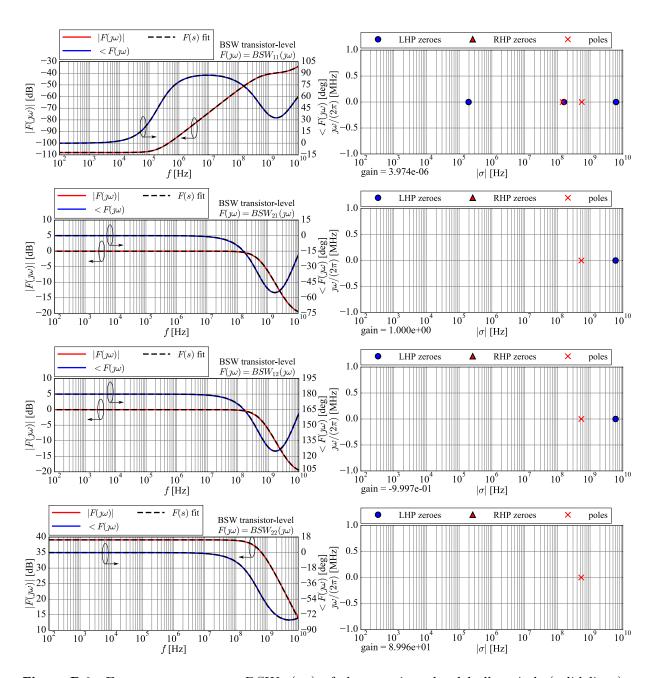

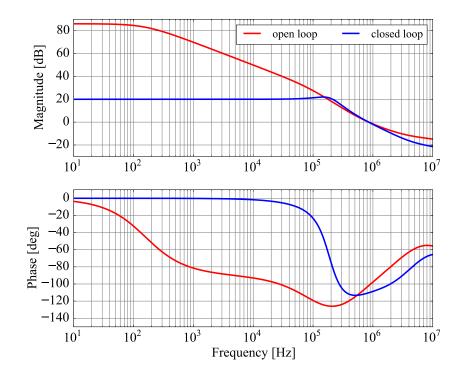

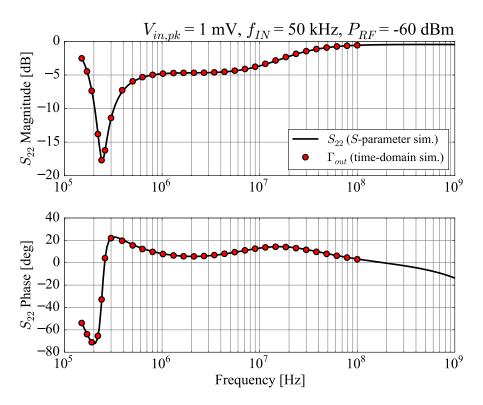

In [42], the stability of the feedback loop in the nonlinear impedance model is analysed in the discrete time-domain, and a method for obtaining the poles of the resulting discrete-time system using the frequency response using optimization based on the Cauchy integral is proposed, based on [43]. In [38], the small-signal stability is analysed in the continuous time-domain, and the stability discussion is generalized to include the influence of the ESN model outside of the trained RF frequency range on the stability of the initial transients in the time-domain simulations.

The principles derived in this research have been applied to the building of behavioural models in ESD and EMC area. In [44], a behavioural model of an ESD protection device that exhibits snapback is built for simulations of the transmission line pulsing (TLP) test. In [45], the RF harmonic distortion of an I2C pin of an integrated circuit is modelled for the analysis of the re-radiated RF disturbance in a magnetically coupled wireless system. Both test cases demonstrate the ability of behavioural models to reproduce highly nonlinear behaviour of integrated circuits.

# 1.3 Original scientific contribution

The original scientific contribution presented in the thesis consists of three components:

- 1. Modelling method for nonlinear circuits in large signal operating conditions using the echo state networks.

- 2. Adaptive algorithm for sampling nonlinear circuit behaviour in the time-domain.

- 3. Nonlinear impedance modelling method based on controlled sources for behavioural model interconnectivity.

#### 1.4 Thesis outline

The thesis is organized into five chapters and four appendices as follows.

Chapter2presents the echo state network as a nonlinear discrete-time element for modelling the relationships between the time-domain signals observed in integrated circuit simulations, including the mathematical definition, the training and verification procedures, the stability analysis, and the hyper-parameter selection guidelines. An adaptive algorithm is proposed for sampling the large-signal nonlinear behaviour of integrated circuits over the design space defined by the RF frequency and RF forward power in the conducted immunity simulation environment. The proposed methodology is applied to five modelling test cases of integrated circuits.

Chapter3presents the nonlinear impedance model architecture based on the echo state network with controlled voltage and current sources in a feedback loop. An overview of nonlinear effects in the conducted immunity simulation environment is given, a method for evaluating the model accuracy over the RF design space is proposed, and an algorithm for DPI simulations using binary search is presented. The stability of the behavioural models is analysed and sufficient conditions for model stability in the top-level test bench are derived. The proposed methodology is applied to an industrial buffered voltage reference integrated circuit by simulating various combinations of transistor-level and ESN model representations of the subcircuits.

Chapter4presents behavioural modelling applications in ESD and EMC area. A lumped-distributed model of a transmission line pulsing setup is presented, including a behavioural model of an ESD protection device that exhibits snapback. The behavioural model of the I2C pad of an industrial integrated circuit is presented that enables simulating the RF re-radiation due to RF harmonic distortion in a magnetically coupled system.

Chapter5concludes the thesis.

AppendixApresents the implementation of the behavioural model of a generic 2-port circuit in the hardware description language Verilog A, including the DC look-up table, the ESN model, and the ESN rescaling block.

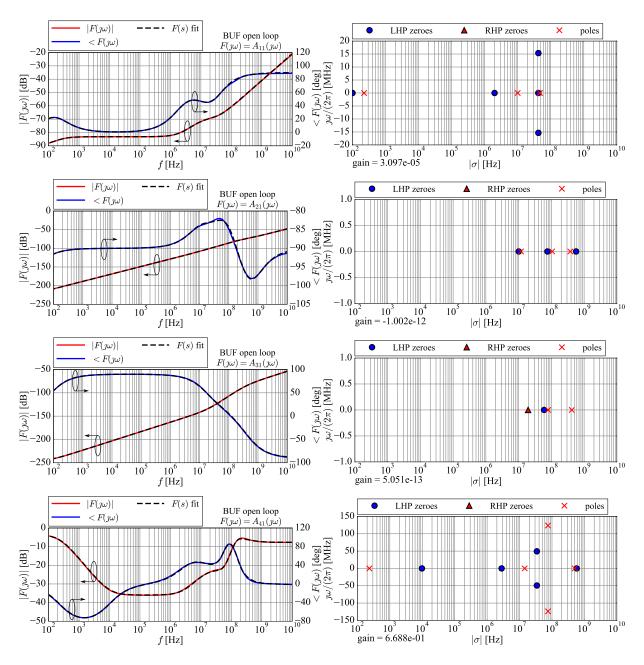

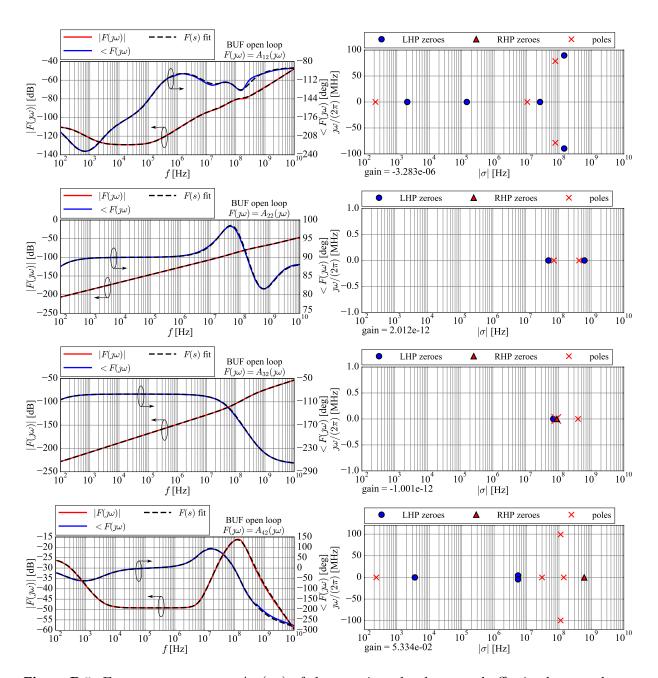

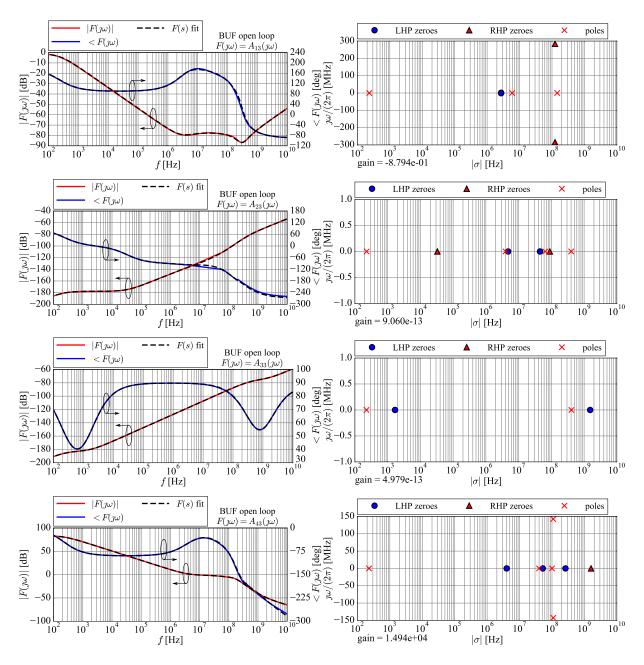

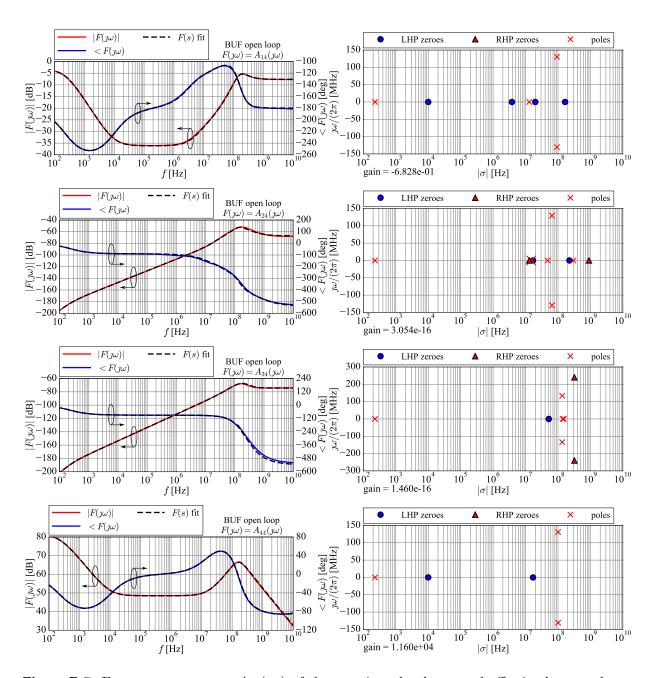

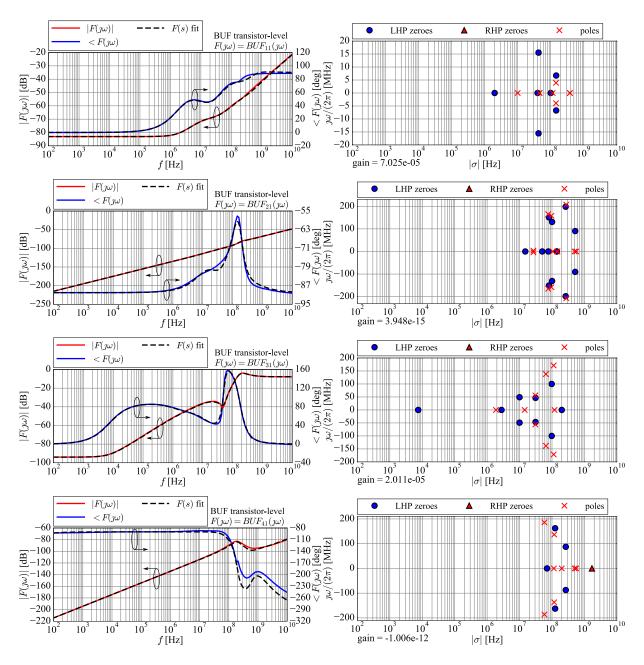

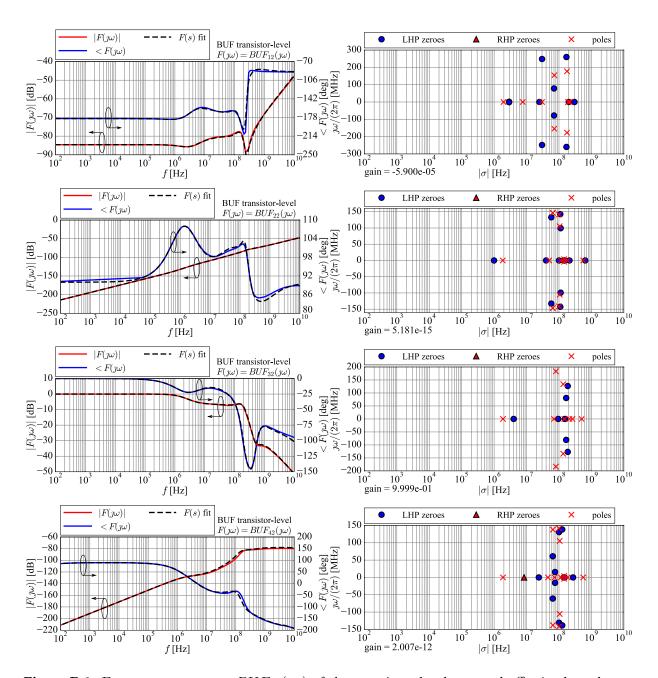

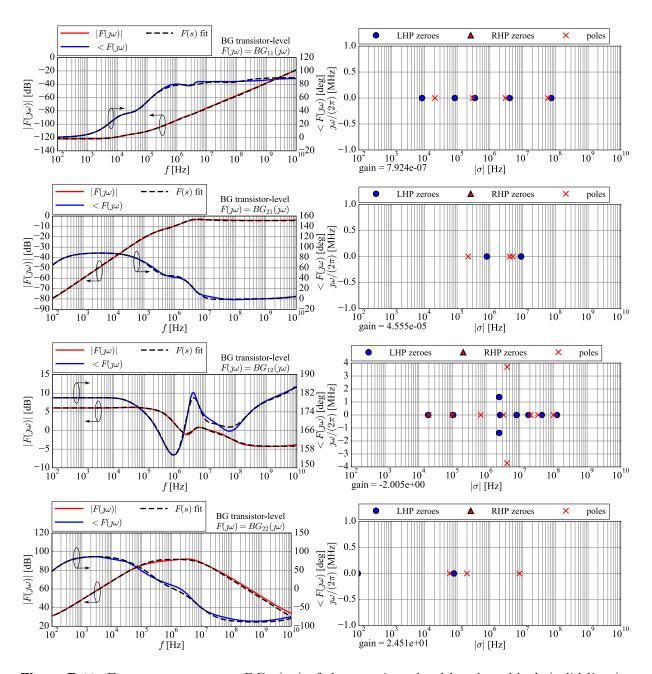

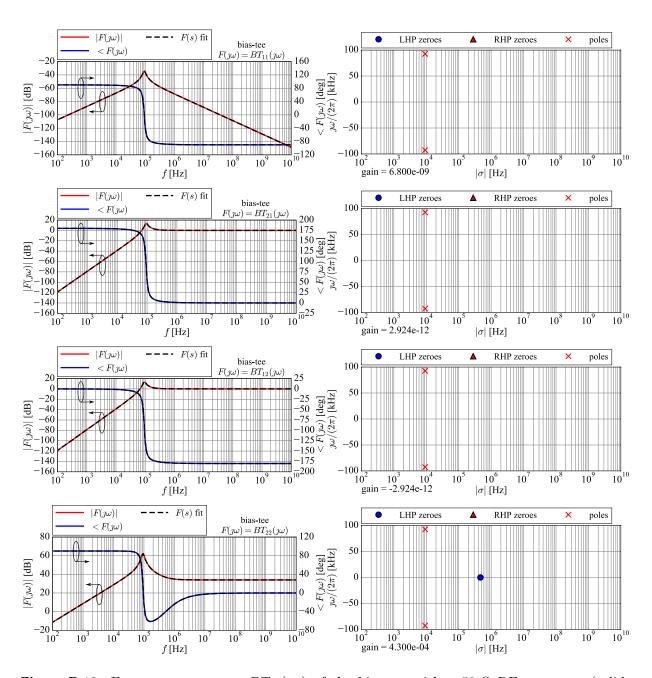

AppendixBpresents the analysis of the small-signal behaviour of the transistor-level buffered voltage reference circuit, including the frequency responses of each subcircuit and the associated transfer functions. The closed-form solutions for each perturbation voltage and current in the conducted immunity simulation test bench are derived.

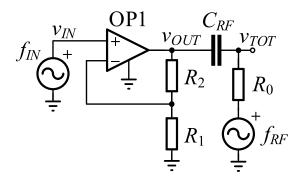

AppendixCpresents the analysis of the influence of the phase relationship between the RF interference and the functional signal on the DPI characteristics of an operational amplifier in the non-inverting configuration through the output reflection coefficient.

AppendixDpresents the methodology for determining the poles of a discrete-time system based on its frequency response using global optimization of the Cauchy integral.

# Chapter 2

# Modelling large-signal nonlinear circuit behaviour using echo state networks

#### 2.1 Motivation

The echo state network (ESN) is presented as the building block for the behavioural modelling of nonlinear integrated circuits. The properties of the ESN models are investigated with focus on modelling the relationships of time-domain signals observed in integrated circuit simulations, which are characterized by memory effects and by widely separated time-constants. An adaptive algorithm for sampling the nonlinear behaviour of integrated circuits in the time-domain is presented, that enables building ESN models that cover a range of operation of the modelled circuit. The presented modelling methodology is applied to five modelling test cases.

The chapter is organized as follows. Section 2.2 presents the definition of the echo state network with the conditions for the bounded-input bounded-output (BIBO) stability, and the generic ESN training and verification procedures for time-series modelling. Section 2.3 presents the methodology for modelling nonlinear circuit behaviour consisting of multiple time-domain waveforms obtained by circuit simulations using the ESN, and the adaptive algorithm for sampling the nonlinear circuit time-domain behaviour that enables automating the construction of the training dataset. Section 2.4 presents five modelling test cases that demonstrate the ability of the ESN to capture the nonlinear relationships between time-domain signals observed in simulations of various integrated circuit blocks. The presented results are discussed in Section 2.5, and Section 2.6 summarizes the chapter. The research from this chapter is presented in [34], [37].

### 2.2 Echo state networks

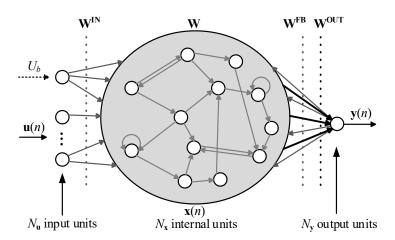

Figure 2.1: Generic diagram of the echo state network [34].

The echo state network (ESN) is a type of recurrent neural network (RNN) first proposed in [13]. Referring to Fig.2.1, the ESN consists of  $N_u$  input units in the input layer,  $N_x$  internal units in the hidden layer, and  $N_y$  output units in the output layer. Each unit, or neuron, is associated with an activation signal in the discrete time-domain that is defined by the recurrent connections between the units in the input, output, and hidden layers of the network. The connections from the input units to the internal units are defined by the input weight matrix  $\mathbf{W^{IN}}$ , the recurrent connections between the internal units are defined by the internal weight matrix  $\mathbf{W}$ , and the feedback connections from the output units to the internal units are defined by the output feedback weight matrix  $\mathbf{W^{FB}}$ . The output unit activations are constructed from the activation signals available in the input and hidden layers using the connections defined by the output weight matrix  $\mathbf{W^{OUT}}$ .

Unlike the training procedures of general recurrent neural networks, where all connections in the RNN are trained using slow training algorithms based on gradient descent, the idea behind the ESN is to train only the connections from the input and internal units to the output units of an ESN instance with randomly generated recurrent connections in the hidden layer, significantly reducing the complexity of the training procedure. The validity and the bounded-input bounded-output (BIBO) stability of this modelling approach is based on the echo state property, which states that the influence of the input sequence on the internal unit activations fades away exponentially in time. In this way, the internal unit activations become nonlinear "echoes" of the input data sequence fed to the input units, and the ESN retains the memory of the previous input signal values in its hidden layer. A sufficient condition to guarantee the echo state property of a randomly generated ESN is derived and proven in [39]. The formal mathematical definition of the ESN as a discrete-time system and the BIBO stability analysis are presented next.

#### 2.2.1 ESN definition in the discrete time-domain

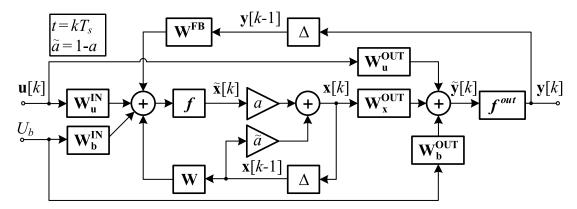

Figure 2.2: The signal flow-diagram of the echo state network as a discrete-time system with the constant sampling time  $T_s$  and the leaky integrator neuron model defined by the leaking rate a.

Fig.2.2presents the ESN as a discrete-time system with the constant sampling time  $T_s$ . The vector  $\mathbf{u}[k] \in \mathbb{R}^{N_{\mathbf{u}}}$  is the input unit activation vector that contains the instantaneous values of the  $N_{\mathbf{u}}$  input signals at the moment  $t = kT_s$ , and the signal  $U_b$  is a time-constant bias term. The bias term  $U_b$  and the input signal vector  $\mathbf{u}[k]$  define the extended input signal vector  $\tilde{\mathbf{u}}(n) = [U_b; \mathbf{u}[k]] \in \mathbb{R}^{N_b+N_{\mathbf{u}}}$  by concatenation, where  $N_b \in \{0,1\}$  indicates if the bias-term  $U_b$  is used or not. The vector  $\mathbf{x}[k] \in \mathbb{R}^{N_{\mathbf{x}}}$  is the internal unit activation vector that contains the instantaneous values of the  $N_{\mathbf{x}}$  activation signals within the hidden layer, and the vector  $\mathbf{y}(n) \in \mathbb{R}^{N_{\mathbf{y}}}$  is the output signal vector that contains the instantaneous values of the  $N_{\mathbf{y}}$  output signals. At each time-step k, the internal unit activation update vector  $\tilde{\mathbf{x}}[k] \in \mathbb{R}^{N_{\mathbf{x}}}$  is defined by the update equation given in Eq. (2.1):

$$\tilde{\mathbf{x}}[k] = f\left(\mathbf{W}^{\mathbf{IN}}\tilde{\mathbf{u}}[k] + \mathbf{W}\mathbf{x}[k-1] + \mathbf{W}^{\mathbf{FB}}\mathbf{y}[k-1] + \mathbf{v}_{\sigma}[k]\right)$$

(2.1)

where f is the nonlinear activation function of the internal units, typically the hyperbolic tangent tanh, as in [13]. The matrices  $\mathbf{W^{IN}} \in \mathbb{R}^{N_{\mathbf{x}} \times (N_{\mathbf{b}} + N_{\mathbf{u}})}$ ,  $\mathbf{W^{FB}} \in \mathbb{R}^{N_{\mathbf{x}} \times N_{\mathbf{y}}}$  are the input and output feedback weight matrices that define the connections from the input and output units to the internal units. The recurrent connections between the internal units in the hidden layer are defined by the internal weight matrix  $\mathbf{W} \in \mathbb{R}^{N_{\mathbf{x}} \times N_{\mathbf{x}}}$ . The vector  $\mathbf{v}_{\sigma}[k] \in \mathbb{R}^{N_{\mathbf{x}}}$  is a white noise term with the variance  $\sigma$  that is used as a regulariser for the internal unit activation update vector. The internal units use the "leaky integrator" neuron model defined in [13], where the internal state vector  $\mathbf{x}[k]$  is defined using the leaking rate  $a \in (0,1]$  as a linear combination of its value  $\mathbf{x}[k-1]$  in the previous time-step, and the update vector  $\tilde{\mathbf{x}}[k]$ , according to Eq. (2.2):

$$\mathbf{x}[k] = a\tilde{\mathbf{x}}[k] + (1-a)\mathbf{x}[k-1]$$

(2.2)

The extended input signal vector  $\tilde{\mathbf{u}}[k]$  and the internal unit activation vector  $\mathbf{x}[k]$  define the collected states vector  $\mathbf{z}[k] = [U_b; \mathbf{u}[k]; \mathbf{x}[k]] \in \mathbb{R}^{N_b + N_u + N_x}$  by concatenation. Optionally, the collected states vector can be augmented by concatenating additional input and internal unit activation vector transforms obtained using the augmented activation function  $f^{aug}$ , resulting in  $\mathbf{z}[k] = [U_b; \mathbf{u}[k]; \mathbf{x}[k]; f^{aug}(\mathbf{u}[k]); f^{aug}(\mathbf{x}[k])] \in \mathbb{R}^{N_b + 2N_u + 2N_x}$ . The typical augmented activation function  $f^{aug}$  is the square function, as in [13]. The output unit activation vector  $\mathbf{y}[k]$  is defined by the output equation given in Eq. (2.3):

$$\mathbf{y}\left[k\right] = f^{out}\left(\mathbf{W}^{\mathbf{OUT}}\mathbf{z}\left[k\right]\right) \tag{2.3}$$

where  $f^{out}$  is the output unit activation function, typically the identity function, as in [13], and the matrix  $\mathbf{W}^{\mathbf{OUT}} \in \mathbb{R}^{N_{\mathbf{y}} \times (N_{\mathbf{b}} + N_{\mathbf{u}} + N_{\mathbf{x}})}$  is the output weight matrix.

For a given ESN instance, the input weight matrix  $\mathbf{W^{IN}}$  and the output feedback weight matrix  $\mathbf{W^{FB}}$  are generated randomly using the values from user-selected distributions, typically the uniform distribution in [-1,1], as in [13]. The BIBO stability of the recurrent connections in the hidden layer is based on the existence of the echo state property of a given ESN model instance. According to the sufficient condition derived and proven in [39], the echo state property is guaranteed if the internal weight matrix  $\mathbf{W}$  is diagonally Schur stable. This is achieved by randomly generating an initial matrix  $\tilde{\mathbf{W}} \in \mathbb{R}^{N_{\mathbf{x}} \times N_{\mathbf{x}}}$  with all positive entries, determining its spectral radius  $\tilde{r}$ , and globally rescaling it to any spectral radius r < 1 using Eq. (2.4):

$$\mathbf{W} = \tilde{\mathbf{W}} \frac{r}{\tilde{r}} \tag{2.4}$$

Finally, the signs of randomly selected entries in **W** are changed in order to obtain negative entries. During the training and the execution of a given ESN instance, the weight matrices **W**<sup>IN</sup>, **W**, **W**<sup>FB</sup> remain unchanged, while the output weight matrix **W**<sup>OUT</sup> is trained to generate the correct output signals from the activation signals available in the hidden layer using training algorithms based on linear regression. The ESN training and verification procedures are presented next.

#### 2.2.2 ESN training and verification procedures

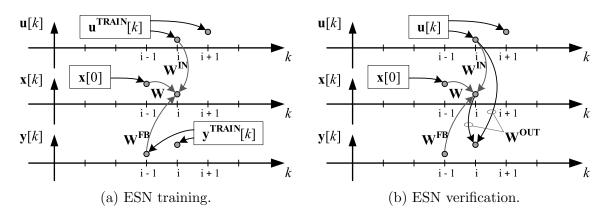

Figure 2.3: Graphical representation of the ESN training and verification procedures [34].

The ESN training procedure is presented in Fig.2.3a. The training dataset consists of the sequence of the desired instantaneous output training values  $\mathbf{y^{TRAIN}}[k] \in \mathbb{R}^{N_y}$ that is associated with the sequence of the input training values  $\mathbf{u}^{\mathbf{TRAIN}}[k] \in \mathbb{R}^{N_{\mathbf{u}}}$  for the discrete-time steps k = 1, ..., T, where T is the training period in the discrete time-domain. The values of the input and output training sequences over the training period Tare collected in the training matrices  $\mathbf{U^{TRAIN}} \in \mathbb{R}^{N_{\mathbf{u}} \times T}$  and  $\mathbf{Y^{TRAIN}} \in \mathbb{R}^{N_{\mathbf{y}} \times T}$ . During the ESN training procedure, the input units are driven by the input training sequence  $\mathbf{u}^{\mathbf{TRAIN}}[k]$ , and the internal unit activations  $\mathbf{x}$  are updated starting from a random initial value  $\mathbf{x}[0]$ . If the feedback connections from the output units to the internal units are used, the output units are driven by the desired output sequence  $\mathbf{y}^{\mathbf{TRAIN}}[k]$ . In order to allow the influence of the random initial condition on the internal unit activations to fade away according to the echo state property, a number of initial time-steps is discarded. The values of the resulting collected state vector sequence  $\mathbf{z}[k]$  over the discrete-time steps n = 1, ..., T' are collected in the design matrix  $\mathbf{Z} \in \mathbb{R}^{(N_{\mathbf{b}} + N_{\mathbf{u}} + N_{\mathbf{x}}) \times T'}$ , where T' is the training period after the initial discard period. The output weight matrix  $\mathbf{W}^{\mathbf{OUT}}$  is calculated by solving the linear regression problem given in Eq. (2.5):

$$\mathbf{Y}^{\mathbf{TRAIN}} = \mathbf{W}^{\mathbf{OUT}}\mathbf{Z},\tag{2.5}$$

where the output weight matrix  $\mathbf{W}^{\mathbf{OUT}}$  is the unknown that determines the model output signal vector sequence  $\mathbf{y}[k] \in \mathbb{R}^{N_{\mathbf{y}}}$  from the collected state vector sequence  $\mathbf{z}[k]$  according to the output equation Eq. (2.3). The optimal solution for  $\mathbf{W}^{\mathbf{OUT}}$  minimises an error measure  $E\left(\mathbf{y}[k], \mathbf{y}^{\mathbf{TRAIN}}[k]\right)$  over the training period, where the error measure E is determined by the selected regression method used for solving Eq. (2.5), and it largely determines the properties of the resulting echo state network. Most researchers use ridge regression [13], also known as regression with Tikhonov regularization, to find the opti-

mal  $W^{OUT}$ , as given in Eq. (2.6):

$$\mathbf{W}^{\mathbf{OUT}} = \mathbf{Y}^{\mathbf{TRAIN}} \mathbf{Z}^{\top} \left( \mathbf{Z} \mathbf{Z}^{\top} + \beta \mathbf{I} \right)^{-1}, \tag{2.6}$$

where  $\beta$  is the regularization coefficient, **I** is the identity matrix, and  $\Box^{-1}$  is the matrix inversion operator. In the special case with  $\beta=0$ , Eq. (2.6) becomes the solution of a linear regression problem that minimises the L2-norm of the model error. Adding the white noise term  $\mathbf{v}_{\sigma}[k]$  as an additional regulariser in Eq. (2.1) during the ESN training procedure, as suggested in [13], is shown to improve the stability and the generalisation properties of the trained ESN and results in the output coefficients with lower values that reduce the over-fitting of the model to the training dataset. The linear regression methods based on minimising the L1-norm are shown to drive most output weights to zero [46]. This is a desirable mathematical property, as it enables reducing an initially large network to a more compact size. The presented training algorithm is an offline method, because the output weights are calculated after driving the ESN with the full training dataset. Online training methods that dynamically update the output weights while the network is being driven by the training dataset are not considered in this work.

The verification process of a trained ESN is shown in Fig.2.3b. The input units of the trained ESN are driven by the input sequence  $\mathbf{u}[k]$  from the verification dataset. The ESN produces the output sequence  $\mathbf{y}[k]$  based on the output equation Eq. (2.3), and it is compared to the desired output sequence  $\mathbf{y}^{\text{TRAIN}}[k]$  using any error measure E, typically the mean-square error (MSE), as defined in Eq. (2.7):

$$\mathbf{MSE}\left(\mathbf{y}\left[k\right], \mathbf{y^{TRAIN}}\left[k\right]\right) = \sum_{k=1}^{N_{test}} \left(\mathbf{y}\left[k\right] - \mathbf{y^{TRAIN}}\left[k\right]\right)^{2}$$

(2.7)

where  $N_{test}$  is the number of discrete-time samples in the verification dataset, the vector  $\mathbf{MSE} \in \mathbb{R}^{N_y}$  contains the mean square error for each output signal, and the squaring operation is performed element-wise on the difference vector.

The presented ESN training procedure for reproducing the output discrete-time series  $\mathbf{y}[k]$  as a function of the given input discrete-time series  $\mathbf{u}[k]$  is the basis for defining the methodology for modelling integrated circuit behaviour observed in time-domain simulations that is presented next.

# 2.3 Method for modelling circuit time-domain behaviour

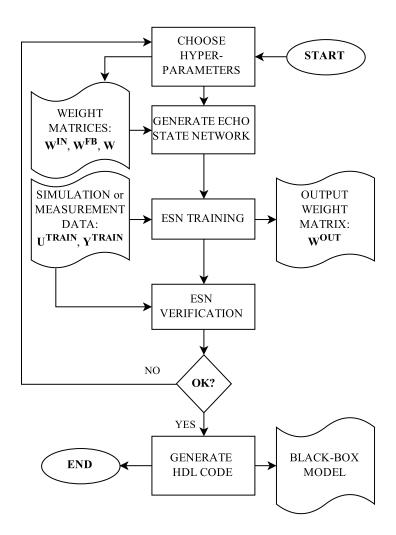

The proposed method for modelling the time-domain behaviour of integrated circuits using echo state networks is presented in Fig.2.4.

Figure 2.4: The proposed method for modelling simulated or measured behaviour of integrated circuits in the time-domain using echo state networks [34].

The ESN hyper-parameters are selected using the guidelines given in Section 2.3.1, and a BIBO stable ESN model is generated using the procedure presented in Section 2.2.1. The ESN model is trained according to the ESN training procedure given in Section 2.2.2 using the simulated or measured data covering the desired operating range of the model, obtained either by uniform sampling, or using the adaptive sampling algorithm presented in Section 2.3.2. In order to test its interpolation properties, the trained ESN model is tested using the verification dataset containing time-domain signals not included in the training dataset. The procedure is repeated with modified hyper-parameters until acceptable ESN model accuracy is achieved, and the final ESN model is implemented in any hardware description language using the procedure in Section 2.3.3.

#### 2.3.1 ESN hyper-parameter selection

ESN hyper-parameters are the network parameters that define the common properties of ESN instances that are built by iteratively generating the random recurrent connections in the ESN hidden layer. The guidelines for the selection of each hyper-parameter presented below are based on the research published in [9], [13], [21], [34], [36], [37]. Within the scope of this work, all hyper-parameters are set manually, and optimized by iterative trials that are enabled by the fast training procedure of the ESN.

The hyper-parameters related to the echo state network topology are: the number of internal units  $N_x$  in the hidden layer, the spectral radius r, the leaking rate a, the internal unit activation function f, the output unit activation function  $f^{out}$ , and the augmented activation function  $f^{aug}$ .

The number of internal units  $N_x$  should be small enough to prevent the ESN over-fitting the training dataset. An over-fitted ESN is characterized by very large coefficients in the output weight matrix  $\mathbf{W}^{\mathbf{OUT}}$ , that enable modelling the training dataset with high accuracy, but with poor interpolation between the trained data points [39]. Within this work, most ESN models use up to 15 internal units, and the largest ESN uses 60 internal units. The spectral radius r determines the properties of the input signal "echoing" in the hidden layer, and it is set to values between 0.8 and 0.99 for the circuit applications presented in this work. The leaking rate a is used to "smooth-out" the ESN response, by reusing the internal unit activations from the previous time-step in the update equation of the neurons in the hidden layer. The modelling results presented in this work demonstrate that the leaking rate a is a useful knob in building the ESN models that capture sinewave-shaped waveforms observed in conducted immunity simulations, with values between 0.07 and 1. The typical internal unit activation function f used in this work and in literature is the hyperbolic tangent tanh, that has a linear characteristic around zero appropriate for modelling the RF voltage and RF current waveforms with low amplitude, while the modelled signals with higher amplitude use the more nonlinear regions of the tanh function. The output unit activation function  $f^{out}$  and the augmented activation function  $f^{aug}$  are typically not used in the modelling of integrated circuit behaviour.

The hyper-parameters related to the weight matrices of the echo state network are the distribution limits of the coefficients in the weight matrices and the bias-term  $U_b$ . The randomly generated weight matrix coefficients are typically selected from the uniform distribution between -1 and 1. The bias-term  $U_b$  enables adding a random bias level to each internal unit activation through the input weight matrix coefficients related to the bias-term, allowing different neurons to model different regions of nonlinearity. Typical values of the bias-term  $U_b$  are between 0 and 1, depending on the nonlinearity of the modelled time-domain signals.

The hyper-parameters related to the training procedure are the uniform sampling time  $T_s$ , the variance  $\sigma$  of the additive white noise term  $\mathbf{v}_{\sigma}[k]$  in Eq. (2.1), the length T of the training dataset, the linear regression method used to solve the optimization problem in Eq. (2.5), the ridge regression coefficient  $\beta$  in case linear regression is run using the ridge regression method based on Eq. (2.6).

The signals obtained by circuit simulations are non-uniformly sampled time-domain waveforms. Since the ESN is a discrete-time system, the modelled waveforms are interpolated to a uniform sampling time  $T_s$ , that is for the Nyquist frequency required by the bandwidth of the modelled signals. The sampling times used in the presented work depend on the application, and vary from 0.5 ps for very fast signals up to 100 ps for slower signals. The values of the variance  $\sigma$  of the additive white noise regulariser term are chosen to be several orders of magnitude lower than the amplitude of the modelled signals, typically below  $5\cdot10^{-4}$ .

The training period T is used to set weighting factors on the time-domain waveforms in the training dataset that have a wide range of amplitudes, in order to avoid the waveforms with larger amplitudes dominating over the waveforms that have lower amplitudes in the overall model error measure E used to train the ESN. By increasing the training period of the waveforms with lower amplitudes, approximately equal weighting between all RF waveforms can be achieved in the training dataset.

The methods used for linear regression include different implementations of the L2 or L1 norm minimisation of the model error available in the scientific packages in Python. Additional hyper-parameters related to the special properties of the hidden layer are the connectivity factor that determines the sparsity of the connections in the hidden layer, the limitation of the input weight matrix coefficients to the two extreme values defined by the coefficient distribution limits, and setting the selected connections from the input units directly to the output units to zero [13]. These hyper-parameters have more application in the computer science applications of the ESN, rather than the circuit modelling applications.

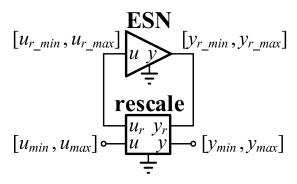

The final group of hyper-parameters is related to the rescaling of the time-domain signals observed in integrated circuit simulations that are fed to the ESN model. The voltages and currents observed in circuit simulations often have DC values and amplitudes of widely different orders of magnitude. The modelled signals are therefore rescaled to a normalized range defined for each ESN input and output signal as follows. Referring to Fig.2.5, the input signal u is rescaled from the range  $[u_{min}, u_{max}]$  defined by the input signals in the training dataset to the rescaled value  $u_r$  in the range  $[u_{r\_min}, u_{r\_max}]$ , and it is fed to the ESN as an input signal. The ESN output signal  $y_r$  is rescaled from the normalized range  $[y_{r\_min}, y_{r\_max}]$  to the restored value y in the range  $[y_{min}, y_{max}]$  defined

by the output signals in the training dataset. The input and output signals are rescaled using the expressions in Eq. (2.8):

$$u_{r} = (u - u_{min}) \cdot \frac{u_{r\_max} - u_{r\_min}}{u_{max} - u_{min}} + u_{r\_min}$$

$$y = (y_{r} - y_{r\_min}) \cdot \frac{y_{max} - y_{min}}{y_{r\_max} - y_{r\_min}} + y_{min}$$

(2.8)

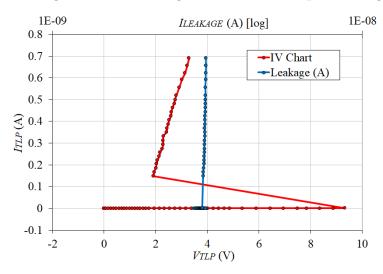

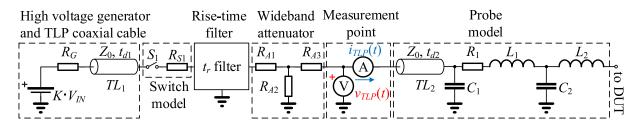

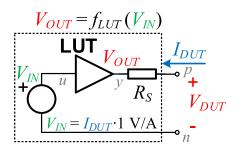

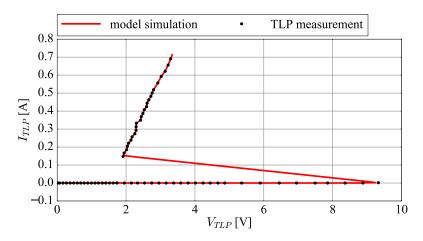

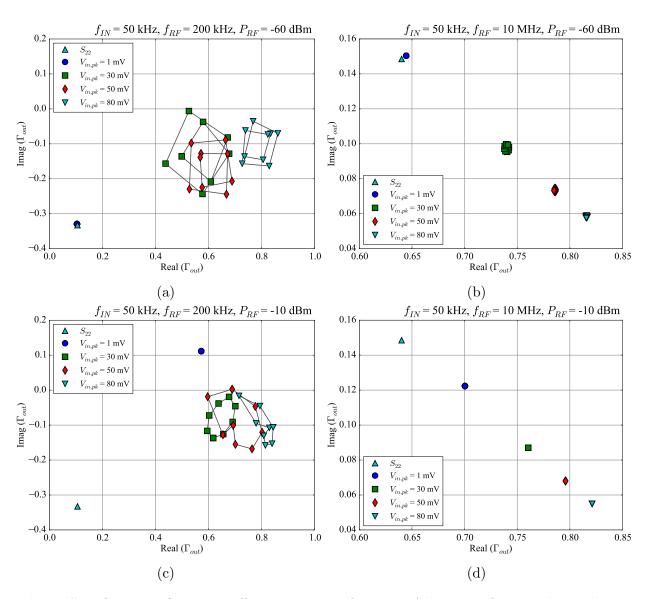

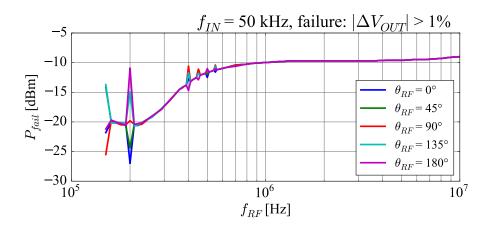

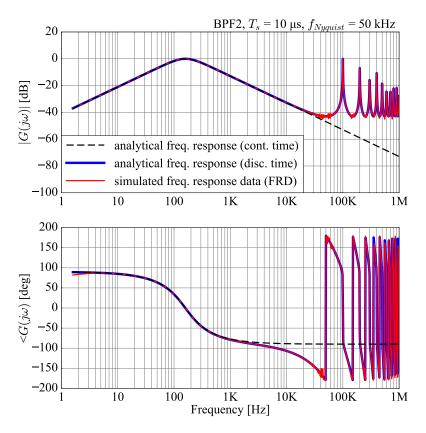

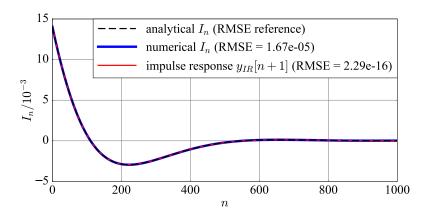

Figure 2.5: Echo state network with the rescaling block.