# Design characterization of multiport electro-optical circuits for broadband voltage measurements in an electromagnetically polluted environment

Štimac, Hrvoje

Doctoral thesis / Disertacija

2020

Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Zagreb, Faculty of Electrical Engineering and Computing / Sveučilište u Zagrebu, Fakultet elektrotehnike i računarstva

Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:168:587135

Rights / Prava: In copyright/Zaštićeno autorskim pravom.

Download date / Datum preuzimanja: 2025-03-14

Repository / Repozitorij:

FER Repository - University of Zagreb Faculty of Electrical Engineering and Computing repozitory

# University of Zagreb

FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Hrvoje Štimac

## DESIGN AND CHARACTERIZATION OF MULTIPORT ELECTRO-OPTICAL CIRCUITS FOR BROADBAND VOLTAGE MEASUREMENTS IN AN ELECTROMAGNETICALLY POLLUTED ENIVRONMENT

DOCTORAL THESIS

Zagreb, 2020

# University of Zagreb

FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Hrvoje Štimac

## DESIGN AND CHARACTERIZATION OF MULTIPORT ELECTRO-OPTICAL CIRCUITS FOR BROADBAND VOLTAGE MEASUREMENTS IN AN ELECTROMAGNETICALLY POLLUTED ENIVRONMENT

DOCTORAL THESIS

Supervisor: Professor Adrijan Barić, PhD

Zagreb, 2020

# Sveučilište u Zagrebu FAKULTET ELEKTROTEHNIKE I RAČUNARSTVA

Hrvoje Štimac

# PROJEKTIRANJE I KARAKTERIZACIJA VIŠEPROLAZNIH ELEKTROOPTIČKIH SKLOPOVA ZA ŠIROKOPOJASNO MJERENJE NAPONA U ELEKTROMAGNETSKI ZAGAĐENOJ OKOLINI

DOKTORSKI RAD

Mentor: prof. dr. sc. Adrijan Barić

Zagreb, 2020.

This doctoral thesis was done at the University of Zagreb Faculty of Electrical Engineering and Computing, Department of Electronics, Microelectronics, Computer and Intelligent Systems.

Supervisor: Professor Adrijan Barić, PhD

This doctoral thesis contains 192 pages.

Doctoral thesis No.: \_\_\_\_\_

## About the Supervisor

Adrijan Barić was born in Zagreb in 1958. He received Dipl. Ing. and M.Sc. degrees in electrical engineering from the University of Zagreb (UniZag), Faculty of Electrical Engineering and Computing (FER), Zagreb, Croatia, in 1982 and 1985. He received the PhD degree from the Dublin City University, Ireland, in 1995. Since 1984 he is employed by FER. He was on a two-month research visit at the Rutherford Appleton Laboratory, England, and on a six-month postdoc research visit at the Ghent University, Belgium. He was promoted to Full professor in 2013. He was a principal investigator of two projects funded by the Ministry of Science, Education and Sports of Croatia, one BICRO project, he coordinated the FER research team in one EU FP6 and one FP7 project, as well as several bilateral and multilateral projects with EU companies and universities. He presently coordinates the project "MUNJA" funded by the company ON Semiconductor (Belgium), the project "Sensor Fusion" funded by ams AG (Austria), and the project "Fast switching converters based on GaN devices and resonant architectures" funded by the Croatian Science Foundation HRZZ. He was the President of the Committee for Research, Development and Technology of the UniZag from 2008 to 2011. From 2013 to 2017 he was the President of the Council of Technical Faculties of the UniZag. He was a General Chair or Co-Chair of two IEEE conferences, Finance Chair of one IEEE conference, and Technical Programme Chair of EMC Compo 2011. He is a member of the societies IEEE, HD MIPRO, KoREMA and AMAC-FER. He received Gold Medal "Josip Lončar" for outstanding performance from FER in 2015.

## **O** mentoru

Adrijan Barić rođen je u Zagrebu 1958. Diplomirao je 1982. i magistrirao 1985. na Fakultetu elektrotehnike i računarstva (FER) Sveučilišta u Zagrebu (SuZ). Doktorirao je na Dublin City University, Irska, 1995. Na FER-u radi od 1984. Bio je gostujući istraživač 2 mjeseca na Rutherford Appleton Laboratory, Engleska, te 6 mjeseci na Ghent University, Belgija, 2000. U redovitog profesora u trajnom zvanju izabran je 2013. Bio je glavni istraživač na dva projekta MZOS-a, jednom BICRO projektu, te je vodio je FER-ov tim u jednom EU FP6 i jednom EU FP7 projektu, te više bilateralnih i multilateralnih projekata s EU tvrtkama i sveučilištima. Trenutno vodi projekt "Sensor Fusion" s ams AG, Austrija, HRZZ projekt "Brzi prekidački pretvornici zasnovani na GaN elementima i rezonantnim arhitekturama", te projekt "MUNJA" s tvrtkom ON Semi, Belgija. Objavio je više od 80 radova u časopisima i zbornicima konferencija iz područja elektroničkih sklopova i elektromagnetske kompatibilnosti. Bio je predsjednik Odbora za istraživanje, razvoj i tehnologiju SuZ-a od 2008. do 2011. Od 2013. do 2017. bio je predsjednik Vijeća tehničkog područja SuZ-a. Bio je predsjedatelj ili supredsjedatelj dvije IEEE konferencije, financijski voditelj jedne IEEE konferencije, te Technical Programe Chair konferencije EMC Compo 2011. Član je udruga IEEE, HD MIPRO, KoREMA i AMAC-FER. Godine 2015. primio je FER-ovu Zlatnu plaketu "Josip Lončar" za svoj rad.

This research was supported in part by the Croatian Science Foundation (HRZZ) within the project Advanced design methodology for switching DC-DC converters, and in part by ON Semiconductor Belgium.

#### Abstract

Broadband electro-optical differential probes for voltage measurements in an electromagnetically polluted environment are designed and characterized. The differential circuit topology is used because of its good immunity to noise. By separating the signal acquisition and signal processing part of the system, a fully isolated measurement system is implemented, where both the measured RF signal and the bias signal are transmitted using an optical connection. Methods for characterization and modelling of multiport circuits at high frequencies are compared. The differential circuits are evaluated by measuring the mixed-mode S-parameters. The differential-mode signal transmission, the common-mode signal transmission, and the common-mode rejection ratio are evaluated.

The probe circuit consists of three main parts: the attenuator, the laser and the bias circuit. Each part of the probe circuit is characterized by performing measurements, electromagnetic and circuit simulations, and circuit modelling. The design of each part of the probe circuit is optimized in order to improve the common-mode rejection ratio of the system. The optimized attenuator circuit, laser and bias circuit layout are implemented in the probe circuit design. Probe circuit characterization structures with different attenuation ratios are characterized. The repeatability of the characteristics between probes with the same probe circuit design is evaluated. The probe circuit layout is optimized and implemented on a connectorized probe with a well-defined ground connection and a fully floating wafer probe. The probes are characterized in the frequency range from 1 MHz to 8 GHz. The impact of ground connection and power supply isolation on the performance of the probes is evaluated. The input impedance of the two probes is characterized and modelled. The simple and low cost measurement system can be implemented as a standalone probe or as a part of an integrated circuit characterization and test environment. The system is designed for characterization of electrostatic discharge waveforms, and can also be used for electromagnetic compatibility measurements.

**Keywords**: attenuator, circuit modelling, common-mode rejection ratio (CMRR), common-mode signal, differential voltage measurement, differential-mode signal, electro-optical system, electromagnetic compatibility (EMC), electrostatic discharge (ESD), noise immunity, power-over-fiber (PoF), vertical-cavity surface-emitting laser (VCSEL)

## Prošireni sažetak

Elektrostatski izboji (engl. *electrostatic discharge* – ESD) su brzi pulsevi s tipično visokom razinom napona. Ovi brzi pulsevi imaju širok frekvencijski opseg koji je tipično u gigahercnom području te mogu stvoriti elektromagnetske smetnje u mjernom sustavu. S kontinuiranim razvojem elektroničkih uređaja postoji stalna potreba za unaprjeđenjem tehnika zaštite od elektrostatskih izboja. Mogućnost jednostavnog i praktičnog mjerenja naponskih valnih oblika elektrostatskih izboja pruža korisne informacije dizajnerima integriranih sklopova. Unapređuje se razumijevanje mehanizama propagacije elektrostatskih izboja te se omogućava poboljšanje tehnika potiskivanja i zaštite od elektrostatskih izboja u elektroničkim sklopovima.

Projektiraju se i karakteriziraju širokopojasne elektrooptičke sonde za diferencijsko mjerenje napona u elektromagnetski zagađenoj okolini. Koristi se sklop s diferencijskom topologijom zbog dobre otpornosti na smetnje. Odvajanjem dijela sustava za mjerenje i obradu signala ostvaruje se potpuno izolirani mjerni sustav, gdje se i mjereni radiofrekvencijski signal i signal napajanja prenose optičkom vezom. Svaki dio elektrooptičkog sustava karakterizira se zasebno te se optimizira njegov dizajn sa ciljem poboljšanja faktora potiskivanja zajedničkog signala diferencijskog mjernog sustava. Koristi se iterativni pristup istraživanju pri čemu se rezultati mjerenja, elektromagnetskih i sklopovskih simulacija kombiniraju sa ciljem poboljšanja karakterizaciju i modeliranje višeprolaznih sklopova na visokim frekvencijama. Diferencijski sklopovi karakteriziraju se mjerenjem mješovitih raspršnih parametara (engl. *scattering parameters* – S-parameters). Karakterizira se prijenos diferencijskog signala, zajedničkog signala te faktor potiskivanja zajedničkog signala (engl. *common-mode rejection ratio* – CMRR).

Sklop sonde sastoji se od tri osnovna dijela: atenuatora, lasera i sklopa za napajanje. Svaki dio sonde karakterizira se mjerenjem, provođenjem elektromagnetskih i sklopovskih simulacija te modeliranjem. Dizajn svakog dijela sklopa sonde optimizira se sa ciljem poboljšanja faktora potiskivanja zajedničkog signala sustava. Jednostavan mjerni sustav niske cijene može se implementirati u obliku samostalne sonde ili kao dio mjernog okruženja za karakterizaciju i ispitivanje integriranih sklopova. Sustav je projektiran za karakterizaciju valnih oblika elektrostatskih izboja te se može koristiti i za mjerenje elektromagnetske kompatibilnosti (engl. *electromagnetic compatibility* – EMC).

Predstavljene su metode za karakterizaciju višeprolaznih sklopova na visokim frekvencijama mjerenjem raspršnih parametara. Mješoviti S-parametri prikladniji su za karakterizaciju diferencijskih (simetričnih) sklopova nego tradicionalni asimetrični (engl. *single-ended*) S-parametri. Tradicionalni vektorski analizatori mreža projektirani su za mjerenje asimetričnih S-parametara. Čistomodni vektorski analizator mreža (engl. *pure-mode vector network analyzer*) predstavlja koncept za izravno mjerenje mješovitih S-parametara. Iako ne postoje komercijalno dostupni uređaji tog tipa, umjesto toga mogu se koristiti vektorski analizatori mreža s dva generatora. Provodi se usporedba različitih mjernih metoda analizom tipičnih sklopova koji se karakteriziraju u sklopu istraživanja. Usporedbom mjerenja provedenih koristeći tradicionalni četveroprolazni vektorski analizator mreža, četveroprolazni vektorski analizator mreža s dva generatora te tradicionalni dvoprolazni vektorski analizator mreža, demonstrirana je dobra ponovljivost rezultata mjerenja karakteristika diferencijskog i zajedničkog signala. Većina mjerenja u sklopu istraživanja provedena je koristeći dvoprolazni vektorski analizator mreža.

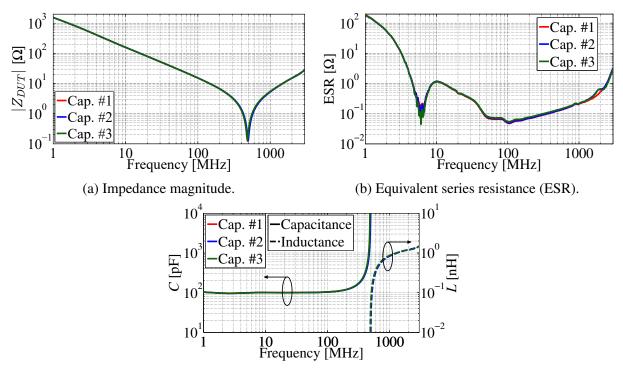

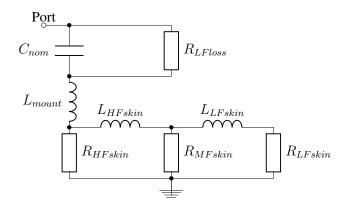

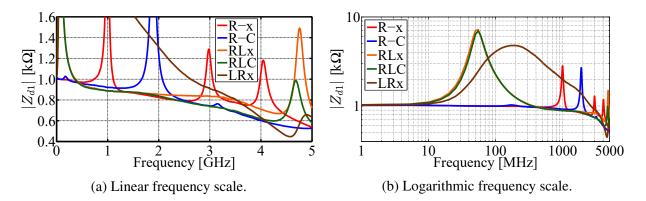

Prezentirana je serijska i paralelna (engl. *shunt*) metoda karakterizacije sklopova. Glavna prednost serijske metode karakterizacije je mogućnost ekstrahiranja parazita prema masi, dok je paralelna metoda prikladnija za karakterizaciju sklopova niske impedancije. Ekstrahirani su nadomjesni modeli otpornika i kondenzatora za površinsku montažu (engl. *surface-mount technology* – SMT) korištenih u atenuatorskom sklopu. Demonstrirano je da otpornici s višim nominalnim otporom imaju veći pad impedancije pri frekvencijama u gigahercnom području, kao posljedica utjecaja parazita. Višeslojni keramički kondenzator namijenjen za upotrebu u RF sustavima modeliran je koristeći dvoprolaznu paralelnu metodu karakterizacije. Ekstrahirani model precizno opisuje utjecaj skin-efekta u frekvencijskom pojasu do 2 GHz.

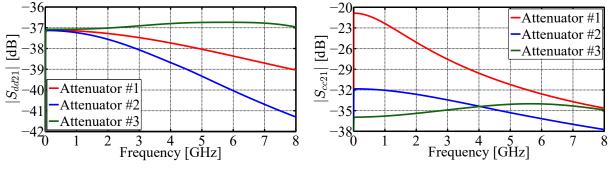

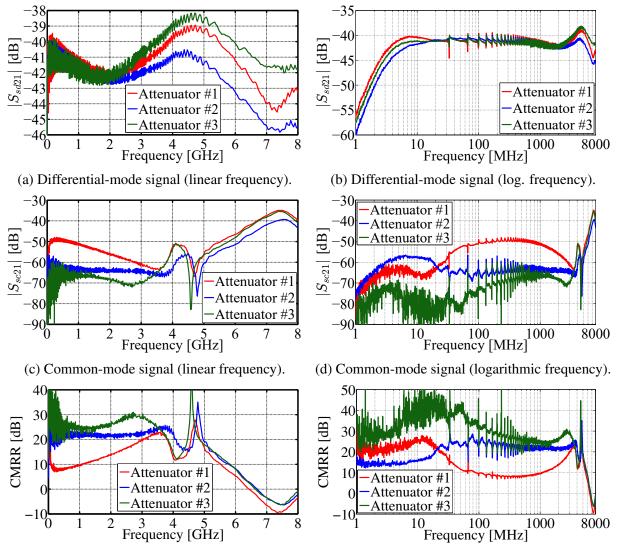

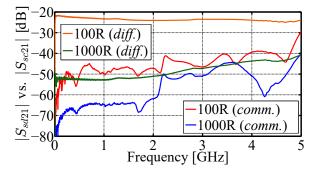

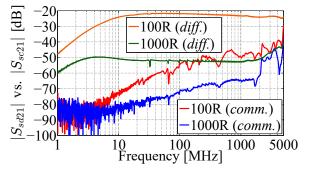

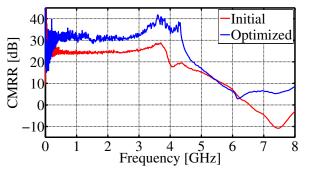

Atenuatorski sklop se koristi za prigušenje ulaznog RF signala. Izborom vrijednosti otpornika korištenih u atenuatorskom sklopu namješta se faktor atenuacije elektrooptičkog sklopa sonde. Izlazni napon atenuatora ograničen je maksimalnom dopuštenom razinom signala na laserskoj diodi uz koji laser još uvijek radi u linearnom području. Provode se elektromagnetske simulacije i mjerenja S-parametara više iteracija dizajna atenuatorskog sklopa. Unapređuje se stabilnost prigušenja diferencijskog i zajedničkog signala te se smanjuje pretvorba modova. Različite iteracije atenuatorskog sklopa uspoređuju se mjerenjem sklopova sonde s implementiranim različitim verzijama dizajna atenuatora. Optimizacijom dizajna atenuatorskog sklopa faktor potiskivanja zajedničkog signala uvećan je za 10 dB do 20 dB.

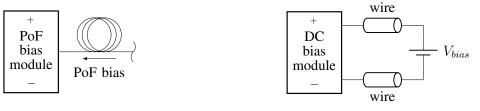

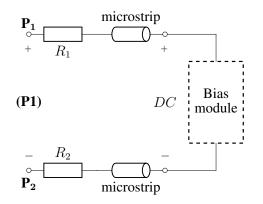

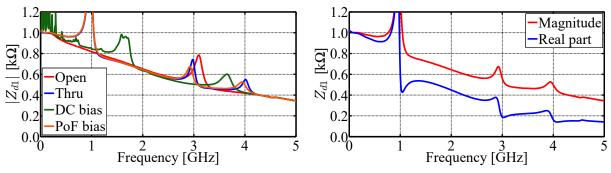

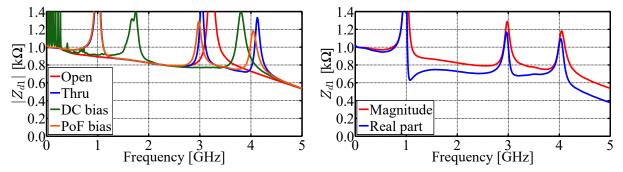

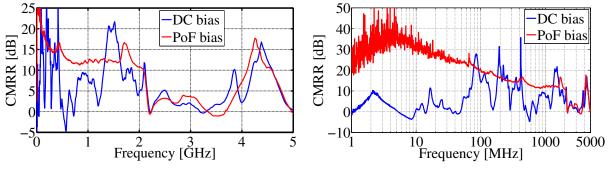

Laserska dioda koristi se za pretvorbu izmjerenog RF signala u optički signal. Na taj način poboljašava se otpornost elektrooptičkog mjernog sustava na elektromagnetske smetnje. Koristi se laser s vertikalnom rezonantnom šupljinom (engl. *vertical-cavity surface-emitting laser* – VCSEL) zbog širokog frekvencijskog pojasa, malih dimenzija i mase te niske cijene. Diferencijski RF signal dovodi se na ulaz lasera između anode i katode. Radna točka lasera postavlja se u središte linearnog područja kako bi laser mogao raditi s maksimalnim amplitudama ulaznog signala. Izolirani modul za napajanje (engl. *power-over-fiber* – PoF) i neizolirani modul za napajanje koji je izravno spojen na izvor napajanja karakteriziraju se mjerenjem diferencijske ulazne impedancije. Korištenjem izoliranog napajanja postiže se potpuna galvanska izolacija elektrooptičkog mjernog sustava te se potiskuju smetnje koje dolaze iz izvora napajanja.

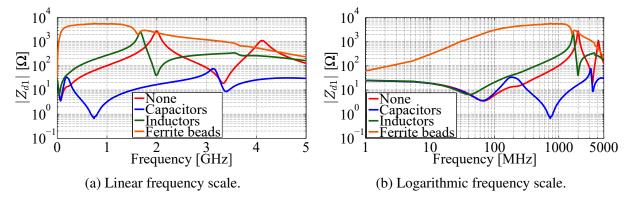

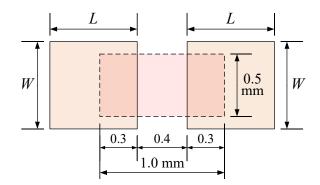

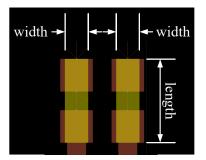

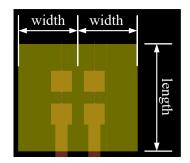

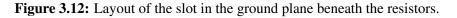

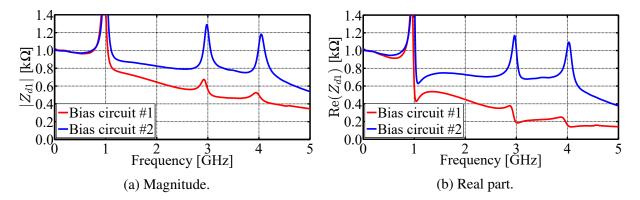

Projektira se diferencijski sklop za napajanje koji se koristi za postavljanje statičke radne točke laserske diode. Projektira se više iteracija dizajna sklopa za napajanje koje se karakteriziraju provođenjem elektromagnetskih simulacija i mjerenjem diferencijske ulazne impedancije. Najbolje performanse postižu se korištenjem serijske kombinacije ferita i otpornika na ulazu u sklop za napajanje. Na ovaj način koriste se prednosti oba tipa pasivnih komponenata kako bi se postigla visoka ulazna impedancija u širokom pojasu frekvencija. Paraziti se dodatno smanjuju dodavanjem proreza u masi ispod pasivnih komponenata i smanjenjem dimenzija lemnih mjesta (engl. *pad*).

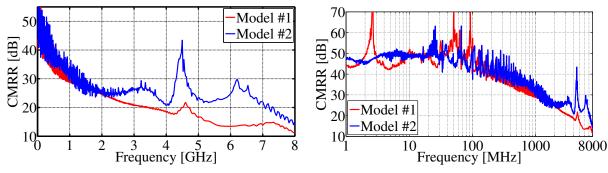

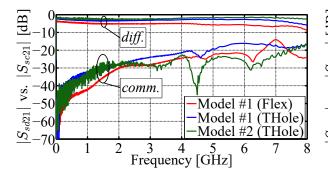

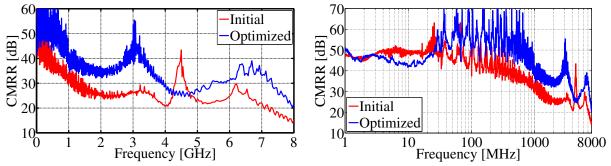

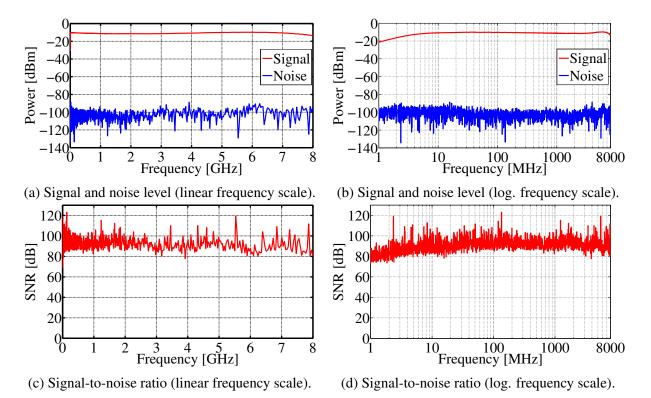

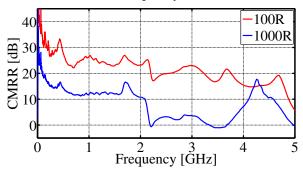

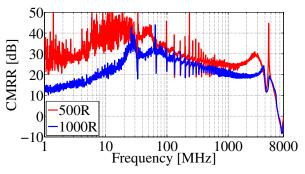

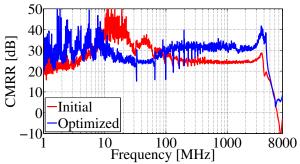

Karakteriziraju se laseri različitih proizvođača i u različitim tipovima pakiranja. Mjeri se prijenos diferencijskog i zajedničkog signala te faktor potiskivanja zajedničkog signala. Korištenjem prospojnog (engl. *through-hole*) pakiranja lasera ostvaruje se najbolja kombinacija faktora potiskivanja zajedničkog signala, mehaničke robusnosti i ponovljivosti karakteristika lasera. Izolacija napajanja nema značajan utjecaj na performanse karakteriziranog lasera. Ekstrahiran je diferencijski nadomjesni model lasera koji se koristi za modeliranje prijenosa diferencijskog i zajedničkog signala te faktora potiskivanja zajedničkog signala. Demonstriran je utjecaj asimetrije parazita prema masi na faktor potiskivanja zajedničkog signala karakteriziranog lasera. Optimizirana je topologija laserskog sklopa te je poboljšan faktor potiskivanja zajedničkog signala. Ostvaren je faktor potiskivanja zajedničkog signala od 30 dB u frekvencijskom pojasu do 3.9 GHz. Karakterizirani laser koristi se u elektrooptičkom sklopu sonde. Odnos signal-šum (engl. *signal-to-noise ratio* – SNR) lasera ovisi o odnosu signal-šum fotodetektora korištenog za mjerenje te ograničava odnos-signal šum elektrooptičkog sklopa sonde.

Početna verzija dizajna sklopa sonde implementirana je na plivajućoj sondi za mjerenje wafera. Ispitane su različite verzije sklopa sonde te su poboljšanja dizajna atenuatorskog sklopa, topologije laserske diode i sklopa za napajanje implementirana u dizajn sklopa sonde. Karakterizirani su sklopovi sonde s različitim stupnjevima atenuacije. Općenito vrijedi, što je niži stupanj atenuacije sonde, to viši faktor potiskivanja zajedničkog signala može biti postignut. Ovo je posljedica činjenice da zajednički signal ne može biti prigušen u istoj mjeri kao i diferencijski signal, zato što postoji doprinos zajedničkom signalu koji nije ovisan o stupnju atenuacije. Korištenje otpornika s nižim nominalnim otporom također rezultira stabilnijim prijeno-som diferencijskog signala u širokom pojasu frekvencija i širim 3 dB frekvencijskim opsegom sondi s nižim stupnjem atenuacije. Prisutne su razlike do 5 dB u iznosu faktora potiskivanja zajedničkog signala između sklopova sonde s identičnim topologijama. To je posljedica tolerancija između pasivnih komponenata korištenih u sklopu sonde, laserskih dioda i parazita unesenih procesom lemljenja. Bolju ponovljivost karakteristika između uzoraka sondi moguće je ostvariti korištenjem profesionalnog postupka lemljenja i sastavljanja. Ovo pokazuje utjecaj postupka lemljenja i sastavljanja tiskanih pločica na ponovljivost karakteristika sklopa sonde.

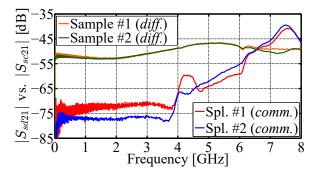

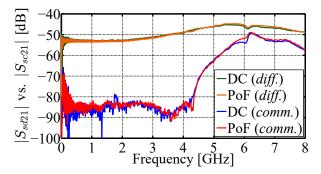

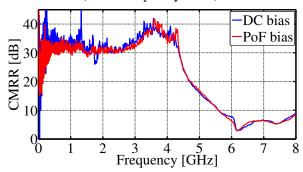

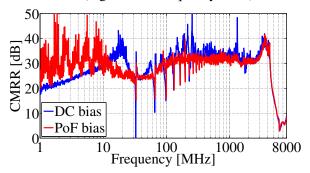

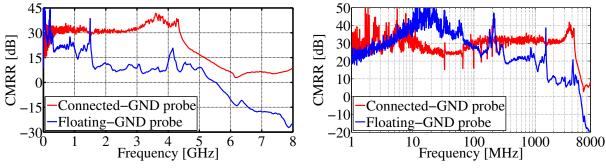

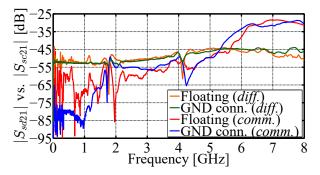

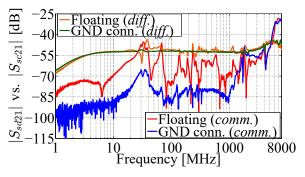

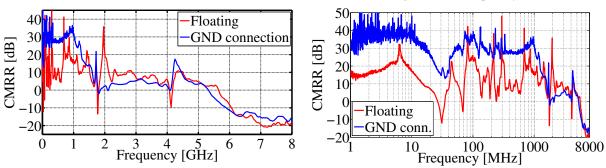

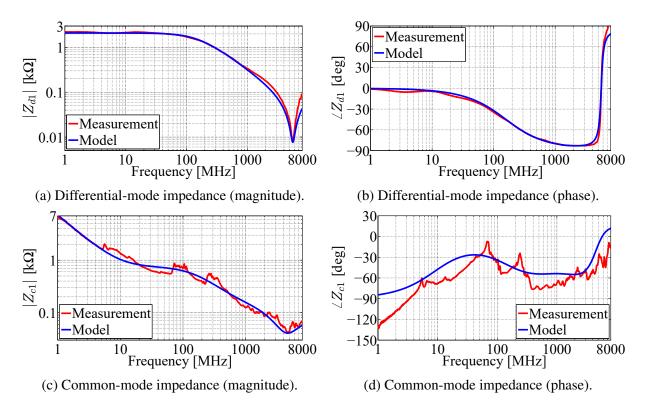

Topologija sklopa sonde optimizirana je sa ciljem poboljšanja faktora potiskivanja zajedničkog signala. Optimizirana topologija sklopa sonde implementirana je na diferencijskoj sondi s pristupnom strukturom s konektorima i spojenom masom te potpuno plivajućoj diferencijskoj sondi za mjerenje wafera. Unatoč razlikama u pristupnim strukturama i priključcima mase, obje sonde realizirane su u diferencijskoj konfiguraciji gdje se signal diferencijski dovodi na laser. Sonde su projektirane za diferencijska mjerenja valnih oblika elektrostatskih izboja s amplitudama do 100 V (200 V<sub>PP</sub>). Iako se pri radu s elektrostatskim izbojima ne očekuje značajna disipacija snage, maksimalna dopuštena razina efektivnog napona iznosi 14.1 V. Faktor potiskivanja zajedničkog signala sonde za mjerenje wafera s optimiziranim dizajnom sklopa sonde je 10 dB viši u usporedbi s početnim dizajnom sklopa sonde. Spoj sonde prema masi nema značajan utjecaj na prijenos diferencijskog signala, dok je utjecaj na prigušenje zajedničkog signala vrlo značajan. Znatno viši faktor potiskivanja zajedničkog signala postiže se kad je prisutna dobro definirana referenca mase. Sonda sa spojenom masom i plivajuća sonda imaju sličan 3 dB frekvencijski pojas od 3.5 GHz. Međutim, sonda sa spojenom masom ima faktor potiskivanja zajedničkog signala iznad 30 dB u frekvencijskom pojasu do 4.4 GHz, dok plivajuća sonda ima faktor potiskivanja zajedničkog signala iznad 20 dB u frekvencijskom pojasu do 1 GHz.

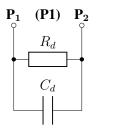

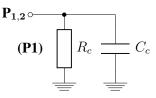

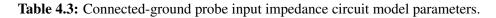

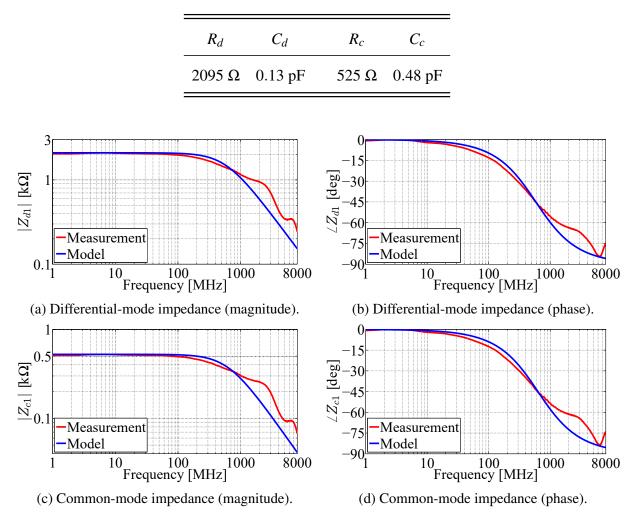

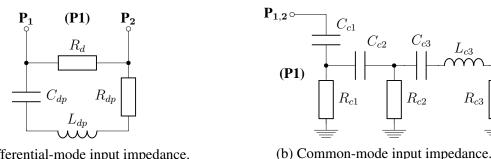

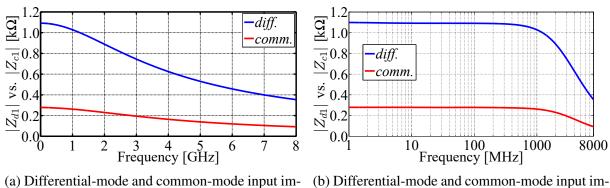

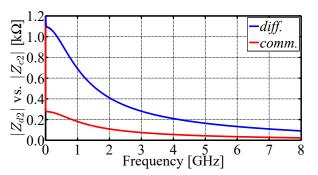

Ispitan je utjecaj izoliranog napajanja na performanse sondi u obliku smetnji u prijenosu diferencijskog i zajedničkog signala. Utjecaj smetnji koje dolaze iz neizoliranog izvora napajanja i sprege smetnji na električne vodove je relativno malen za sonde sa spojenom masom. Međutim, izolacija napajanja je kritična za u potpunosti plivajuće diferencijske sonde, s obzirom da značajno smanjuje razinu smetnji u prijenosu diferencijskog, a posebno u prijenosu zajedničkog signala. Osim znatno višeg faktora potiskivanja zajedničkog signala u širokom pojasu frekvencija, sonda sa spojenom masom ima i višu i stabilniju diferencijsku i zajedničku ulaznu impedanciju na visokim frekvencijama, uz vrlo nizak parazitni kapacitet. Nominalna diferencijska ulazna impedancija sonde sa spojenom masom iznosi 2095  $\Omega$  s parazitnim kapacitetom od 0.13 pF, dok nominalna zajednička ulazna impedancija iznosi 525  $\Omega$  s parazitnim kapacitetom od 0.48 pF. Prezentirani jednostavan dizajn sklopa sonde niske cijene moguće je minijaturizirati i implementirati na sondama s različitim tipovima pristupnih struktura i primjenama u sustavima za mjerenje elektrostatskih izboja i elektromagnetske kompatibilnosti.

Brzi pad faktora potiskivanja zajedničkog signala na visokim frekvencijama prisutan je kod svih karakteriziranih sklopova sonde, neovisno o topologiji sklopa sonde i stupnju atenuacije signala. Ovo pokazuje fundamentalno ograničenje dizajna sklopa sonde. Takav pad u faktoru potiskivanja zajedničkog signala nije prisutan u karakteristikama atenuatora i lasera karakteriziranih zasebno. Pad u faktoru potiskivanja zajedničkog signala na visokim frekvencijama rezultat je interakcije između propagacije diferencijskog i zajedničkog signala kroz atenuator i laser, u kombinaciji s prilagođenjem diferencijske i zajedničke impedancije između ta dva sklopa. Faktor potiskivanja zajedničkog signala elektrooptičke sonde moguće je poboljšati optimizacijom izlazne impedancije atenuatora i ulazne impedancije lasera. Kontroliranjem impedancija moguće je sniziti razinu zajedničkog signala na ulazu u laser, u odnosu na razinu diferencijskog signala, na taj način povećavajući faktor potiskivanja zajedničkog signala.

Razvijen je diferencijski elektrooptički sustav za mjerenje napona koji ima dobre karakteristike u frekvencijskom području do nekoliko gigaherca. Sustav koristi jednostavan dizajn sklopa sonde niske cijene. Optička veza koristi se i za radiofrekvencijski signal i za signal napajanja, sa ciljem galvanske izolacije sustava, dopuštajući mu rad u elektromagnetski zagađenoj okolini. Prikazana su ograničenja sustava u smislu stabilnosti prijenosa diferencijskog signala i pada u faktoru potiskivanja zajedničkog signala na visokim frekvencijama. Predložene su izmjene za daljnja unaprjeđenja dizajna svakog dijela sklopa sonde. Umjesto fokusiranja na niske frekvencije pod cijenu performansi na visokim frekvencijama, ostvaren je stabilniji frekvencijski profil faktora potiskivanja zajedničkog signala. Navedene karakteristike postižu se pojednostavljenjem dizajna sklopa, koristeći samo neophodne komponente, što umanjuje fizičke dimenzije sustava, poboljšava performanse i snižava cijenu. Uz karakterizaciju valnih oblika elektrostatskih izboja, razvijeni dizajn sklopa sonde može se prilagoditi i za primjene ispitivanja elektromagnetske kompatibilnosti. Predloženi dizajn omogućava eksperimentiranje s različitim tipovima pristupnih struktura kako bi se smanjile dimenzije sonde, koju bi bilo moguće integrirati u okolinu za ispitivanje integriranih sklopova.

Znanstveni doprinos doktorskog rada:

- Metodologija za modeliranje elektrooptičkih sklopova i karakterizaciju odziva na diferencijske i zajedničke signale kombinacijom admitancijskih parametara i mješovitih raspršnih parametara.

- 2. Diferencijski elektrooptički nadomjesni model lasera s vertikalnom rezonantnom šupljinom za procjenu faktora potiskivanja zajedničkog signala.

- 3. Projektiranje i karakterizacija višeprolaznih širokopojasnih elektrooptičkih diferencijskih sondi za mjerenje napona u elektromagnetski zagađenoj okolini.

- 4. Usporedna analiza diferencijskih elektrooptičkih naponskih sondi s plivajućom masom i sa spojenom masom za rad u gigahercnom frekvencijskom području.

**Ključne riječi**: atenuator, modeliranje sklopova, faktor potiskivanja zajedničkog signala (CMRR), zajednički signal, diferencijsko mjerenje napona, diferencijski signal, elektrooptički sustav, elektromagnetska kompatibilnost (EMC), elektrostatski izboj (ESD), otpornost na smetnje, power-over-fiber (PoF), laser s vertikalnom rezonantnom šupljinom (VCSEL)

# Contents

| 1. | Intr | oductio                                  | <b>n</b>                                                    | 1  |  |  |  |

|----|------|------------------------------------------|-------------------------------------------------------------|----|--|--|--|

|    | 1.1. | Introdu                                  | action and overview of the conducted research               | 2  |  |  |  |

|    | 1.2. | 2. Scientific contribution of the thesis |                                                             |    |  |  |  |

|    | 1.3. | e of the thesis                          | 5                                                           |    |  |  |  |

| 2. | Mul  | tiport n                                 | neasurement methodology and design of attenuator structures | 7  |  |  |  |

|    | 2.1. | Measurement methodology                  |                                                             |    |  |  |  |

|    |      | 2.1.1.                                   | S-parameters                                                | 9  |  |  |  |

|    |      | 2.1.2.                                   | S-parameter measurements                                    | 16 |  |  |  |

|    |      | 2.1.3.                                   | Measurement methodology verification                        | 20 |  |  |  |

|    |      | 2.1.4.                                   | Modelling methodology                                       | 25 |  |  |  |

|    | 2.2. | Passive                                  | e component modelling                                       | 30 |  |  |  |

|    |      | 2.2.1.                                   | RF resistor modelling                                       | 30 |  |  |  |

|    |      | 2.2.2.                                   | RF capacitor modelling                                      | 32 |  |  |  |

|    | 2.3. | Attenu                                   | ator circuit                                                | 39 |  |  |  |

|    |      | 2.3.1.                                   | Initial attenuator circuit design                           | 39 |  |  |  |

|    |      | 2.3.2.                                   | Attenuator circuit design optimization                      | 42 |  |  |  |

|    | 2.4. | Summ                                     | ary                                                         | 48 |  |  |  |

| 3. | Lase | Laser diode characterization             |                                                             |    |  |  |  |

|    | 3.1. | Introdu                                  | uction to laser diode characterization                      | 50 |  |  |  |

|    | 3.2. | Laser bias circuit                       |                                                             | 53 |  |  |  |

|    |      | 3.2.1.                                   | Laser DC characterization                                   | 53 |  |  |  |

|    |      | 3.2.2.                                   | Bias modules                                                | 54 |  |  |  |

|    |      | 3.2.3.                                   | Bias circuit #1 layout                                      | 58 |  |  |  |

|    |      | 3.2.4.                                   | Bias circuit #2 layout                                      | 60 |  |  |  |

|    |      | 3.2.5.                                   | Bias circuit #3 layout                                      | 65 |  |  |  |

|    |      | 3.2.6.                                   | Bias circuit #4 layout                                      | 69 |  |  |  |

|    | 3.3. | Laser o                                  | diode RF characterization                                   | 72 |  |  |  |

|                  |      | 3.3.1.   | Laser package comparison                                           |  |  |  |  |

|------------------|------|----------|--------------------------------------------------------------------|--|--|--|--|

|                  |      | 3.3.2.   | Laser model comparison                                             |  |  |  |  |

|                  |      | 3.3.3.   | Laser model and package comparison                                 |  |  |  |  |

|                  |      | 3.3.4.   | Laser power supply isolation                                       |  |  |  |  |

|                  | 3.4. | Laser e  | equivalent circuit model                                           |  |  |  |  |

|                  |      | 3.4.1.   | Measurement                                                        |  |  |  |  |

|                  |      | 3.4.2.   | Electrical circuit model                                           |  |  |  |  |

|                  |      | 3.4.3.   | Electro-optical circuit model                                      |  |  |  |  |

|                  | 3.5. | Optimi   | zed laser layout                                                   |  |  |  |  |

|                  |      | 3.5.1.   | Signal-to-noise ratio                                              |  |  |  |  |

|                  | 3.6. | Summa    | ary                                                                |  |  |  |  |

| 1                | Proh | o circui | it design and characterization                                     |  |  |  |  |

| ч.               |      |          | circuit development                                                |  |  |  |  |

|                  | 7.1. | 4.1.1.   |                                                                    |  |  |  |  |

|                  |      |          | Probe circuit                                                      |  |  |  |  |

|                  | 42   |          | zed probe layout                                                   |  |  |  |  |

|                  | 1.2. | -        | Connected-ground probe                                             |  |  |  |  |

|                  |      | 4.2.2.   | Floating-ground probe                                              |  |  |  |  |

|                  |      |          | Probe comparison                                                   |  |  |  |  |

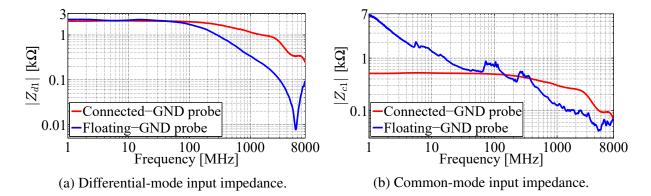

|                  | 4.3. |          | nput impedance characterization                                    |  |  |  |  |

|                  |      | 4.3.1.   | Connected-ground probe                                             |  |  |  |  |

|                  |      | 4.3.2.   | Floating-ground probe                                              |  |  |  |  |

|                  |      | 4.3.3.   | Probe comparison                                                   |  |  |  |  |

|                  | 4.4. | Discus   | sion of common-mode rejection ratio measurements                   |  |  |  |  |

|                  |      | 4.4.1.   | Common-mode rejection ratio definitions                            |  |  |  |  |

|                  |      | 4.4.2.   | Probe circuit impedance matching                                   |  |  |  |  |

|                  |      | 4.4.3.   | Impact of circuit asymmetry on the common-mode rejection ratio 154 |  |  |  |  |

|                  | 4.5. | Probe t  | ime domain measurements                                            |  |  |  |  |

|                  | 4.6. | Summa    | ary                                                                |  |  |  |  |

| 5.               | Con  | clusion  |                                                                    |  |  |  |  |

| Bibliography     |      |          |                                                                    |  |  |  |  |

| <b>Biography</b> |      |          |                                                                    |  |  |  |  |

| Životopis        |      |          |                                                                    |  |  |  |  |

# **Chapter 1**

# Introduction

## **1.1 Introduction and overview of the conducted research**

Electrostatic discharges (ESD) are fast pulses with a typically high maximum voltage. These fast pulses have a wide bandwidth that is usually in the gigahertz range, and can create electromagnetic interference in the measurement system [1]. In particular, system-level ESD pulses contain information in the frequency band up to 5 GHz [2]. Given the short duration of ESD pulses, their average power is not a concern. With the continuous development of electronic devices there is a constant need for improvement of ESD protection. The ability to measure ESD voltage waveforms in a simple and practical way provides useful information to integrated circuit designers. It furthers the understanding of the mechanisms of ESD propagation, and allows for improvement of ESD suppression and protection techniques in electronic devices.

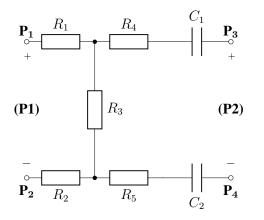

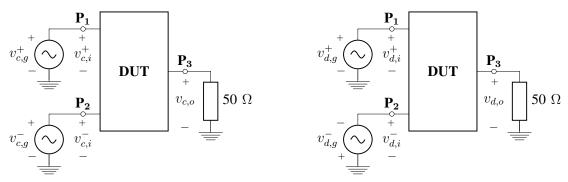

Standard electrical probes are susceptible to coupling of electromagnetic noise on the measurement system. Differential circuits have a more robust topology compared to single-ended circuits. Their main advantage is lower sensitivity to system noise and reduced generation of transient noise [3]. A general schematic of a single-ended device is presented in Fig. 1.1a. The device has two physical ports:  $P_1$  and  $P_2$ . In a single-ended system, the signal at each port is referenced to the ground. Single-ended systems are sensitive to interference, because the unwanted signal is directly superposed to the wanted signal, and the two signals are indistinguishable. Additionally, any interference in the ground reference is superposed to signals at all ports sharing the same ground reference.

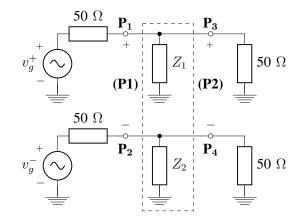

In a differential system, a pair of physical ports forms a logical differential (balanced) port. The signal at the logical differential port is defined as the difference between the signals at the two physical ports. The idea behind differential signaling is that if two traces are physically close to each other, the same interference is picked up by both signals. Given that the interference is common to both signals, it is cancelled out by making a difference of the two signals. A general schematic of a differential device is presented in Fig. 1.1b. The device shown has four physical ports. The physical ports  $P_1$  and  $P_2$  form the logical differential port (P1), while the physical ports  $P_3$  and  $P_4$  form the logical differential port (P2). Differential-mode or common-mode stimulus can be applied to a balanced port. A differential-mode signal is created by two counter-phase signals with the same magnitude, applied to the two physical ports that

(a) Single-ended device under test.

(b) Differential device under test.

Figure 1.1: Schematic of a single-ended and a differential device under test.

form the balanced port. A common-mode signal is created by two in-phase signals with the same magnitude, applied to the two physical ports that form the balanced port. The differential-mode signal typically presents the wanted signal, while the common-mode signal typically presents the unwanted signal in the differential system. The ratio between the transmission of the wanted differential-mode signal and the unwanted common-mode signal is called the common-mode rejection ratio (CMRR).

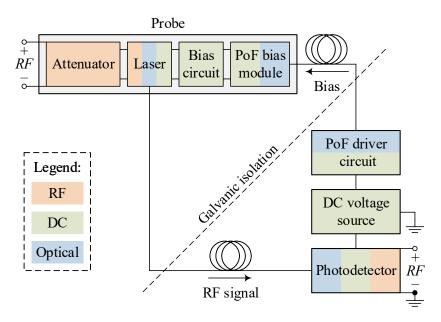

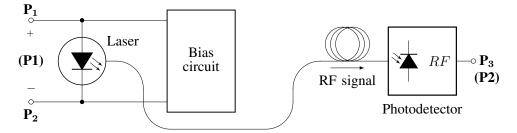

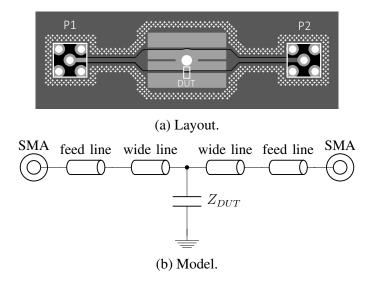

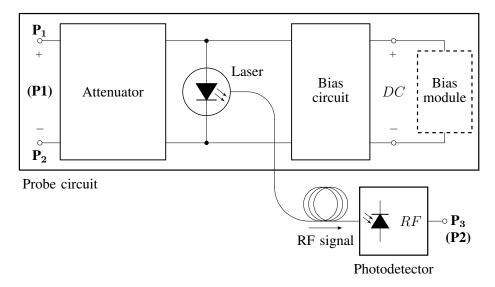

An effective way of making a measurement system more resistant to electromagnetic interference is using electro-optical probes. A general concept of an electro-optical voltage measurement system is presented in Fig. 1.2. In an electro-optical measurement system, the signal acquisition and signal processing stage of the system are separated, achieving galvanic isolation of the measurement system. In this way, the electromagnetic interference present in the measurement environment does not impact the signal processing stage of the system, where the signal obtained using the electro-optical probe is typically digitized using a high speed oscilloscope, or a similar instrument.

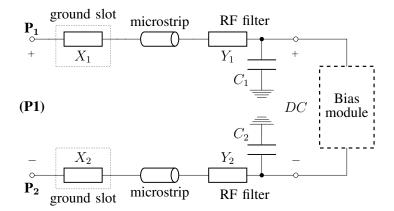

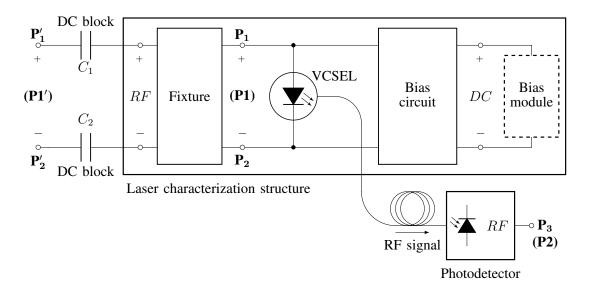

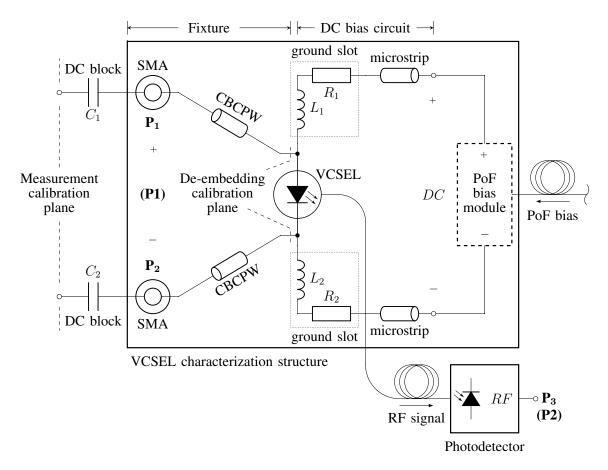

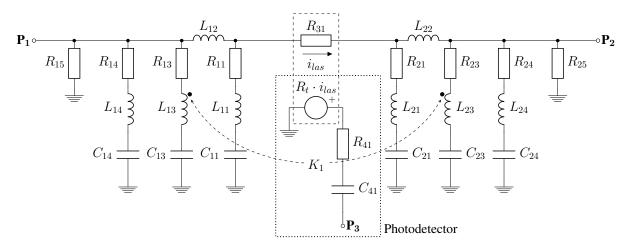

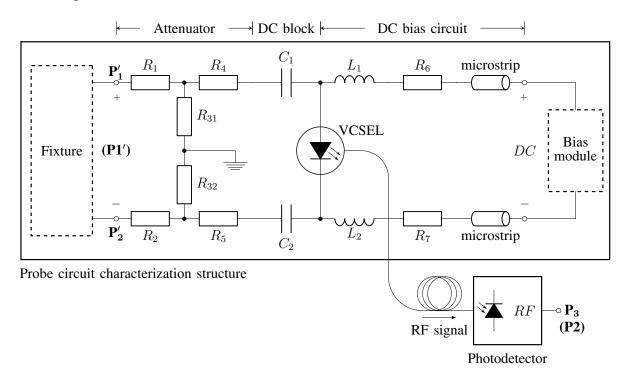

The electro-optical measurement system consists of three key parts: the attenuator, the laser and the bias circuit. The attenuator is used to lower the input signal level in order not to overdrive the laser. The laser converts the measured radio frequency (RF) signal into an optical signal, which is transmitted to the photodetector in the signal processing part of the system. The bias circuit is used to set the operating point of the laser. Fully isolated electro-optical probes also use an optical connection for the power-over-fiber (PoF) power supply.

Figure 1.2: Differential electro-optical voltage measurement system schematic.

The general concept of electro-optical ESD probes is presented in [4]. Electro-optical probes are most commonly implemented as contactless probes for electric and magnetic field sensing [5-12]. Such probes can be used for measuring radiated emissions for electromagnetic

compatibility (EMC) analysis. The spectrum required by EMC standards for measurements of electromagnetic emissions of integrated circuits is up to 1 GHz, and is expected to be extended in the future [13]. Precise measurements of ESD voltage waveforms require contact measurements to be performed. Given the interference that can be generated by ESD pulses, ESD probes need to be designed to operate in an electromagnetically polluted environment. Using the benefits of a differential circuit topology and an electro-optical measurement system provides the highest level of noise immunity. A circuit design of a differential electro-optical ESD voltage probe is proposed in [2].

This thesis presents the development of a broadband electro-optical differential voltage measurement system. The goal is to develop a simple and low-cost differential system with a stable common-mode rejection ratio up to several gigahertz. While most of the practice in ESD focuses on the quasi-static behaviour, when the ESD pulse has stabilized, the presented system is developed with the goal of being able to investigate the transients and the related risk of overshoots in more detail. The measurement system can be adjusted for different fixture types and is suitable for on-chip ESD waveform characterization, as well as for characterization of waveforms in certain EMC applications.

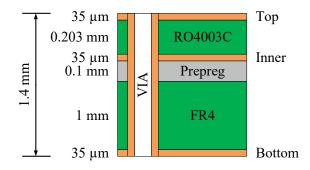

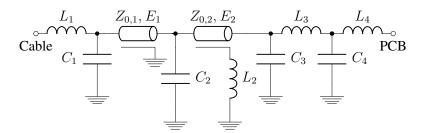

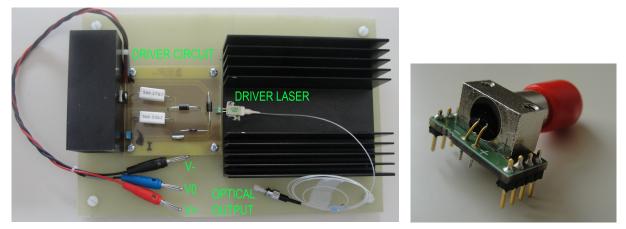

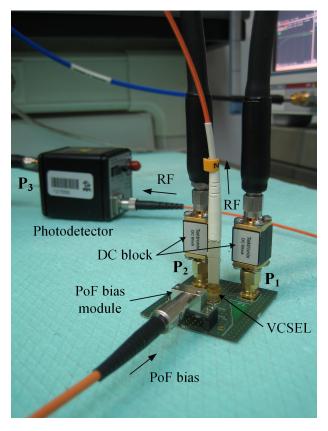

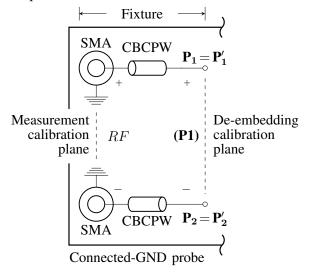

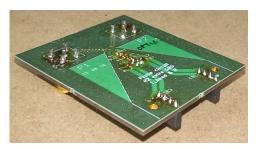

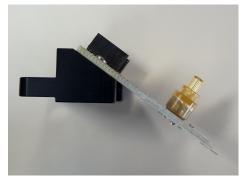

The probe circuit is realized on a three-layer printed circuit board (PCB), shown in Fig. 1.3. The PCB stack-up uses a combination of an RF Rogers RO4003C substrate and a thicker FR4 substrate. The Rogers RF substrate is used for routing the RF transmission lines, and for placing all the components of the attenuator and the bias circuit. The FR4 substrate is used for mechanical stability of the PCB, and for placing the laser diode and the bias module. The PCB stack-up and dimensions are based on the |Z| Probe® PCB layout. The |Z| Probe® is a type of a broadband wafer probe designed for high-accuracy measurements, with low contact resistance and good impedance control [14]. The same PCB stack-up is used for all the characterization structures designed to evaluate the performance of the parts of the electro-optical probe circuit.

**Figure 1.3:** Characterization PCB stack-up schematic. The copper layers are marked in orange and the dielectric layers are marked in green color (dimensions are not in scale).

The research is conducted by characterizing each individual part of the electro-optical measurement system separately. The design of each part of the electro-optical system is optimized in order to improve the performance of the probe circuit. Circuit simulations, electromagnetic simulations, and measurements are used to analyze the performance of the individual parts of the probe circuit design. Equivalent circuit models of the components used in the probe circuit are developed. The response of the probe circuit to differential-mode and common-mode input signals is evaluated, as well as the common-mode rejection ratio. The improvements made to the individual parts of the measurement system are implemented into the probe circuit design. Multiple layouts of the probe circuit are characterized and the probe circuit layout is optimized. The optimized probe circuit layout is implemented on a connectorized probe with a well-defined ground connection, as well as a fully floating wafer probe. The performance of the probes is analyzed, as well as the impact of the ground connection and power supply isolation, on the probe performance. Potential areas for performance improvement of the elements of the electro-optical measurement system are suggested.

## **1.2** Scientific contribution of the thesis

The scientific contribution of the thesis is:

- 1. Methodology combining admittance parameters and mixed-mode scattering parameters for modelling electro-optical devices and for characterizing differential-mode and common-mode response.

- 2. Differential electro-optical equivalent circuit model of a vertical-cavity surface-emitting laser for common-mode rejection ratio estimation.

- 3. Design and characterization of multiport broadband electro-optical differential probes for voltage measurements in an electromagnetically polluted environment.

- 4. Comparative analysis of the floating-ground and connected-ground differential electro-optical voltage probes operating in GHz-range.

### **1.3** Outline of the thesis

The thesis is organized in five chapters.

Chapter 2 presents the different measurement methodologies used to characterize and model multiport circuits. The passive components used in the attenuator circuit are characterized, and their circuit models are extracted. Different attenuator circuit topologies are designed and characterized. The attenuator circuit design is optimized in order to improve the attenuation of the wanted differential-mode signal and the suppression of the unwanted common-mode signal.

Chapter 3 presents the design and characterization of the laser bias circuit, as well as the bias modules used to set the operating point of the laser diode. Laser diodes from different manufac-

turers and in different package types are characterized. The equivalent circuit model of the laser diode used is extracted. Based on the analysis of the circuit model, the laser layout is optimized in order to improve the common-mode rejection ratio. The optimized laser layout is characterized and the signal-to-noise ratio of the electro-optical measurement system is evaluated.

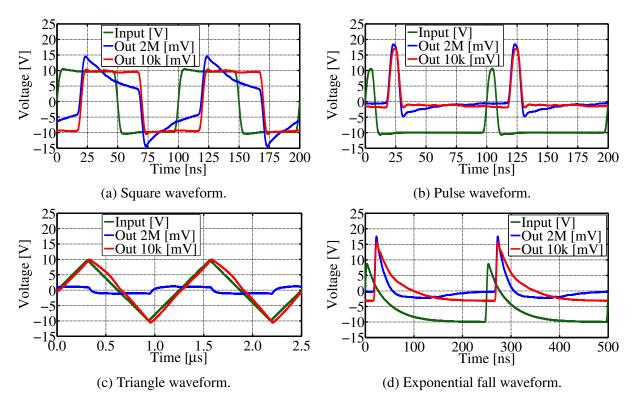

Chapter 4 presents the development of the probe circuit design, from the initial design implemented on the wafer probe, to the implementation of the improvements made to the circuit elements on the probe circuit characterization structure. The probe circuit layout is optimized and implemented on two probes with different fixtures and ground connection types. The probes are characterized by measuring the differential-mode and common-mode signal transmission, as well as the common-mode rejection ratio. The input impedance characteristics of the two probes are analyzed and modelled. The impact of impedance matching between the elements of the probe circuit and the circuit symmetry on the common-mode rejection ratio is analyzed. Time domain measurements are performed using the developed electro-optical probe.

Chapter 5 concludes the thesis.

# Chapter 2

# Multiport measurement methodology and design of attenuator structures

This chapter explores the different measurement methodologies used for circuit characterization at high frequencies. The optimum method is selected based on the characterized circuits and components, and the available measurement equipment. Series and shunt characterization methods are described, which are used to extract equivalent circuit models. Equivalent circuit models of the resistors and capacitors used in the attenuator circuit are presented. The circuit models of the characterized components are used to perform electromagnetic and circuit simulations, and evaluate the proposed circuit designs. The attenuator circuit, located at the input of the probe circuit, must ensure that the laser diode is not overdriven by high input signal levels. Different attenuator circuit designs are simulated and measured. The best attenuator circuit design is selected based on the stability of the differential-mode signal attenuation, and suppression of the unwanted common-mode signal and the mode conversion.

This chapter is structured as follows. Section 2.1 presents the different measurement methodologies used to characterize and model multiport circuits. Section 2.2 explores the passive components used in the attenuator circuit and presents their equivalent circuit models. Section 2.3 discusses the design and characterization of different attenuator circuit topologies. The summary is given in Section 2.4.

This chapter is based on the following papers:

- [15] Blecic, R., Stimac, H., Gillon, R., Nauwelaers, B., Baric, A., "Improved Estimation of Radiated Fields of Unintentional Radiators by Correction of the Impedance Mismatch Between a Transverse Electromagnetic Cell and a Hybrid Coupler", IEEE Transactions on Electromagnetic Compatibility, Vol. 60, No. 6, Dec 2018, pp. 1717-1725.

- [16] Štimac, H., Blečić, R., Gillon, R., Barić, A., "Frequency-Domain Characterization and Modelling of a Multi-Layer Ceramic Capacitor for RF Applications", in 2019 Joint International Symposium on Electromagnetic Compatibility, Sapporo and Asia-Pacific International Symposium on Electromagnetic Compatibility (EMC Sapporo/APEMC), June 2019, pp. 285-288.

- [17] Bačmaga, J., Štimac, H., Gillon, R., Barić, A., "High-Frequency Characterization and Parametrized Modelling of DC-Biased Surface-Mount Ferrite Beads for EMI Suppression Applications", IEEE Transactions on Electromagnetic Compatibility, Vol. 62, No. 6, Dec 2020, pp. 2793-2803.

- [18] Bačmaga, J., Štimac, H., Barić, A., "Combined Series and Shunt Characterization for Accurate Resonant Frequency Extraction and Circuit Modelling of Surface-Mount Inductors", in 2020 IEEE 24th Workshop on Signal and Power Integrity (SPI), May 2020, pp. 1-4.

- [19] Bačmaga, J., Štimac, H., Barić, A., "Methodology for Characterization and Modelling of DC-Biased Surface-Mount Ferrite Power Inductors", in 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Nov 2020, pp. 1-7.

### 2.1 Measurement methodology

High frequency characterization of circuits presents a challenge, given that the standard characterization methods like measuring voltages and currents are not suitable at frequencies in the gigahertz range. Within this thesis a number of different multiport circuits and components are characterized. This includes two-port, three-port and four-port, both active and passive circuits and components. Given that working with differential-mode and common-mode signals is a central topic of the research presented in this thesis, most circuits are characterized as differential (balanced) circuits. However, single-ended circuits are characterized as well.

A number of measurement methods used for characterization and modelling of multiport circuits at high frequencies are explored. An introduction into the concept of single-ended and mixed-mode scattering parameters (S-parameters) is given. When differential-mode and common-mode stimulus is applied to circuits, mixed-mode S-parameters are often more useful than standard single-ended S-parameters. The series and shunt characterization methods are explored, as well as the application of these methods to extract equivalent circuit models.

The differences between a traditional vector network analyzer and a pure-mode vector network analyzer are explained. The pure-mode vector network analyzer is designed for measuring mixed-mode S-parameters directly. Methods for measuring multiport circuits using a more affordable two-port vector network analyzer are explored. Procedures for combining the results and error reduction are discussed. Methods for measuring mixed-mode S-parameters using a traditional vector network analyzer and external components like hybrid couplers, baluns and power dividers are described. The repeatability of measurement results using the same measurement method, as well as using different measurement methods is evaluated on practical examples of circuits characterized within the research presented in this thesis. The best characterization method is selected based on the measurement accuracy, the time required to perform the measurements, and the available measurement equipment.

#### 2.1.1 S-parameters

At high frequencies it is very difficult to measure voltages and currents directly. For that reason, scattering parameters are introduced. Standard S-parameters are useful when working with single-ended devices. For applications where differential (balanced) devices are used, the concept of mixed-mode scattering parameters is often more practical [20]. S-parameters are used for measuring linear networks. If active devices are characterized, they need to be measured in small-signal mode of operation.

#### **Single-ended S-parameters**

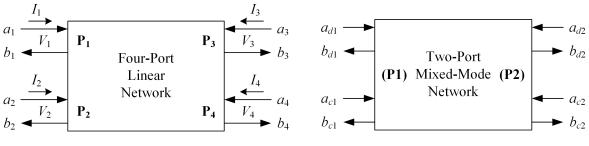

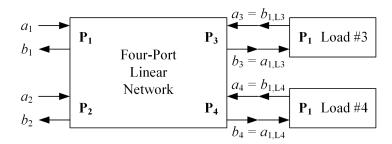

A device with four physical ports shown in Fig. 2.1 can be viewed as a single-ended device (Fig. 2.1a), or a mixed-mode device (Fig. 2.1b). When characterizing a device as a multiport single-ended device, the physical ports are stimulated one by one, while the other ports are terminated with a matched load. The reflected and transmitted traveling waves are measured. The concept of power waves is introduced in [21]. While traveling waves are physical, measurable and present the solution of Maxwell's equations, power waves are a theoretical concept used in the definition of S-parameters, and are a useful tool for achieving power matching [22]. For a device with *N* ports shown in Fig. 2.1a, the incident power wave  $a_i$  and the reflected power wave  $b_i$  at a certain port *i*, are defined using the voltage at the port  $V_i$ , the current flowing into the port  $I_i$ , and the reflected impedance of the port  $Z_i$  as follows [21]:

$$a_{i} = \frac{V_{i} + Z_{i}I_{i}}{2\sqrt{|\text{Re}\{Z_{i}\}|}}, \quad b_{i} = \frac{V_{i} - Z_{i}^{*}I_{i}}{2\sqrt{|\text{Re}\{Z_{i}\}|}}, \quad (2.1)$$

where  $Z_i^*$  represents the complex conjugate of the impedance  $Z_i$ . In general, the port impedance  $Z_i$  can be complex. The power wave definitions can be simplified if all ports share the same complex reference impedance  $Z_R$ . In practice,  $Z_R = Z_0$  is typically used, where  $Z_0$  represents the real characteristic impedance, which is typically set to 50  $\Omega$  [23].

(a) Four-port single-ended network.

(b) Two-port mixed-mode network.

**Figure 2.1:** Linear network with four physical ports represented in a single-ended configuration (left) and in a mixed-mode configuration with two logical ports (right).

The concept of S-parameters was first introduced in [24]. S-parameters are defined as the ratio between the reflected power wave at the port i and the incident power wave at the port j in an N-port linear network as follows [21, 25, 26]:

$$S_{ij} = \frac{b_i}{a_j} \bigg|_{a_k = 0, \ k \neq j}.$$

(2.2)

The power wave reflection coefficient looking into the port *i* is defined as the ratio between the

reflected and the incident power wave at the port *i* as follows [21]:

$$\Gamma = \frac{b_i}{a_i}.\tag{2.3}$$

The power wave reflection coefficient looking into the port *i* can also be expressed using the impedance of the port  $Z_i$  and the impedance of the termination load  $Z_L$  as follows [21]:

$$\Gamma = \frac{Z_L - Z_i^*}{Z_L + Z_i}.$$

(2.4)

In the general case, the relationship between the incident and reflected power waves, and the S-parameters can be expressed in the form of a matrix equation as follows [25]:

$$[\boldsymbol{b}] = [\boldsymbol{S}][\boldsymbol{a}]. \tag{2.5}$$

For an N-port linear network the S-parameter matrix is expressed as follows [25]:

$$\begin{bmatrix} b_1 \\ b_2 \\ \vdots \\ b_N \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} & \cdots & S_{1N} \\ S_{21} & \ddots & & \vdots \\ \vdots & & \ddots & \vdots \\ S_{N1} & \cdots & \cdots & S_{NN} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \\ \vdots \\ a_N \end{bmatrix}.$$

(2.6)

For a four-port linear network, as shown in Fig. 2.1a, the S-parameter matrix is expressed as follows [27]:

$$\begin{bmatrix} b_1 \\ b_2 \\ b_3 \\ b_4 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} & S_{13} & S_{14} \\ S_{21} & S_{22} & S_{23} & S_{24} \\ S_{31} & S_{32} & S_{33} & S_{34} \\ S_{41} & S_{42} & S_{43} & S_{44} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \\ a_3 \\ a_4 \end{bmatrix}.$$

(2.7)

#### **Mixed-mode S-parameters**

Mixed-mode S-parameters are developed for combined differential-mode and common-mode normalized power waves [20, 25, 26, 28–37]. The two physical single-ended ports that form a logical balanced port can be viewed as a single differential port with a mixed-mode stimulus, as shown in Fig. 2.1b. The stimulus can be either common-mode, where in-phase signals with the same magnitude are applied to the two physical ports, or differential-mode, where counter-phase signals with the same magnitude are applied to the two physical ports. The mixed-mode S-parameters can be calculated from the standard single-ended S-parameters and vice versa [20, 25–27, 29, 30, 34, 35, 38–40].

For the two-port mixed-mode network shown in Fig. 2.1b, differential-mode and common-mode voltages and currents are defined at each port, using the single-ended voltages and currents shown in Fig. 2.1a. The differential-mode voltages and currents at the balanced ports are defined using the difference between the voltages and currents at the two physical ports that form the balanced port. The common-mode voltages and currents at the balanced ports are defined using the sum of the voltages and currents at the two physical ports that form the balanced port. The differential-mode and common-mode voltages and currents are defined as follows [20, 25, 28]:

$$V_{d1} = V_1 - V_2, (2.8)$$

$$I_{d1} = \frac{1}{2} \left( I_1 - I_2 \right), \tag{2.9}$$

$$V_{d2} = V_3 - V_4, (2.10)$$

$$I_{d2} = \frac{1}{2} \left( I_3 - I_4 \right), \tag{2.11}$$

$$V_{c1} = \frac{1}{2} \left( V_1 + V_2 \right), \tag{2.12}$$

$$I_{c1} = I_1 + I_2, (2.13)$$

$$V_{c2} = \frac{1}{2} \left( V_3 + V_4 \right), \tag{2.14}$$

$$I_{c2} = I_3 + I_4. (2.15)$$

Using this concept, differential-mode and common-mode normalized power waves are introduced. They are analogous to the concept of power waves for standard single-ended S-parameters, calculated using (2.1). The differential-mode and common-mode normalized power waves can be expressed using the standard single-ended power waves. Similar to the voltage and currents, the differential-mode power waves are calculated using the difference between the single-ended power waves, while the common-mode power waves are calculated using the sum of the single-ended power waves, as follows [20, 25, 27–29].

$$a_{d1} = \frac{1}{\sqrt{2}}(a_1 - a_2), \tag{2.16}$$

$$a_{c1} = \frac{1}{\sqrt{2}}(a_1 + a_2), \tag{2.17}$$

$$b_{d1} = \frac{1}{\sqrt{2}}(b_1 - b_2), \tag{2.18}$$

$$b_{c1} = \frac{1}{\sqrt{2}}(b_1 + b_2), \qquad (2.19)$$

$$a_{d2} = \frac{1}{\sqrt{2}}(a_3 - a_4), \tag{2.20}$$

$$a_{c2} = \frac{1}{\sqrt{2}}(a_3 + a_4), \tag{2.21}$$

$$b_{d2} = \frac{1}{\sqrt{2}}(b_3 - b_4), \tag{2.22}$$

Multiport measurement methodology and design of attenuator structures

$$b_{c2} = \frac{1}{\sqrt{2}}(b_3 + b_4). \tag{2.23}$$

This relationship between the mixed-mode incident power wave matrix  $[A_{mm}]$  and the standard single-ended incident power wave matrix  $[A_{std}]$  is expressed as follows [20, 25, 29]:

$$\begin{bmatrix} a_{d1} \\ a_{d2} \\ a_{c1} \\ a_{c2} \end{bmatrix} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & -1 \\ 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \\ a_3 \\ a_4 \end{bmatrix} = \begin{bmatrix} \mathbf{M} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \\ a_3 \\ a_4 \end{bmatrix}, \quad (2.24)$$

$$[\boldsymbol{A}_{mm}] = [\boldsymbol{M}] [\boldsymbol{A}_{std}]. \tag{2.25}$$

In a similar way, the relationship between the mixed-mode reflected power wave matrix  $[\mathbf{B}_{mm}]$  and the standard single-ended reflected power wave matrix  $[\mathbf{B}_{std}]$  is expressed as follows [20, 25, 29]:

$$\begin{bmatrix} b_{d1} \\ b_{d2} \\ b_{c1} \\ b_{c2} \end{bmatrix} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & -1 \\ 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 \end{bmatrix} \begin{bmatrix} b_1 \\ b_2 \\ b_3 \\ b_4 \end{bmatrix} = [\boldsymbol{M}] \begin{bmatrix} b_1 \\ b_2 \\ b_3 \\ b_4 \end{bmatrix}, \qquad (2.26)$$

$$[\boldsymbol{B}_{mm}] = [\boldsymbol{M}] [\boldsymbol{B}_{std}], \qquad (2.27)$$

where the transformation matrix [M] is defined as follows [20, 25, 29]:

$$[\mathbf{M}] = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & -1 \\ 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 \end{bmatrix}.$$

(2.28)

Mixed-mode S-parameters are defined using the differential-mode and common-mode normalized power waves as follows [20, 25, 27–29]:

$$\begin{bmatrix} b_{d1} \\ b_{d2} \\ b_{c1} \\ b_{c2} \end{bmatrix} = \begin{bmatrix} S_{dd11} & S_{dd12} & S_{dc11} & S_{dc12} \\ S_{dd21} & S_{dd22} & S_{dc21} & S_{dc22} \\ S_{cd11} & S_{cd12} & S_{cc11} & S_{cc12} \\ S_{cd21} & S_{cd22} & S_{cc21} & S_{cc22} \end{bmatrix} \begin{bmatrix} a_{d1} \\ a_{d2} \\ a_{c1} \\ a_{c2} \end{bmatrix}.$$

(2.29)

Using (2.25) and (2.27), the relationship between the mixed-mode S-parameter matrix  $[S_{mm}]$  and the standard single-ended S-parameter matrix  $[S_{std}]$  is expressed as follows [20, 25, 29]:

$$[\boldsymbol{S}_{mm}] = [\boldsymbol{M}] [\boldsymbol{S}_{std}] [\boldsymbol{M}]^{-1}.$$

(2.30)

#### **Converting single-ended to mixed-mode S-parameters**

Mixed-mode S-parameters can be calculated from the measured single-ended S-parameters. A linear network with four physical ports is shown in Fig. 2.1. The network can be represented as a mixed-mode network with two balanced logical ports. Two physical single-ended ports  $P_1$  and  $P_2$  form the logical balanced port (P1), while the other two physical single-ended ports  $P_3$  and  $P_4$  form the logical balanced port (P2), for the mixed-mode S-parameter analysis. The mixed-mode S-parameters are calculated from the measured standard single-ended S-parameters as follows [27, 41]:

$$S_{dd11} = \frac{1}{2} \left( S_{11} - S_{21} - S_{12} + S_{22} \right), \qquad (2.31)$$

$$S_{dd12} = \frac{1}{2} \left( S_{13} - S_{23} - S_{14} + S_{24} \right), \qquad (2.32)$$

$$S_{dd21} = \frac{1}{2} \left( S_{31} - S_{41} - S_{32} + S_{42} \right), \tag{2.33}$$

$$S_{dd22} = \frac{1}{2} \left( S_{33} - S_{43} - S_{34} + S_{44} \right), \qquad (2.34)$$

$$S_{cd11} = \frac{1}{2} \left( S_{11} + S_{21} - S_{12} - S_{22} \right), \qquad (2.35)$$

$$S_{cd12} = \frac{1}{2} \left( S_{13} + S_{23} - S_{14} - S_{24} \right), \qquad (2.36)$$

$$S_{cd21} = \frac{1}{2} \left( S_{31} + S_{41} - S_{32} - S_{42} \right), \qquad (2.37)$$

$$S_{cd22} = \frac{1}{2} \left( S_{33} + S_{43} - S_{34} - S_{44} \right), \qquad (2.38)$$

$$S_{dc11} = \frac{1}{2} \left( S_{11} - S_{21} + S_{12} - S_{22} \right), \qquad (2.39)$$

$$S_{dc12} = \frac{1}{2} \left( S_{13} - S_{23} + S_{14} - S_{24} \right), \qquad (2.40)$$

$$S_{dc21} = \frac{1}{2} \left( S_{31} - S_{41} + S_{32} - S_{42} \right), \tag{2.41}$$

$$S_{dc22} = \frac{1}{2} \left( S_{33} - S_{43} + S_{34} - S_{44} \right), \qquad (2.42)$$

$$S_{cc11} = \frac{1}{2} \left( S_{11} + S_{21} + S_{12} + S_{22} \right), \qquad (2.43)$$

$$S_{cc12} = \frac{1}{2} \left( S_{13} + S_{23} + S_{14} + S_{24} \right), \qquad (2.44)$$

$$S_{cc21} = \frac{1}{2} \left( S_{31} + S_{41} + S_{32} + S_{42} \right), \qquad (2.45)$$

$$S_{cc22} = \frac{1}{2} \left( S_{33} + S_{43} + S_{34} + S_{44} \right).$$

(2.46)

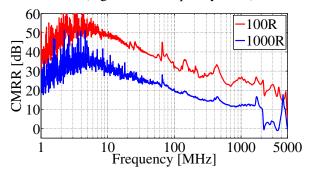

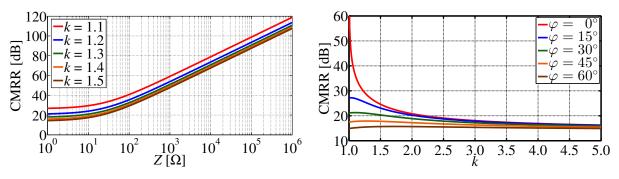

A key parameter for characterizing the performance of differential circuits is the common-mode rejection ratio. The CMRR is defined as the ratio between the wanted differential-mode signal transmission and the unwanted common-mode signal transmission. In this thesis the CMRR of four-port circuits with a balanced input and a balanced output, shown in Fig. 2.1, is defined as the ratio between the differential-to-differential transmission coefficient  $S_{dd21}$  and the common-to-differential mode conversion transmission coefficient  $S_{dc21}$ , given that a differential load is always connected to the output of such circuits. Alternative definitions of the CMRR for four-port networks are sometimes used, depending on the application, as described in [38, 42]. The CMRR is calculated as follows:

$$CMRR = \frac{S_{dd21}}{S_{dc21}}.$$

(2.47)

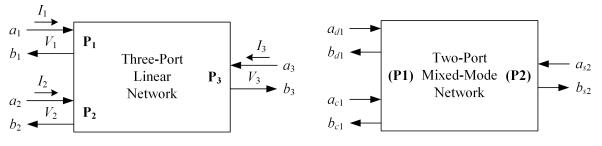

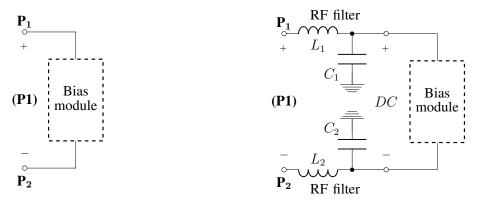

A linear network with three physical ports is shown in Fig. 2.2a. The network can be represented as a mixed-mode network with one balanced logical port and one single-ended logical port, as shown in Fig. 2.2b. The two physical single-ended ports  $P_1$  and  $P_2$  form the logical balanced port (P1). The physical single-ended port  $P_3$  forms the logical single-ended port (P2), for the mixed-mode S-parameter analysis. The mixed-mode S-parameters of this three-port network are expressed as follows [27, 36, 41]:

$$\begin{bmatrix} b_{d1} \\ b_{s2} \\ b_{c1} \end{bmatrix} = \begin{bmatrix} S_{dd11} & S_{ds12} & S_{dc11} \\ S_{sd21} & S_{ss22} & S_{sc21} \\ S_{cd11} & S_{cs12} & S_{cc11} \end{bmatrix} \begin{bmatrix} a_{d1} \\ a_{s2} \\ a_{c1} \end{bmatrix}.$$

(2.48)

(a) Three-port single-ended network.

(b) Two-port mixed-mode network.

**Figure 2.2:** Linear network with three physical ports represented in a single-ended configuration (left) and in a mixed-mode configuration with two logical ports (right).

The mixed-mode S-parameters of the three-port network are calculated from the measured standard single-ended S-parameters as follows [27, 41]:

$$S_{ss22} = S_{33}, (2.49)$$

$$S_{sd21} = \frac{1}{\sqrt{2}} \left( S_{31} - S_{32} \right), \tag{2.50}$$

$$S_{sc21} = \frac{1}{\sqrt{2}} \left( S_{31} + S_{32} \right), \tag{2.51}$$

$$S_{ds12} = \frac{1}{\sqrt{2}} \left( S_{13} - S_{23} \right), \tag{2.52}$$

$$S_{cs12} = \frac{1}{\sqrt{2}} \left( S_{13} + S_{23} \right), \tag{2.53}$$

$$S_{dd11} = \frac{1}{2} \left( S_{11} - S_{12} - S_{21} + S_{22} \right), \qquad (2.54)$$

$$S_{dc11} = \frac{1}{2} \left( S_{11} + S_{12} - S_{21} - S_{22} \right), \qquad (2.55)$$

$$S_{cd11} = \frac{1}{2} \left( S_{11} - S_{12} + S_{21} - S_{22} \right), \qquad (2.56)$$

$$S_{cc11} = \frac{1}{2} \left( S_{11} + S_{12} + S_{21} + S_{22} \right).$$

(2.57)

The common-mode rejection ratio of three-port circuits with a balanced input and a single-ended output, as shown in Fig. 2.2, is defined as the ratio between the wanted differential-mode signal transmission coefficient  $S_{sd21}$  and the unwanted common-mode signal transmission coefficient  $S_{sc21}$ . The CMRR is calculated as follows [42]:

$$CMRR = \frac{S_{sd21}}{S_{sc21}}.$$

(2.58)

#### 2.1.2 S-parameter measurements

#### Traditional vector network analyzer

A device for measuring S-parameters is called a vector network analyzer (VNA) [43, 44]. A VNA can measure both the magnitude and phase of S-parameters. A VNA needs to be calibrated before performing measurements, by measuring a set of well-defined calibration standards [45–49]. A traditional VNA performs measurements by stimulating each port individually, while the remaining ports are terminated with a matched load [29]. The reflected and transmitted traveling waves are measured in order to calculate the standard single-ended S-parameters. Vector network analyzers with two or four physical ports are most commonly used. Due to the higher price of four-port vector network analyzers, more affordable two-port vector network analyzers are often used. When a two-port VNA is used to measure a multiport circuit, more than one measurement needs to be performed. The measurement is performed as a series of two-port measurements [30, 50]. The remaining ports are terminated with a matched load, as shown in Fig 2.3.

For example, in order to measure a four-port circuit with physical ports  $P_1-P_4$ , as shown in Fig. 2.1a, a four-by-four S-parameter matrix (2.7) is generated, containing 16 elements. When a measurement of a four-port circuit is performed using a two-port VNA, six two-port measurements need to be performed, each for a combination of two ports:  $P_1$  and  $P_2$ ,  $P_1$  and  $P_3$ ,  $P_1$

Figure 2.3: Two-port measurement of a four-port linear network.

and  $P_4$ ,  $P_2$  and  $P_3$ ,  $P_2$  and  $P_4$ ,  $P_3$  and  $P_4$ . Six two-by-two S-parameter matrices are generated. These matrices need to be combined to form a four-by-four S-parameter matrix of the measured circuit. The downside of using a two-port VNA compared to a four-port VNA is a more complicated and prolonged measurement procedure, where a series of measurements needs to be performed, instead of a single measurement. Given that the ports of the VNA are disconnected and reconnected to the device under test multiple times, this has a negative effect on the measurement accuracy and repeatability.

When performing two-port measurements of a four-port device, the return loss  $S_{ii}$  at each port *i* is measured three times. In an ideal case, all three measurement results would be the same, however that is usually not the case in practice. When combining the results, one option is to take only one of the measurements into account. An alternative approach is to reduce these inconsistencies by making an average of the three measurements, and use that result in the combined matrix [50]. For example, the return loss at port P<sub>1</sub> is calculated as the average of measurements performed at ports P<sub>1</sub> and P<sub>2</sub>, P<sub>1</sub> and P<sub>3</sub>, and P<sub>1</sub> and P<sub>4</sub> as follows:

$$S_{11,avg} = \frac{S_{11,M12} + S_{11,M13} + S_{11,M14}}{3}.$$

(2.59)

For symmetrical devices, an average of the return loss values on all ports can be calculated [50].

Another thing to note when combining the measurement results is the impedance of the loads used to terminate the unused ports during the two-port measurements. These ports should be terminated with a matched load. However, in practice the loads are not ideal and there is some mismatch between the characteristic impedance and the load impedance. An approach for renormalizing the scattering parameter matrix is described in [50, 51]. Aside from normalizing non-ideal terminations, this procedure can also be used in cases where highly reflective terminations are used, in order to raise the value of the reflected signals above the noise level [51].

#### Pure-mode vector network analyzer

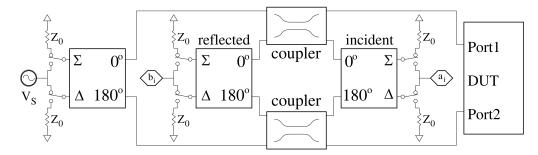

In order to thoroughly characterize differential (balanced) circuits, the differential-mode, common-mode and mode conversion responses need to be measured. These responses are represented using mixed-mode S-parameters [28]. While a traditional VNA performs measurements of single-ended S-parameters directly, a concept called the pure-mode vector network analyzer (PMVNA) measures mixed-mode S-parameters directly [29, 39, 52–55]. This is achieved by stimulating each mode individually, instead of stimulating each physical port individually, which is the case with a traditional VNA [29]. The schematic of the PMVNA concept is shown in Fig. 2.4. The calibration procedure for a PMVNA is described in [53].

Figure 2.4: Pure-mode vector network analyzer concept schematic, image sourced from [55].

Measurements of a differential circuit using a PMVNA display a significantly lower level of uncertainty, compared to a traditional VNA. This is particularly notable for mode conversion mixed-mode S-parameters,  $S_{cd}$  and  $S_{dc}$  [39, 56, 57]. A full implementation of the PMVNA concept is not yet commercially available [55]. However, there are commercially available dual-source VNAs that can produce either pure-differential-mode or pure-common-mode drive in both the forward and reverse direction [54, 58]. These network analyzers can be used to measure balanced devices more accurately.

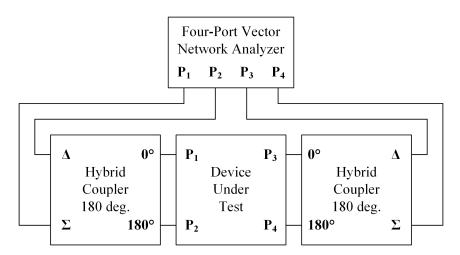

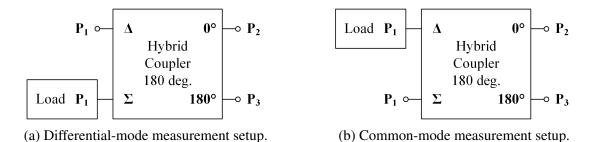

#### Hybrid couplers

In order to characterize a differential circuit using a traditional single-ended vector network analyzer, external hybrid couplers, power dividers or baluns can be used [29, 31, 41, 52, 59–63]. A hybrid coupler has two input and two output ports. A hybrid coupler with a 180 degree phase shift can generate either in-phase signals or counter-phase signals at the two output ports, from a single input port. Alternatively, the hybrid can be used to either make a sum or a difference of the two input signals, at the output port [15]. When a hybrid coupler with a 180 degree phase shift is used with a traditional single-ended four-port VNA, the system can generate both differential-mode and common-mode stimulus [59]. Both input ports of the hybrid coupler can be used simultaneously to generate both a differential-mode and a common-mode signal component at the output ports, as shown in Fig. 2.5. With known S-parameters of the hybrid coupler, the impact of the coupler can be de-embedded from the measurement results [49].

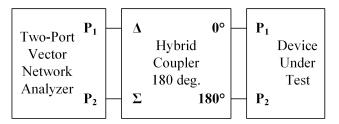

The same procedure can be used with a two-port VNA, if a two-port differential device is measured [61, 63], as shown in Fig. 2.6. If a four-port differential device is measured, two sets of measurements need to be performed, one with a differential-mode stimulus, and the second

**Figure 2.5:** Mixed-mode S-parameter measurement setup using a four-port vector network analyzer and two hybrid couplers with a 180 degree phase shift.

with a common-mode stimulus, generated from a single input port of the hybrid coupler. The other input port of the hybrid coupler is terminated with a matched load. In a similar way, the differential-mode and common-mode response of the characterized device need to be measured separately, using a second hybrid coupler.

**Figure 2.6:** Mixed-mode S-parameter measurement setup using a two-port vector network analyzer and a hybrid coupler with a 180 degree phase shift.

Instead of using a hybrid coupler, baluns and power dividers can be used [31, 41, 60–62]. A balun can be used to generate a differential-mode stimulus, while a power divider can be used to generate a common-mode stimulus. Using these circuits, two sets of measurements can be performed. For some applications, it is only necessary to measure either the differential-mode or the common-mode response of the differential device under test, in which case only one of the aforementioned circuits is used. In some cases, baluns and power dividers can be a part of measurement probes, which means that their S-parameters cannot be measured separately [31]. In such cases, other calibration approaches are used [41].

Hybrid couplers, baluns and power dividers that are used in practice are not ideal. Instead of generating perfect differential-mode and common-mode signals, there is a certain amplitude and phase imbalance between the two signals. This means that in a differential-mode measurement, aside from the differential-mode signal, an unwanted common-mode signal is generated, and vice versa. This unwanted amplitude and phase imbalance of the generated signals affects the

measurement accuracy and introduces measurement uncertainty [64, 65]. Additional components used in the measurements setup, like cables and adapters, introduce further amplitude and phase imbalance. The same problem also occurs in pure-mode vector network analyzers [54].

#### 2.1.3 Measurement methodology verification

The S-parameter measurement methods using different vector analyzer concepts that have been described Section 2.1.2 are compared on three practical examples. The goal is to verify the results of the different measurement methods for the devices characterized within the scope of this thesis. The three devices that are characterized are a four-port attenuator circuit, a three-port laser diode and a hybrid coupler with a 180 degree phase shift.

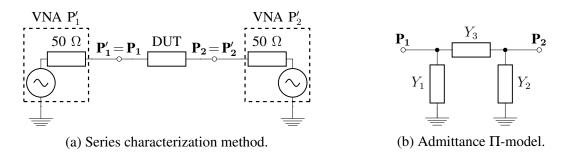

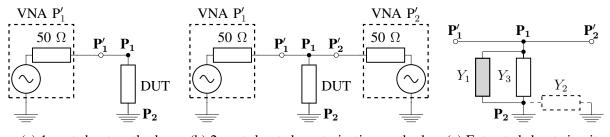

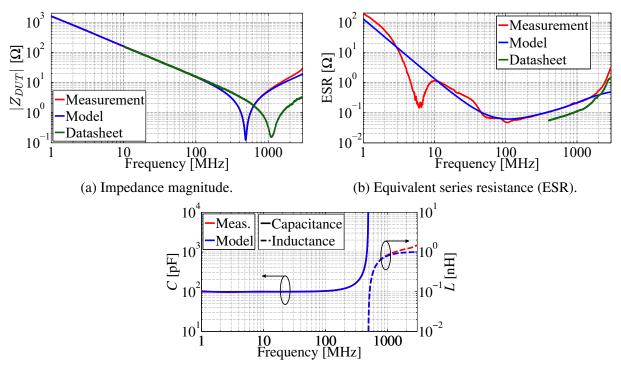

#### **Attenuator circuit**

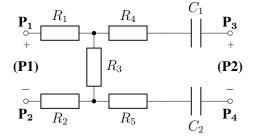

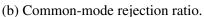

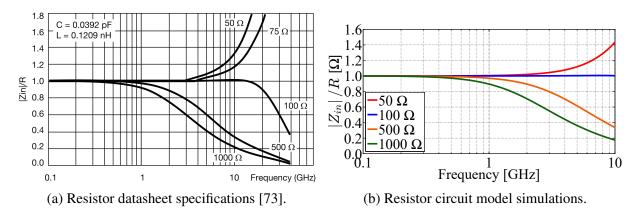

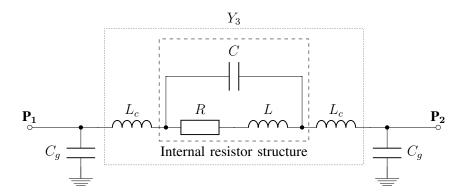

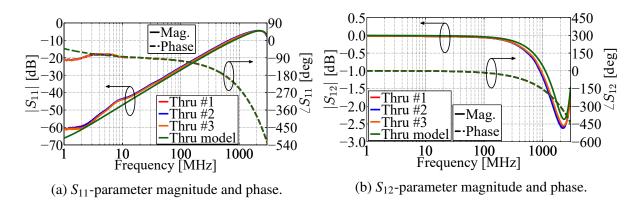

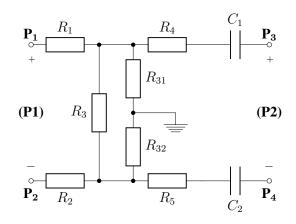

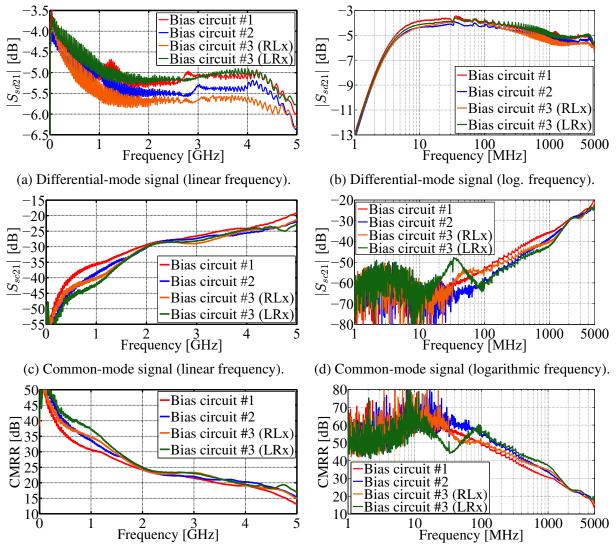

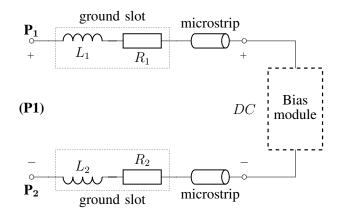

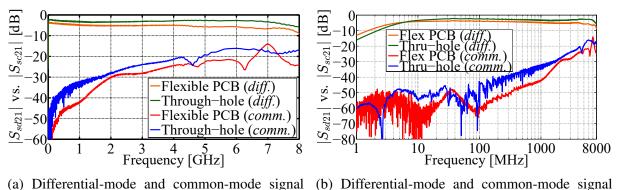

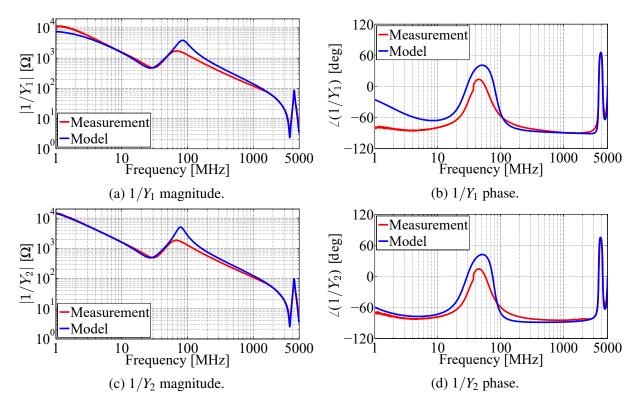

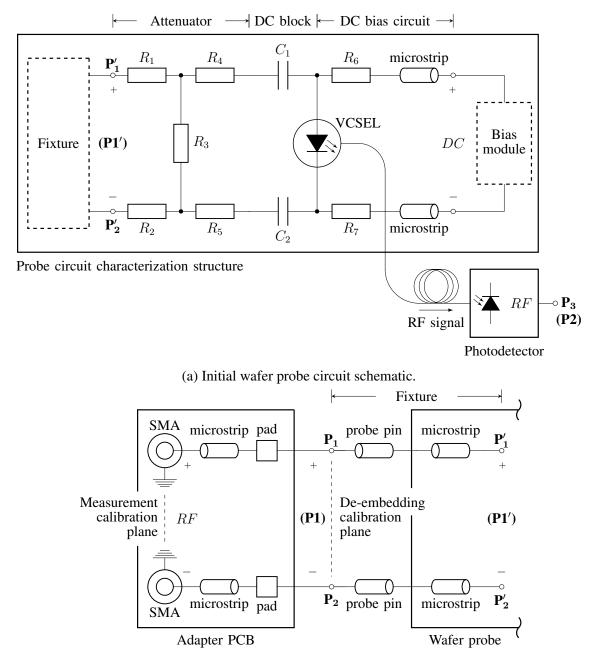

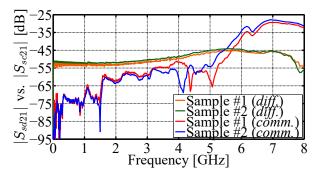

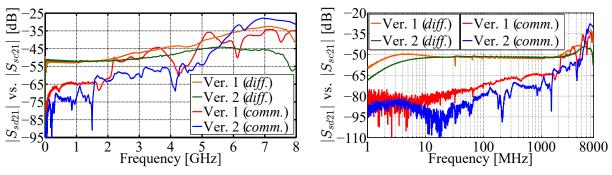

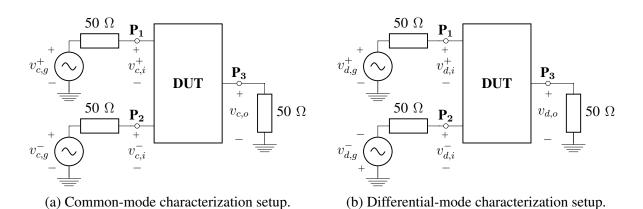

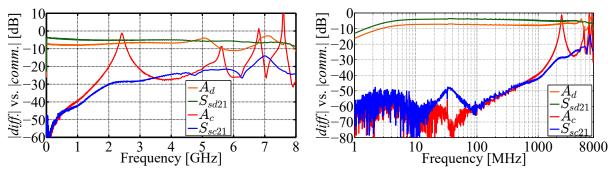

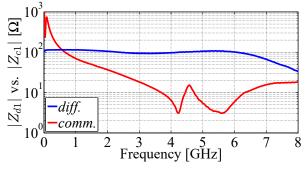

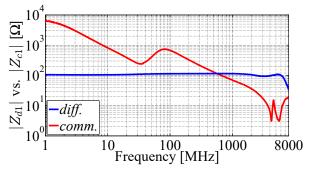

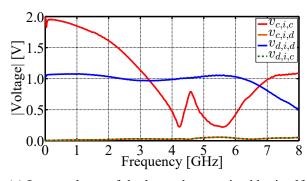

The schematic of the characterized four-port differential attenuator circuit is shown in Fig. 2.7. The device has four physical ports which form two mixed-mode logical ports, as shown in Fig. 2.1. The attenuator circuit is characterized using three different measurement methods. The first measurement is performed using a traditional four-port vector network analyzer [66]. Based on the measured single-ended S-parameters, mixed-mode S-parameters are calculated using (2.31)–(2.46). The second measurement is performed using a dual-source four-port vector network analyzer [67]. This concept for measuring mixed-mode S-parameters using a dual-source four-port VNA is called the true differential measurement mode (TDMM) [58]. Mixed-mode S-parameters are measured directly. The third measurement is performed using a traditional two-port vector network analyzer [68]. A set of six two-port measurements is performed, each for a combination of two physical ports. The measurement results are combined into a four-by-four S-parameter matrix using the technique described in [30, 50]. The mixed-mode S-parameters are calculated in the same way as for the measurement using the traditional four-port VNA.

Figure 2.7: Four-port differential attenuator circuit schematic.

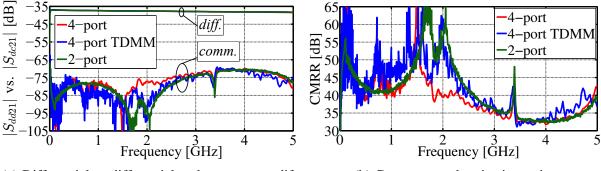

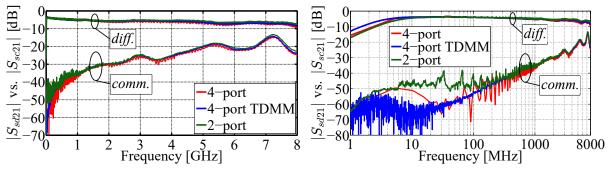

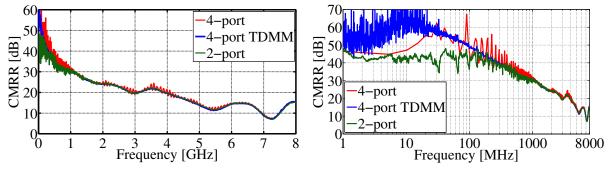

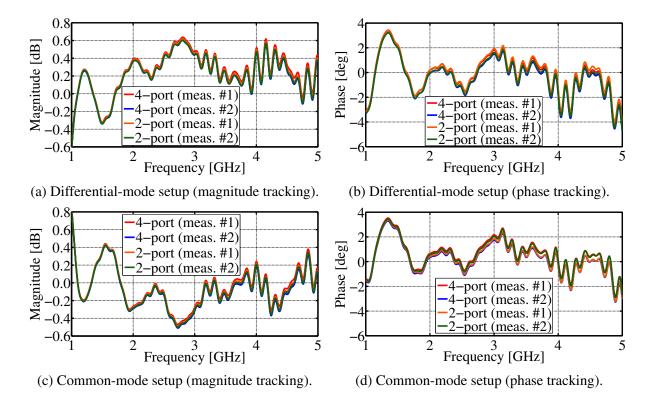

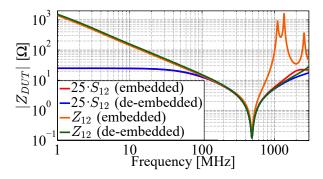

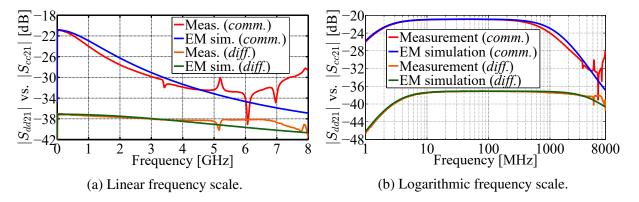

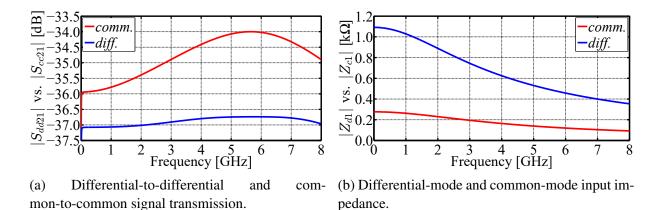

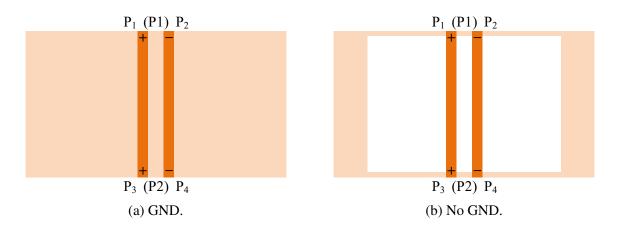

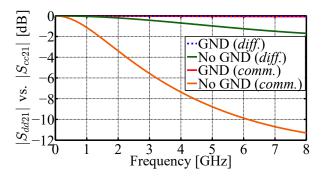

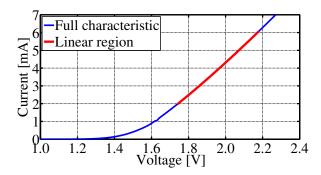

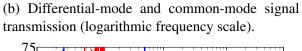

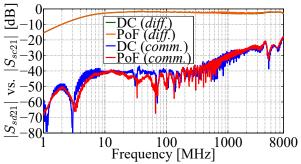

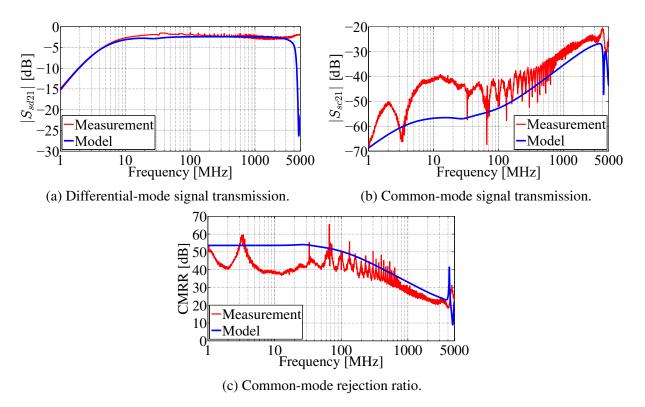

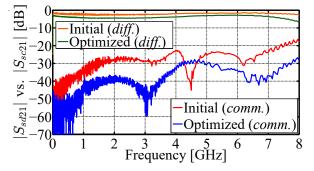

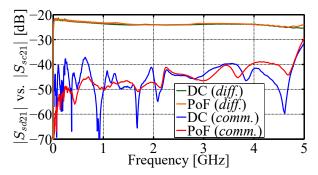

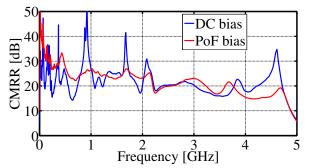

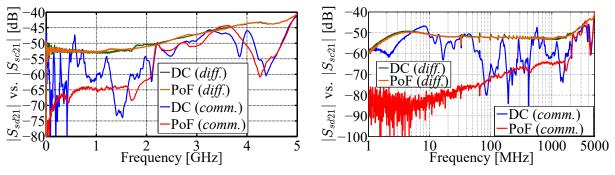

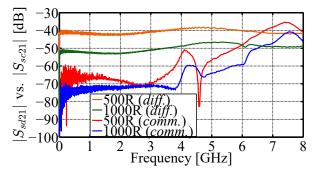

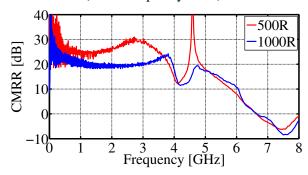

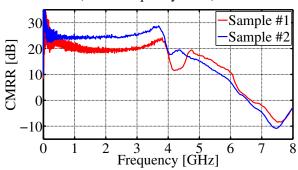

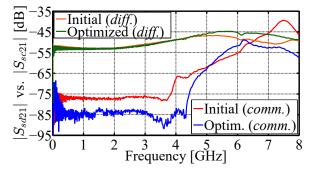

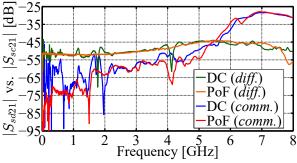

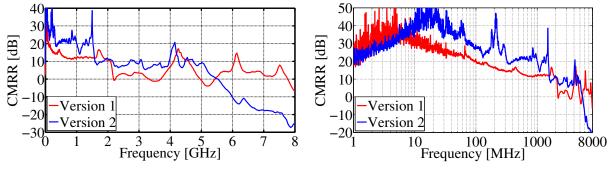

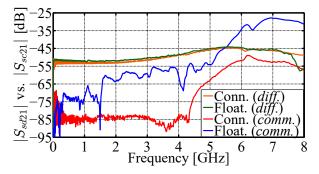

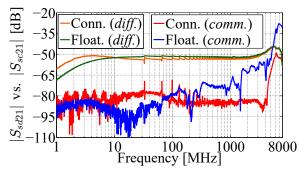

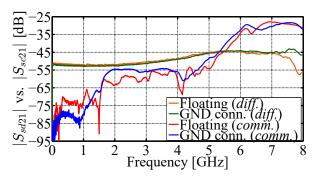

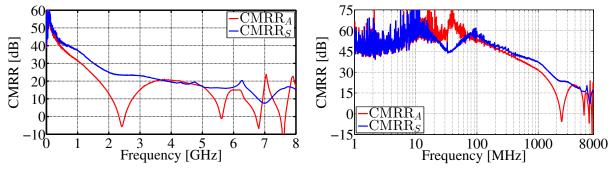

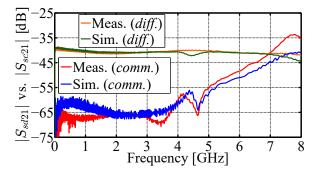

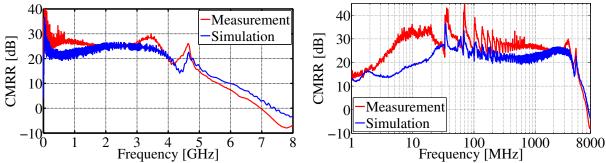

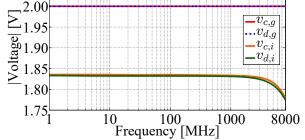

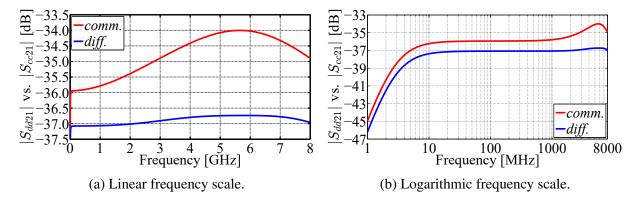

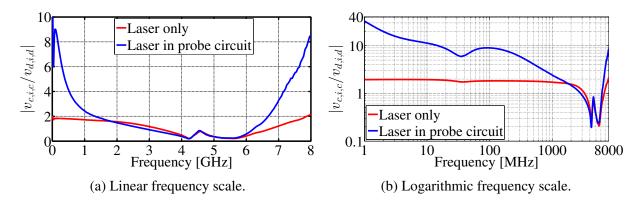

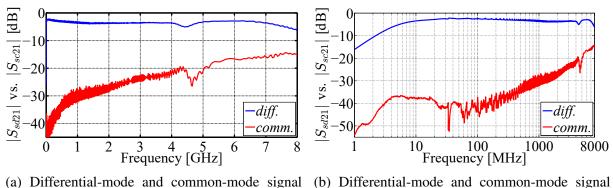

The comparison of the measurement results is shown in Fig. 2.8. Two characteristic mixedmode S-parameters are compared. The first value is the differential-to-differential transmission coefficient  $S_{dd21}$ , which determines the attenuation level of the attenuator. The second value is the common-to-differential transmission coefficient  $S_{dc21}$ , which quantifies the unwanted mode conversion from the common-mode signal at the input to a differential-mode signal at the output. The measurement results for the differential-to-differential signal transmission  $S_{dd21}$  show very good repeatability. No significant difference can be observed between the three measurement methods. The general trend of the common-to-differential mode conversion  $S_{dc21}$  measurements is similar using all three methods. Some differences are observed between the measurements in terms on noise in the characteristic, as well as the resonances. This is expected, given the low level of the measured signal, which is close to the noise floor of the measurement system, making it more susceptible to measurement uncertainty, as explained in Section 2.1.2.

(a) Differential-to-differential and common-to-differential signal transmission.

**Figure 2.8:** Characteristics of the attenuator circuit measured using a traditional four-port VNA, a dual-source four-port VNA using the TDMM, and a traditional two-port VNA. The magnitude of the differential-to-differential transmission coefficient  $S_{dd21}$ , the common-to-differential transmission coefficient  $S_{dc21}$ , and the common-mode rejection ratio (CMRR) are compared.

The general trend of the common-mode rejection ratio is similar using all three measurement methods. Given that the CMRR is defined as the ratio between the two transmission coefficients using (2.47), the impact of the common-to-differential mode conversion has a dominant effect on the CMRR characteristic. At frequencies where the CMRR value is lower, the fitting between the measurement methods is very good. At frequencies where the CMRR value is above 45 dB, there is more discrepancy between the characteristics, because precise CMRR measurements require very low magnitude and phase uncertainty of the measurement system. The magnitude and phase uncertainty are dependent on the VNA model used to perform the measurements, the output power, frequency range, calibration method and the measurement setup [66–68].

#### Laser diode

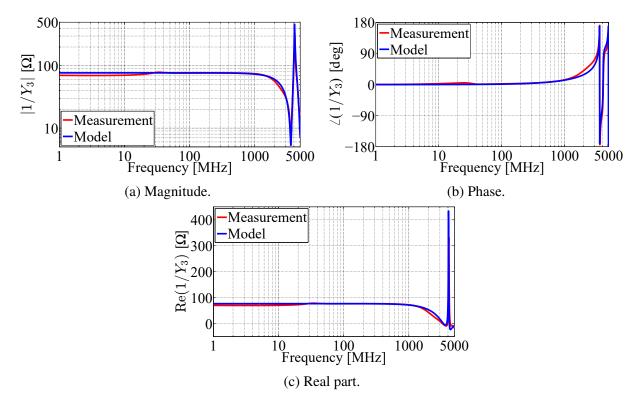

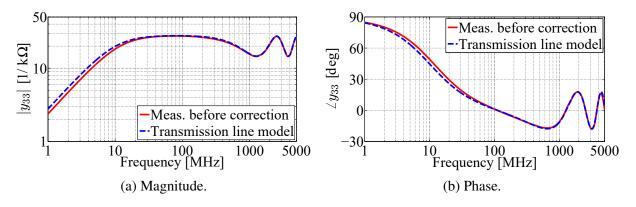

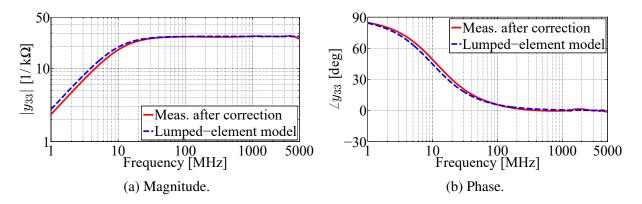

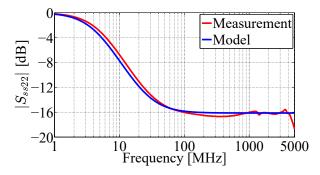

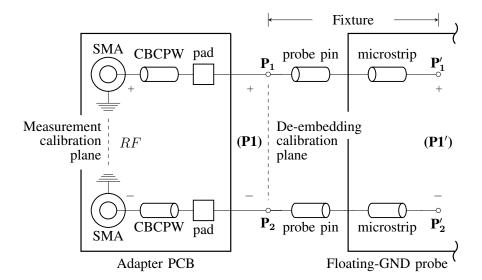

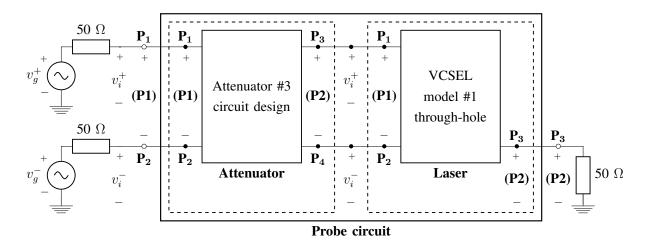

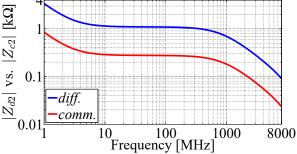

A sample laser diode is characterized using the same three methods used to characterize the attenuator circuit. A schematic of the laser measurement setup is shown in Fig. 2.9. The physical port  $P_1$  is connected to the laser anode, the physical port  $P_2$  is connected to the laser cathode, and the physical port  $P_3$  is connected to the output of the photodetector. The physical ports  $P_1$  and  $P_2$  form the logical balanced port (P1), and the physical port  $P_3$  forms the logical single-ended port (P2), as shown in Fig. 2.2. Using a traditional four-port vector network analyzer [66], three-port single-ended S-parameters are measured, and the mixed-mode S-parameters are calculated using (2.49)–(2.57). The dual-source four-port VNA [67] is used to measure the mixed-mode S-parameters directly. Using a traditional two-port vector network analyzer [68], a set of three two-port measurements is performed, each for a combination of two physical ports. The measurement results are combined into a three-by-three S-parameter matrix using the technique described in [30, 50]. The mixed-mode S-parameters are calculated in the same way as for the measurement using the traditional four-port VNA.

Figure 2.9: Three-port laser diode measurement setup schematic.

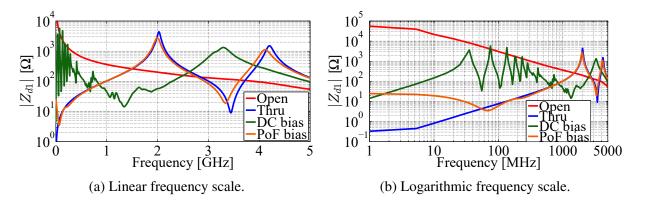

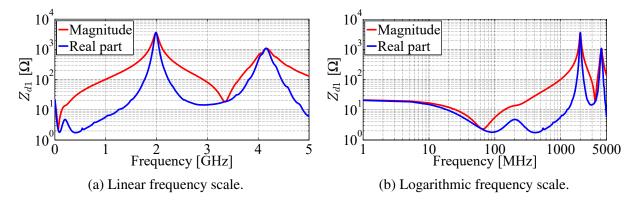

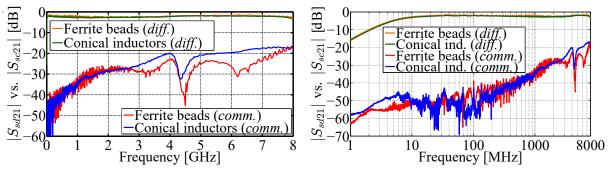

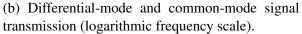

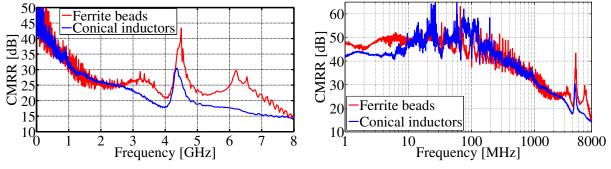

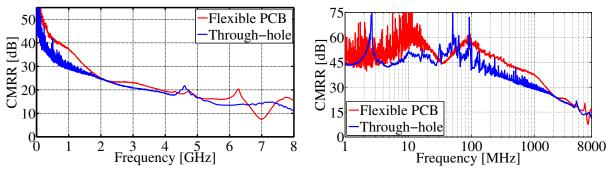

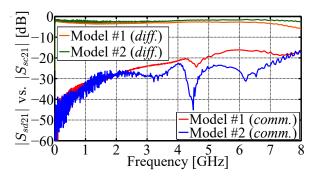

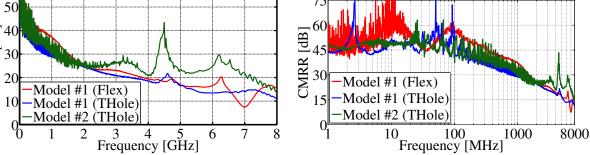

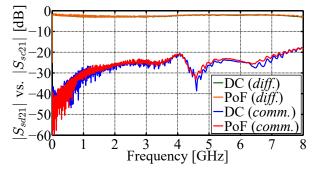

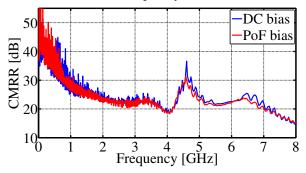

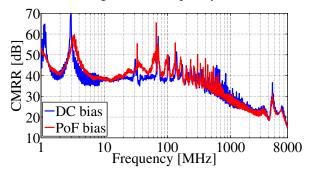

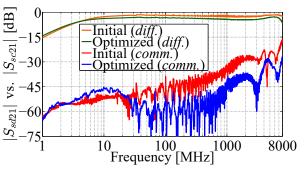

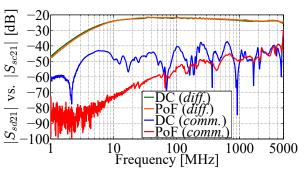

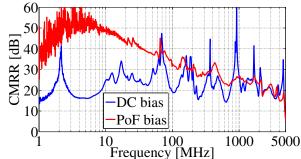

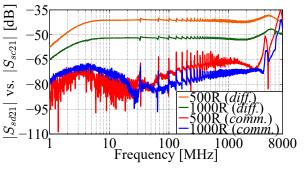

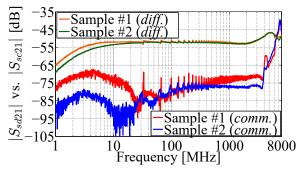

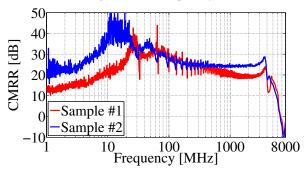

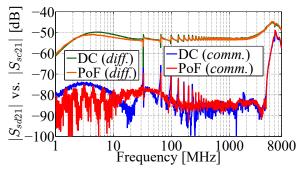

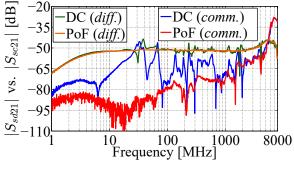

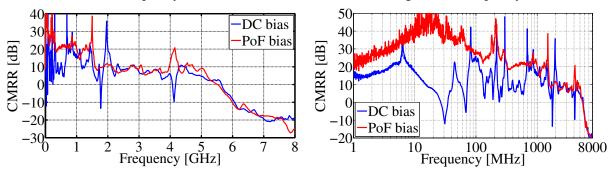

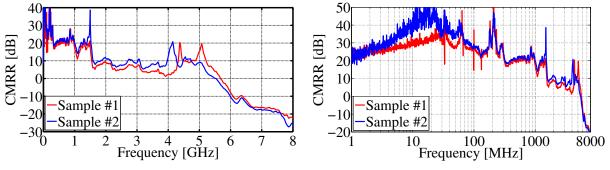

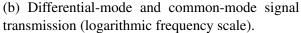

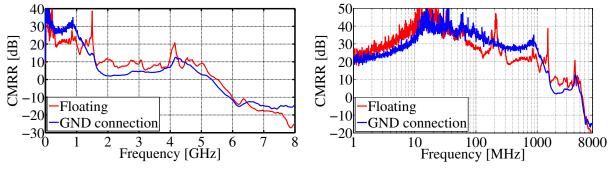

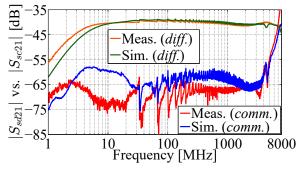

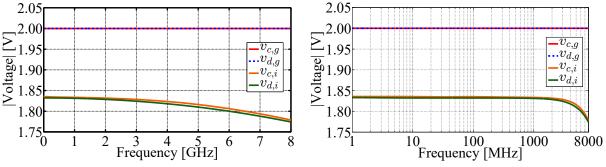

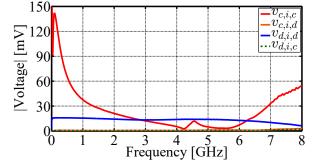

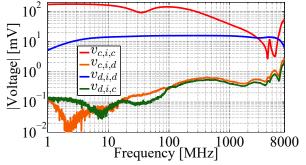

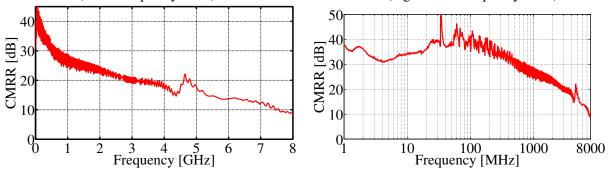

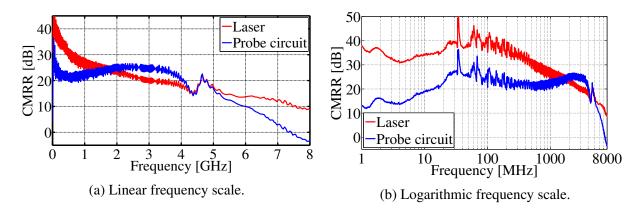

The mixed-mode S-parameter measurement results are compared in Fig. 2.10. There is very good repeatability between the three measurement methods for the differential-mode transmission coefficient  $S_{sd21}$ . Only the four-port TDMM measurement shows a slightly lower lower cutoff frequency. The measurement repeatability is also very good for the common-mode transmission coefficient  $S_{sc21}$  at higher frequencies. There are more significant differences between the measurement methods for frequencies below 100 MHz. Due to the sensitive nature of the laser characterization setup there is always some difference between the measurements, because the common-mode signal is very sensitive to the twisting and bending of the cables in the measurement setup. Additionally, the low level of the common-mode signal makes it difficult to measure accurately, particularly at low frequencies where the measurement accuracy of the VNA is the worst [66–68]. By comparing the CMRR results it is observed that all three measurement methods show very good repeatability for frequencies above 1 GHz. At frequencies below 100 MHz the differences are more pronounced, because such high CMRR values are very difficult to measure, as they require the measurement system to have extremely low magnitude and phase measurement uncertainty. The magnitude and phase uncertainty are typically the worst at low frequencies, close the the minimum frequency of the VNA [66-68]. This is also the frequency range where the CMRR is typically the highest.

As for the attenuator circuit, it is demonstrated that measuring the low level common-mode signal, and in turn the high CMRR, is very difficult. The CMRR can be measured accurately and with good repeatability for lower CMRR values. In general, that is the most important

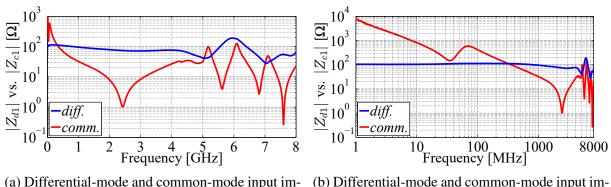

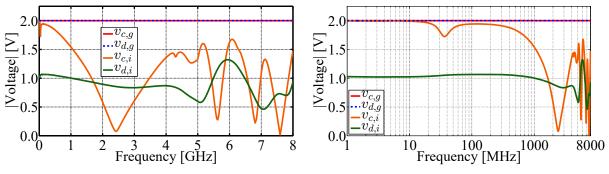

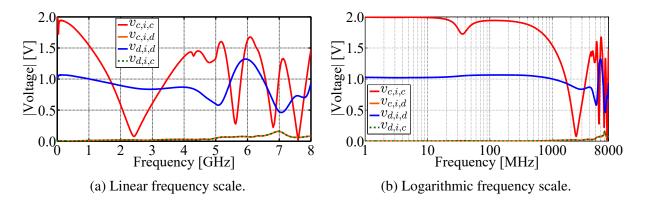

transmission (linear frequency scale).

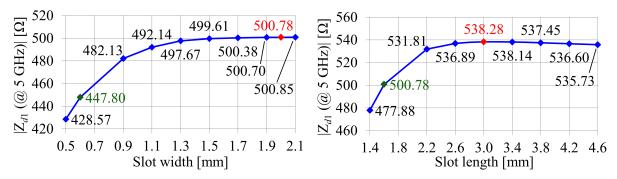

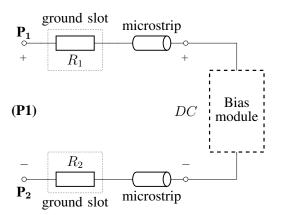

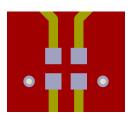

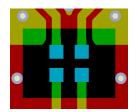

(a) Differential-mode and common-mode signal (b) Differential-mode and common-mode signal transmission (logarithmic frequency scale).