### Power management integrated circuit featuring highefficiency analog techniques

Emanović, Edi

### Doctoral thesis / Disertacija

2024

Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Zagreb, Faculty of Electrical Engineering and Computing / Sveučilište u Zagrebu, Fakultet elektrotehnike i računarstva

Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:168:527445

Rights / Prava: In copyright/Zaštićeno autorskim pravom.

Download date / Datum preuzimanja: 2025-03-19

Repository / Repozitorij:

FER Repository - University of Zagreb Faculty of Electrical Engineering and Computing repozitory

### University of Zagreb FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Edi Emanović

# POWER MANAGEMENT INTEGRATED CIRCUIT FEATURING HIGH-EFFICIENCY ANALOG TECHNIQUES

DOCTORAL THESIS

Zagreb, 2024.

### University of Zagreb

FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Edi Emanović

# POWER MANAGEMENT INTEGRATED CIRCUIT FEATURING HIGH-EFFICIENCY ANALOG TECHNIQUES

DOCTORAL THESIS

Supervisor: Professor Dražen Jurišić, Ph.D.

Zagreb, 2024.

### Sveučilište u Zagrebu FAKULTET ELEKTROTEHNIKE I RAČUNARSTVA

Edi Emanović

# INTEGRIRANI SKLOP ZA UPRAVLJANJE NAPAJANJEM ZASNOVAN NA ANALOGNIM POSTUPCIMA VISOKE UČINKOVITOSTI

DOKTORSKI RAD

Mentor: prof. dr. sc. Dražen Jurišić

Zagreb, 2024.

This doctoral thesis has been done at the University of Zagreb, Faculty of Electrical Engineering and Computing, Department of Electronic Systems and Information Processing.

Part of the research was conducted at the Bar-Ilan University in Israel, Faculty of Engineering, ENICS laboratory.

Supervisor: Professor Dražen Jurišić, Ph.D.

The doctoral thesis has 95 pages.

Doctoral thesis number:

### About the supervisor

**Dražen Jurišić** received the B.Sc., M.Sc., and Ph.D. degrees in electrical engineering from the University of Zagreb, Croatia, in 1990, 1995, and 2002, respectively. From 1997 to 1999, he was with the Institute of Signal and Information Processing, Swiss Federal Institute of Technology (ETH), Zürich, Switzerland. Since 2008, he has been visiting the Faculty of Engineering at Barllan University, Israel, and doing research in the field of analog circuits and filters. He is currently a full professor at the Faculty of Electrical Engineering and Computing (FER), University of Zagreb. He lectures in the field of electrical circuits, signals and systems, and analog and mixed-signal processing circuitry. His research interests include analog and digital signal processing and filter designs, integrated circuit designs, and the study and analysis of fractional-order systems. He has been an MC Member of the COST Action CA15225 "Fractional-Order Systems: Analysis, Synthesis and Their Importance for Future Design." He is a member of the Croatian Society for Communications, Computing, Electronics, Measurement and Control and the IEEE-CAS Society. He was awarded the Silver Plaque Josip Loncar for a distinguished Ph.D. thesis and an IEEE Best Paper Finalist Award for a conference paper.

# O mentoru

**Dražen Jurišić** diplomirao je 1990., magistrirao 1995., te doktorirao 2002. godine na Sveučilištu u Zagrebu, Fakultet elektrotehnike i računarstva. Od 1997. do 1999. radio je na Institutu za obradu signala i informacija, Švicarskog saveznog instituta za tehnologiju (ETH), Zürich, Švicarska. Od 2008. godine boravi na Tehničkom fakultetu Sveučilišta Bar-Ilan u Izraelu i bavi se istraživanjem u području analognih sklopova i filtara. Trenutno je redoviti profesor na Fakultetu elektrotehnike i računarstva (FER) Sveučilišta u Zagrebu. Predaje iz područja električnih krugova, signala i sustava, te analognih i mješovitih sklopova za obradu signala. Njegovi istraživački interesi uključuju analognu i digitalnu obradu signala, dizajn filtara, dizajn integriranih sklopova te proučavanje i analizu sustava frakcijskog reda. Bio je član MC-a COST Action CA15225 "Fractional-Order Systems: Analysis, Synthesis and Their Importance for Future Design". Član je Hrvatskog društva za komunikacije, računarstvo, elektroniku, mjerenje i upravljanje i IEEE-CAS društva. Dobitnik je Srebrne plakete Josip Lončar za istaknutu doktorsku disertaciju, te nagrade IEEE Best Paper Finalist Award za konferencijski rad.

# Acknowledgments

Firstly, I would like to express my deepest gratitude to my supervisor, Professor Dražen Jurišić, whose unwavering support and guidance have been essential throughout my PhD journey. Dražen was always there for me, offering valuable insights, constructive feedback, and encouragement, even during the most challenging moments. His expertise, patience, and dedication to my personal and professional growth have been truly inspiring. I am deeply thankful for his mentorship and for believing in me every step of the way.

I would like to sincerely thank Professor Joseph Shor from Bar-Ilan University in Israel for his invaluable support in analog CMOS design. His expertise and guidance were crucial to my development, and I deeply appreciate the time he invested in me.

I am grateful to Professor Costas Psychalinos from the University of Patras, Greece, for his valuable support in enhancing my PhD thesis with fractional order systems.

My heartfelt appreciation to the members of my PhD defense committee, Professor Marko Koričić, Professor Vladimir Čeperić, and Professor Tomislav Matić, for their thoughtful questions, valuable feedback, and insightful suggestions.

I sincerely thank to all members of the ENICS laboratory at Bar-Ilan University for their support in research during my stay in Israel.

A special thanks to my trusted friends, Marijan, Luka, Mario, Matija, Antonio, Mišel, Karlo, and Marin, for their continuous support and friendship throughout this journey.

Finally, I would like to express my sincere gratitude to my family, brothers Dorian and Leo, my mother Katarina, my father Damir, and my grandmother Marija, for their unconditional love, support, and encouragement.

### Abstract

The rapid advancement of Internet-of-Things (IoT) devices has pushed the boundaries of Systemon-Chip (SoC) solutions, leading to a higher demand for stable on-chip power supplies. The primary function of an integrated power management circuit is to generate required voltage levels on-chip from an external energy source while ensuring high energy efficiency, speedy response, and stability. Additionally, the energy harvesting function may be included as part of the power management circuit, enabling the utilization of energy from the environment to improve overall energy efficiency. The scientific contribution to the field of fully integrated power management was conducted in a way of designing and producing four distinguished integrated circuits: a stepdown DC-DC converter in TSMC 65nm, a boost DC-DC converter in TSMC 180nm, a low-power clock generator in TSMC 180nm, and a digitally controlled fractional-order capacitor in AMS 350nm. Measured and simulated results indicate that novel circuits and techniques developed during research for doctoral studies enable the state-of-the-art performance of DC-DC converters in terms of energy efficiency, power density, and speed. The fact that DC-DC converters play a crucial role in power management makes the presented circuits inspiring solutions for low-power applications of IoT devices.

**Keywords:** DC-DC converters, clock generators, energy harvesting, power management, analog techniques, efficiency, fractional order, regulation.

# Prošireni sažetak

### Integrirani sklop za upravljanje napajanjem zasnovan na analognim postupcima visoke učinkovitosti

Brzi napredak Internet-of-Things (IoT) uređaja doveo je do povećane potražnje za stabilnim izvorima napajanja izvedenim na čipu. Integrirani IoT uređaj obično zahtijeva više naponskih razina koje se generiraju iz jednog vanjskog izvora energije. Napon napajanja digitalne domene kreće se od 0.5 V do 1.2 V, dok analogni sklopovi zahtjevaju nešto viši napon za rad (1.2 V do 5 V). Vanjski izvor energije često je nestabilan, te može ovisti o temperaturi, šumu, potrošnji energije i drugim čimbenicima. Kod sustava koji koriste baterijsko napajanje, razina napona baterije može varirati ovisno o njenoj napunjenosti dok sklopovlje unutar čipa obično zahtijeva stabilan napon napajanja unutar određenih granica. Primarna funkcija potpuno integrirane jedinice za upravljanje napajanjem je osiguranje potrebnih napona napajanja za sustav na čipu uz što bolju energetsku učinkovitost, brzinu i stabilnost. Energetski učinkovitost cijelog sustava, čime se znatno produljuje vijek trajanja baterije (ili potrošnju alternativnog izvora energije). Jedinica za upravljanje napajanjem za najsuvremenije IoT uređaje obično se sastoji od nekoliko međusobno povezanih regulatora napona koji skupnim radom osiguravaju potrebne napone uzevši u obzir zahtjeve sustava.

Primarna funkcija regulatora napona, kao ključne komponente u upravljanju napajanjem, je pretvaranje jedne razine napona u drugu. Ovaj proces je ključan za održavanje stabilnog i reguliranog napajanja sustava. Regulator napona možemo opisati kroz sustav koji kao ulaznu veličinu prima ulazni napon i referentni napon, a na izlazu daje izlazni napon. Razina ulaznog napona koju regulator dobiva obično je nestabilna i nepredvidiva. Nasuprot tome, razina izlaznog napona mora biti regulirana i stabilna unutar određene tolerancije. Ovisno o vrsti regulatora, sustav može ili ne mora zahtjevati ulazni signal takta. Referentni napon smatra se konstantnom razinom napona na koji, u teoriji, ne utječu drugi čimbenici. U praksi referentni napon obično ima vrlo malu ovisnost o temperaturi, razini napona napajanja, šumu, opterećenju i ostalim faktorima, a koristi se kao referentna točka za regulaciju izlaznog napona. Ovisno o konfiguraciji regulatora,

izlazni napon može biti reguliran na razinu referentnog napona ili na razinu referentnog napona pomnoženog s cjelobrojnim faktorom. Jedan od glavnih parametara za svaki regulator napona je energetska učinkovitost, a definira se kao omjer izlazne i ulazne snage. Kod razmatranja integriranih regulatora, gustoća snage postaje važan parametar budući da površina silicija određuje cijenu izrade čipa. Definicija gustoće snage jednaka je omjeru izlazne snage i aktivne površine regulatora na čipu. Budući da regulatori napona mogu raditi s nizom različitih ulaznih i izlaznih napona, uveden je parametar nazvan omjer pretvorbe napona, a označava omjer između izlaznog i ulaznog napona. Valovitost izlaznog napona koristi se za opisivanje varijacija izlaznog napona za vrijeme statičkih uvijeta rada (obično se izražava kao vrijednost izmjenične komponente izlaznog napona od vrha do vrha), dok se varijacije izlaznog napona u dinamičkim uvjetima mogu opisati kroz propad ili nadvišenje napona. Glavni okidač za propad ili nadvišenje je brza prijelazna promjena izlazne struje. Proporcije napona valovitosti i propada odnosno nadvišenja uglavnom su određene brzinom regulatora i kapacitetom izlaznog kondenzatora. Dvije glavne kategorije regulatora napona su linearni regulatori i prekidački DC-DC konverteri. Osnovna razlika je u tome što linearni regulatori ne mijenjaju konfiguraciju u ovisnosti o vremenu (moguće ih je opisati jednim nadomjesnom strujnim krugom), dok prekidački regulatori rade u dvije faze koje se izmjenjuju u vremenu i svaka od faza ima zaseban nadomjesni strujni krug. Osnovno ograničenje kod linearnih regulatora je to što je teoretski maksimalna energetska učinkovitost jednaka omjeru pretvorbe napona. Bez obzira na ovaj faktor ograničenja, linearni regulatori naširoko se koriste kad god je to moguće zbog jednostavnosti, pouzdanosti i superiornih performansi u svim parametrima osim učinkovitosti za niski omjer pretvorbe napona. Drugo ograničenje linearnih regulatora je nemogućnost proizvodnje izlaznog napona većeg od ulaznog. Zbog svoje nelinearne prirode rada, rješenje za oba ograničenja pružaju prekidački DC-DC konverteri (pretvarači). Paralelno s razvojem DC-DC konvertera, uveden je dodatni pokazatelj vrijednosti nazvan faktor poboljšanja učinkovitosti kako bi se posebno opisali DC-DC pretvarači. Razlog tome leži u činjenici da klasična učinkovitost ponekad može dovesti u zabludu jer se implementiraju različiti omjeri pretvorbe napona. Složenost postizanja visoke učinkovitosti obrnuto je proporcionalna s omjerom pretvorbe napona (za niži omjer pretvorbe napona izvedba je složenija s više sklopki i više reaktivnih elemenata). Nadalje, DC-DC pretvarači s visokim omjerom pretvorbe napona (blizu 1) mogu se jednostavno zamijeniti linearnim regulatorima, čime se smanjuje njihova vrijednost u praktičnim primjenama. Faktor poboljšanja učinkovitosti važan je parametar kada se

uspoređuju silazni (buck) DC-DC pretvarači, jer uzima u obzir i učinkovitost i omjer pretvorbe napona. U prektičnom smislu ovaj parametar opisuje koliko je razmatrani DC-DC pretvarač bolji u odnosu na idealan linearni regulator u pogledu energetske učinkovitosti, za isti omjer pretvorbe napona. Ovisno o vrsti reaktivnog elementa korištenog za pohranu energije, razlikujemo dvije skupine DC-DC pretvarača: kapacitivne i induktivne. Glavna razlika je u tome što kapacitivni pretvarači pohranjuju energiju u obliku napona na kondenzatoru, dok induktivni pretvarači pohranjuju energiju u obliku struje kroz zavojnicu. Kod potpuno integriranih sustava, kapacitivni DC-DC pretvarači superiorni su u gotovo svim aspektima u odnosu na induktivne i stoga nailaze na mnogo širu upotrebu. Razlog tome je teškoća u proizvodnji visokokvalitetnih zavojnica na siliciju. Glavni nedostatak kapacitivnih DC-DC pretvarača je fiksan omjer pretvorbe napona koji je definiran mrežnom konfiguracijom prekidajućih kondenzatora.

Proces kojim se električna energija dobiva iz vanjskih izvora (svijetlost, mehaničke vibracije, toplina, zračenje, itd.) i koristi kao izvor napajanja za električne uređaje naziva se prikupljanje energije. Prikupljena energija može se koristiti kao jedini izvor napajanja sustava ili se može koristiti kao djelomični izvor energije za produljenje vijeka trajanja baterije. Zbog trenda samodostatnih uređaja male snage, prikupljanje energije često se implementira kao dio sustava upravljanja napajanjem. Potpuno integrirani IoT uređaji posebno su zanimljivi za prikupljanje energije budući da je sustave niske potrošnje lakše proizvesti na čipu, što omogućuje da prikupljena energija postane glavni izvor napajanja. Budući da ambijentalni izvori energije obično generiraju električne signale u obliku neprikladnom za napajanje (preniskog napona i nestabilni), središnji zadatak procesa prikupljanja energije vrti se oko generiranja razina izlaznog napona pogodnih za daljnju upotrebu. Rješenje za ovaj problem obično je dodatni DC-DC pretvarač s omjerom pretvorbe napona većim od jedan (boost DC-DC pretvarač). U slučaju da je prikupljeni signal izmjeničnog valnog oblika, kao što je radio val, vibracija piezoelektričnog senzora i slično, potrebno ga je prvo ispraviti, a zatim pojačati na potrebnu naponsku razinu. Za razliku od konvencionalnog DC-DC pretvarača, gdje se snaga regulira na temelju struje opterećenja, DC-DC prikupljač treba regulirati svoju snagu na temelju ulaznog naboja. Na taj se način energija sakuplja uz maksimalnu učinkovitost. Izlazni napon u ovom slučaju nije toliko kritičan jer se obično spaja na veliki kondenzator ili bateriju, što ga čini stabilnim. Sekundarna regulacijska petlja ponekad se može implementirati za povremeno pražnjenje izlaznog čvora u bateriju. Sustav može biti samodostatan ako prosječna prikupljena energija premašuje potrošnju energije kruga. Međutim,

gotovo je uvijek potreban neki oblik pohrane energije jer je prikupljeni signal nepredvidiv. Čak i ako je prosječna potrošnja energije manja od prosječne prikupljene energije za dulji vremenski interval, u nekim trenucima može biti suprotno, što bi uzrokovalo kvar sustava bez pohrane energije.

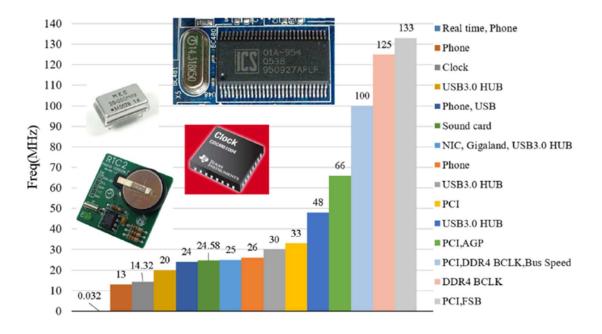

Generator takta je električni krug korišten za proizvodnju signala takta. Signal takta obično je pravokutnog valnog obilika, poznate i jasno definirane frekvencije, te se koristi za sinkronizaciju ostalih krugova u sustavu. Za kvalificiranje i usporedbu generatora takta potrebno je uzeti u obzir nekoliko važnih parametara. Uz osnovne parametre kao što su raspon napona napajanja i raspon izlazne frekvencije, potrebno je definirati dodatne parametre kao što su potrošnja energije, radni ciklus i temperaturni koeficijent. Budući da se generatori takta koriste za vrlo širok raspon aplikacija, važnost određenog parametra ovisi o primjeni. Jednostavna potrošnja energije izražena u vatima ponekad nije dovoljno dobar parametar za usporedbu budući da je veća vjerojatnost da će generatori takta s višom frekvencijom imati veću potrošnju energije. Iz tog razloga, dodatni parametar koji se zove energetska učinkovitost definiran je kao omjer potrošnje energije i frekvencije. Energetska učinkovitost jedan je od kritičnih parametara za generatore takta koji se korištenje energije. IoT uređaji male snage obično rade u stanju mirovanja većinu vremena. Faktor niske aktivnosti znači da se mnogi podsustavi, uključujući generatore takta, moraju često aktivirati i deaktivirati. U takvom scenariju vrijeme pokretanja postaje važan parametar.

Studija prethodnog stanja tehnike koja se odnosi na integrirano upravljanje napajanjem pokazuje da su područja male snage posebno izazovna za postizanje dobrih performansi. Razlog tome je ograničena količina raspoložive snage koju je potrebno rasporediti između podsklopova zaduženih za obavljanje različitih zadataka. Daljnja analiza pokazuje da prethodno objavljani DC-DC pretvarači male snage imaju problema s niskom učinkovitošću, niskom gustoćom snage i sporim prijelaznim odzivom. Također, često zahtijevaju veliki izlazni kondenzator što ograničava njihovu praktičnu primjenu.

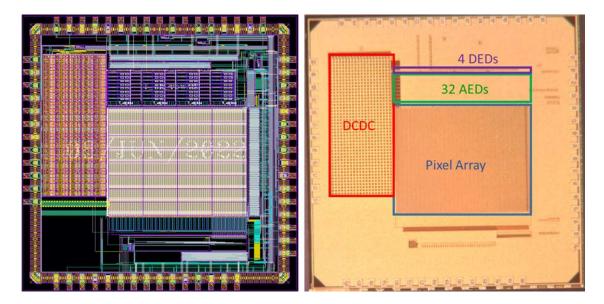

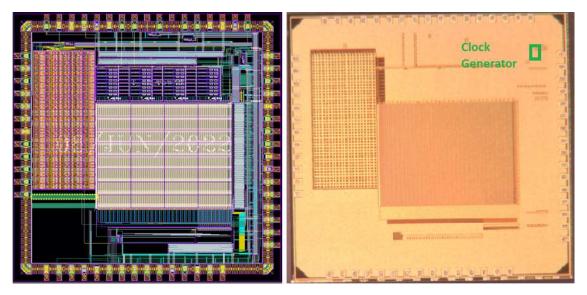

Glavni fokus ovog doktorskog rada je poboljšanje upravljanja napajanjem u područjima energetske učinkovitosti i brzine uvođenjem inovativnih integriranih sklopova i tehnika. Za potrebe istraživanja proizvedena su četiri potpuno integrirana sustava, a rezultati su objavljeni u obliku jednog konferencijskog rada i tri rada u časopisima. Drugo poglavlje opisuje silazni (buck) DC- DC pretvarač proizveden u tehnologiji TSMC 65nm i objavljen kao konferencijski rad s proširenom verzijom u časopisu. Uzlazni (boost) DC-DC pretvarač proizveden u tehnologiji TSMC 180nm kao dio platforme za senzor slike, objavljanoj u časopisu, predstavljen je u trećem poglavlju. Generator takta male snage, kao dio iste platforme za senzor slike, ilustriran je u četvrtom poglavlju. Dodatni doprinos području potpuno integriranog upravljanja napajanjem implementiran je u obliku digitalno kontroliranog kondenzatora necjelobrojnog reda, dizajniranog u tehnologiji AMS 350nm, objavljenog u časopisu, te opisanog u petom poglavlju.

Osnovni znanstveni doprinos, kako u pogledu energetske učinkovitosti tako i u pogledu brzine, opisan je u drugom poglavlju. Silazni DC-DC pretvarač temeljen na inverteru pokazuje poboljšanje stanja tehnike svojim faktorom poboljšanja efikasnosti od 66%, gustoćom snage od 2.56 mW/mm<sup>2</sup> i brzim prijelaznim odzivom koji ne pokazuje propade niti nadvišenja . Brzina predstavljenog DC-DC pretvarača omogućuje mu rad s minimalnim izlaznim kondenzatorom od 50pF, što dodatno štedi površinu silicija. Glavna nova značajka koja je omogućila vrhunske rezultate bila je komparator zasnovan na inverteru. Loše strane inverterskog komparatora su prevladane dodatnom regulacijskom petljom za napon napajanja invertera. Precizne analogne tehnike korištene su za postizanje dodatnih značajki kao što su mogućnost korištenja srednjih izlaznih napona i smanjena potrošnja uslijed prekidanja. Učinkovitost, brzina i gustoća snage predloženog DC-DC pretvarača čine ga korisnim rješenjem za sveprisutne integrirane sustave za upravljanje napajanjem u IoT uređajima.

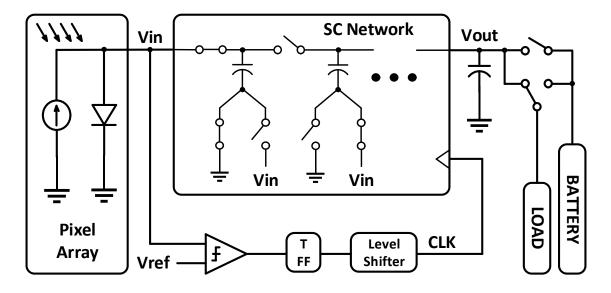

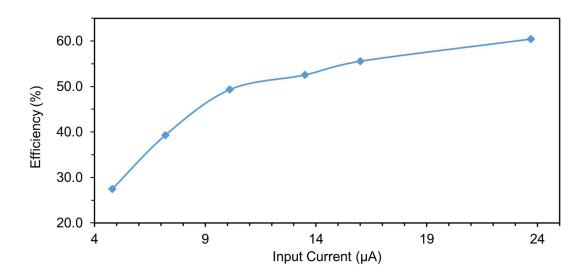

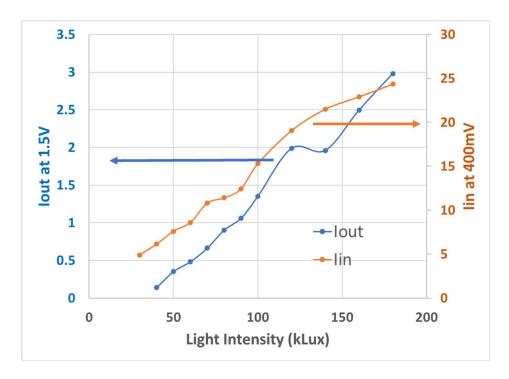

Dodatni znanstveni doprinosi prikazani su u trećem, četvrtom i petom poglavlju. Uzlazni DC-DC pretvarač kao dio platforme za senzor slike opisan je u trećem poglavlju. Glavna svrha DC-DC pretvarača u ovoj aplikaciji je povećanje razine napona u procesa prikupljanja energije, čime se poboljšava energetska učinkovitost cijelog sustava. Energija je sakupljena iz naboja prikupljenog od fotodioda. Budući da fotodiode počinju puštati struju blizu razine napona praga (~500 mV), naponski čvor koji prikuplja naboj potrebno je držati ispod te razine (~450 mV). Implementirani DC-DC pretvarač koristi se za povećanje napona diode na razinu prikladnu za punjenje baterije (~1.5 V) s vršnom učinkovitošću od 60%. Potrebno je naglasiti da se iste fotodiode koje služe za prikupljanja energije također koriste za očitanje slike, a detekcija događaja provodi se tijekom prikupljanja energije. Ova nova značajka omogućuje dulje cikluse prikupljanja energije što dovodi do boljih značajki samoodrživih senzora slike.

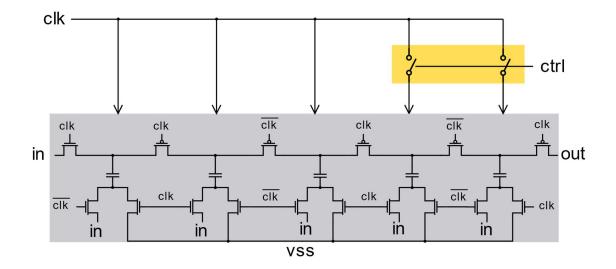

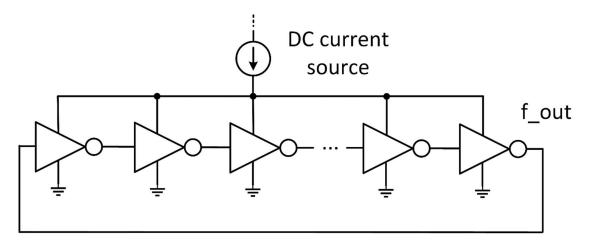

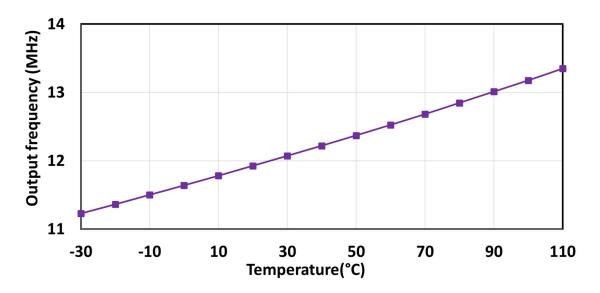

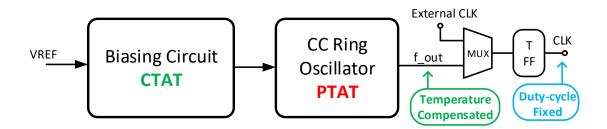

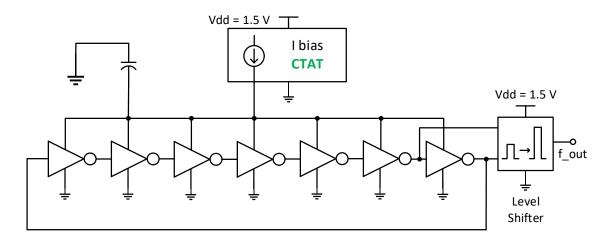

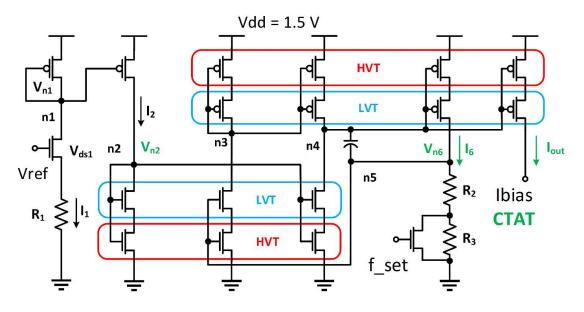

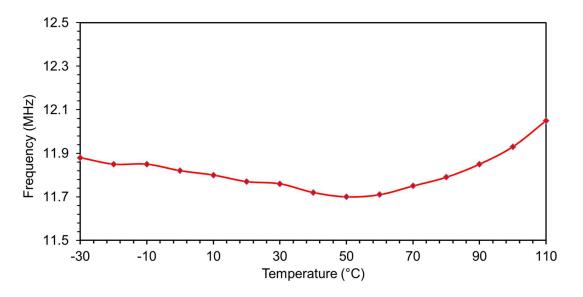

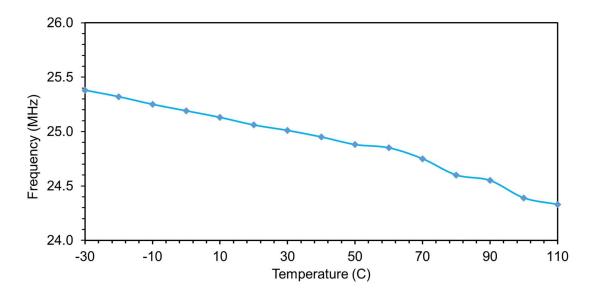

Generator takta male snage s implementiranom kompenzacijom temperature i radnog ciklusa opisan je u četvrtom poglavlju. Primjena sklopa demonstrirana je u platformi za senzor slike, također spomenutoj u trećem poglavlju. Postignuto je dodatno poboljšanje energetske učinkovitosti sustava korištenjem generatora takta male snage dizajniranog posebno za ovu svrhu. Strujno kontrolirani prstenasti oscilator koristi se za proizvodnju početnog signala, koji se zatim pomiče po razini, te mu se kompenzira radni ciklus. Glavni nedostatak ovakvog dizajna je velika temperaturna ovisnost strujno upravljanog prstenastog oscilatora. Ovaj problem prevladan je uvođenjem izvora struje koji ima suprotnu temperaturnu ovisnost od oscilatora, te je na taj način izvedena kompenzacija temperaturnog koeficienta. Generator takta pokazuje vrhunske značajke u pogledu površine od 0.019mm2, energetske učinkovitosti od 0.6  $\mu$ W/MHz (0.3  $\mu$ W/Mhz prije kompenzacije radnog ciklusa), te vremena pokretanja od 5  $\mu$ s.

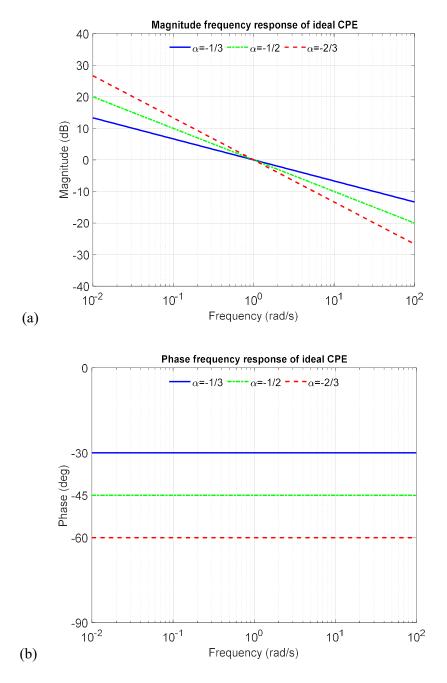

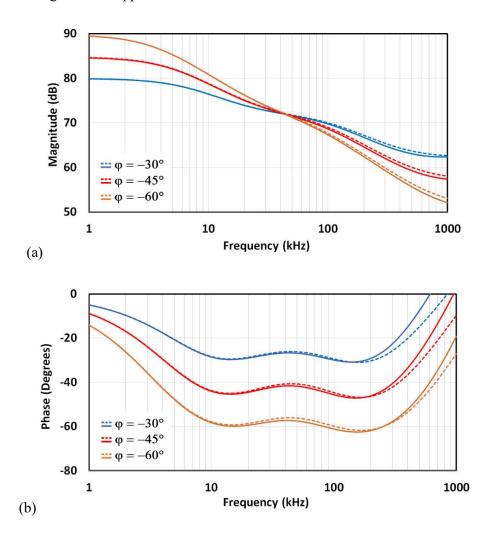

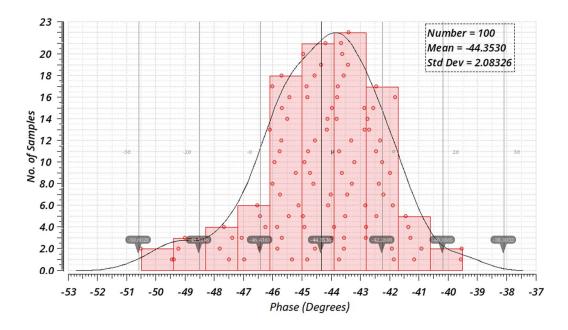

Peto poglavlja opisuje digitalno upravljani kondenzator frakcionalnog reda koji radi u frekvencijskom rasponu relevantnom za DC-DC pretvarače s prekidajućim kondenzatorima. Ovakava realizacija utječe na sustave upravljanja napajanjem iz razloga što frakcionalni kondenzator može biti korišten kao reaktivni element unutar jezgre DC-DC pretvarača ili regulacijski element unutar regulacijske petlje u svrhu poboljšanja energetske učinkovitosti. Dizajnirani frakcionalni kondenzator može postići tri različita fazna pomaka: -30°, -45° i -60°. Na taj način djeluje kao frakcija standardnog kondenzatora (1/3, 1/2 i 2/3).

Integrirani sklopovi opisani u ovom diplomskom radu unaprijedili su područje potpuno integriranog upravljanja napajanjem u nekoliko aspekata, što ih čini inspirativnim rješenjima za aplikacije niske potrošnje IoT uređaja.

**Ključni riječi:** DC-DC pretvarači, generator signala takta, prikupljanje energije, upravljanje napajanjem, analogne tehnike, učinkovitost, frakcionalni red, regulacija.

### Contents

| 1. INTRODUCTION TO AN INTEGRATED POWER MANAGEMENT SYSTEM    | /IS1 |

|-------------------------------------------------------------|------|

| Power Management                                            | 1    |

| Voltage Regulators                                          | 2    |

| Energy Harvesting                                           | 12   |

| Low-Power Clock Generation                                  | 13   |

| Fractional-Order Elements in Power Management               | 15   |

| Prior Art and Motivation                                    | 16   |

| 2. SWITCHED-CAPACITOR DC-DC BUCK CONVERTER                  | 19   |

| Introduction                                                | 19   |

| Architecture and Circuit Design                             | 19   |

| Control Loop and Clock Generation                           | 19   |

| Switched-Capacitor Network                                  | 21   |

| Inverter-based Comparator                                   | 24   |

| Watchdog Mechanism                                          | 26   |

| Internal Load Setup                                         |      |

| Simulated Results                                           | 29   |

| Measured Results                                            | 34   |

| Discussion                                                  |      |

| Conclusion                                                  | 41   |

| 3. A PHOTOVOLTAIC ENERGY HARVESTER AS PART OF THE IMAGE SEN |      |

| PLATFORM                                                    |      |

| Introduction                                                |      |

| System Architecture                                         |      |

| Harvester Architecture                                      |      |

| Measured Results                                            |      |

| 4. LOW-POWER TEMPERATURE-COMPENSATED CLOCK GENERATOR        |      |

| Introduction                                                |      |

| Circuit Architecture and Simulated Results                  |      |

| Measured Results                                            | 57   |

| Conclusion                                                  | 59   |

| 5. DIGITALLY CONTROLLED FRACTIONAL-ORDER ELEMENTS           | 61   |

| Introduction                                                | 61   |

| Fractional-Order Impedance and Transfer Function            | 62   |

| Basic Definitions                                           | 62   |

| Approximated Transfer Function H(s) and the Impedance Z(s) of the nth-order | 64 |

|-----------------------------------------------------------------------------|----|

| Design Procedure                                                            | 66 |

| Simulated Post-Layout Results                                               | 75 |

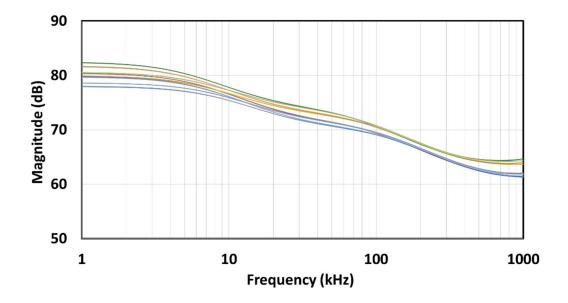

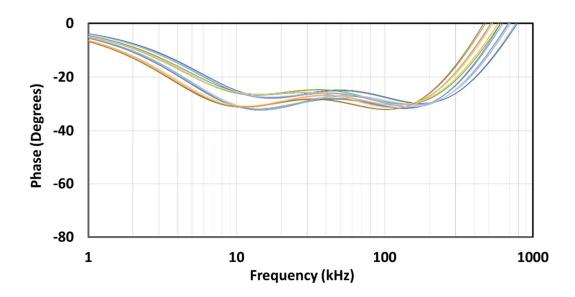

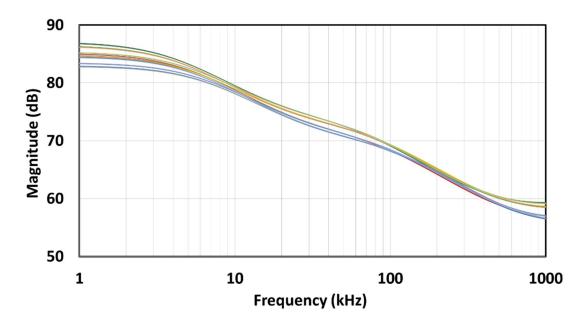

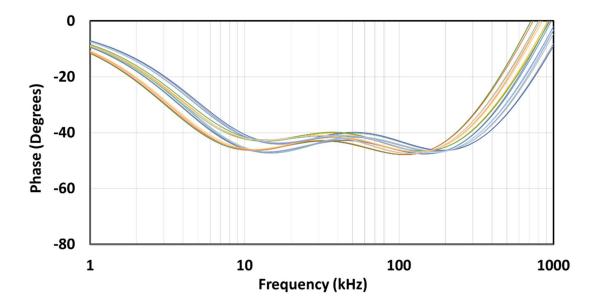

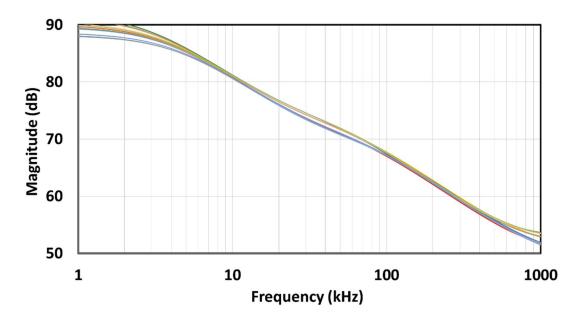

| AC Analysis                                                                 | 75 |

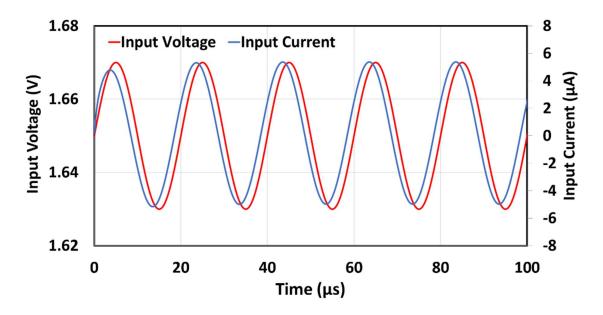

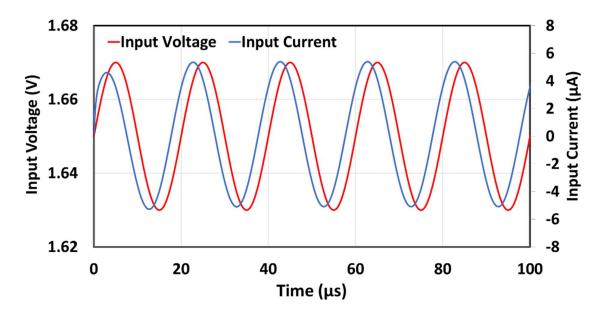

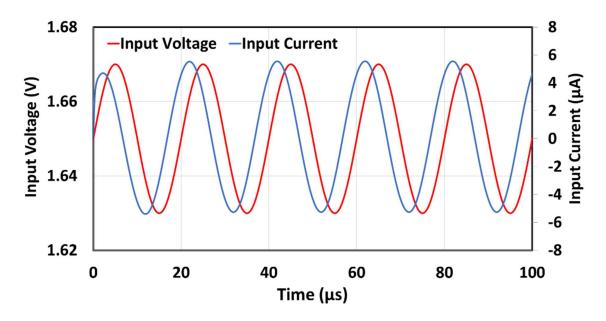

| Transient Analysis                                                          | 76 |

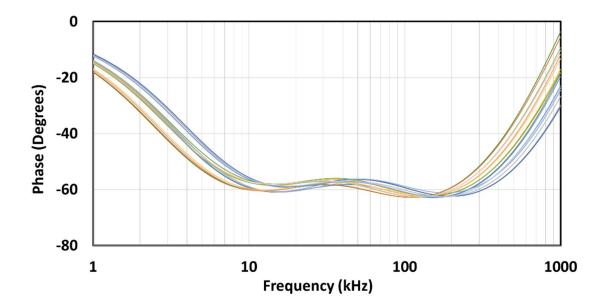

| PVT Corner Analysis                                                         | 78 |

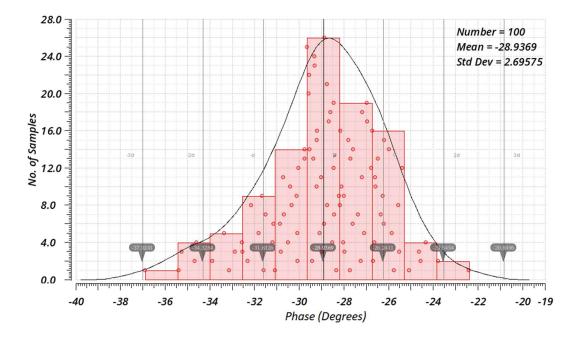

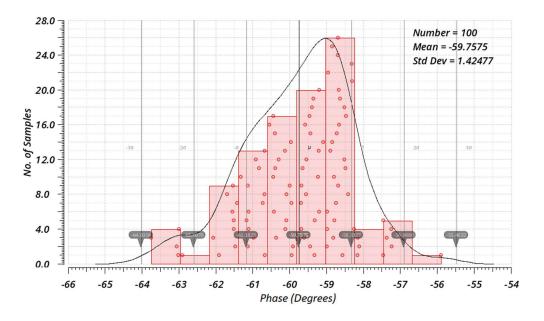

| Monte Carlo Analysis                                                        | 81 |

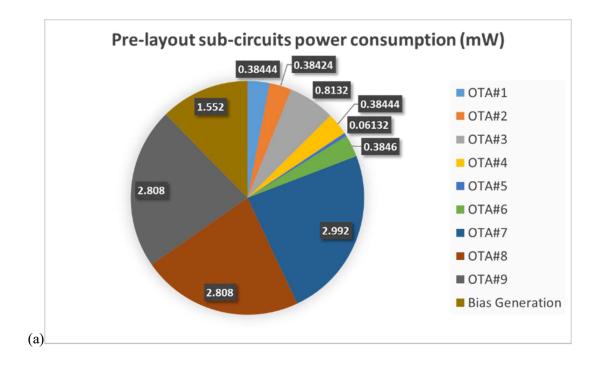

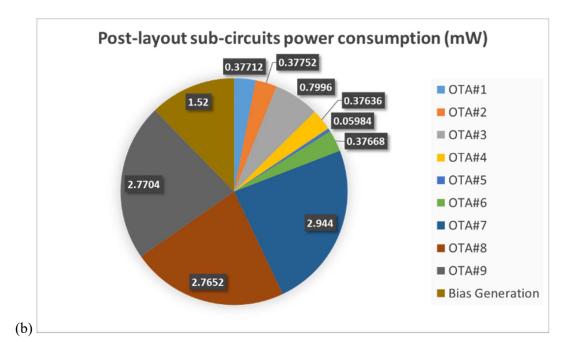

| Power Consumption                                                           | 83 |

| Conclusion                                                                  | 84 |

| 6. CONCLUSION                                                               | 86 |

| References                                                                  | 88 |

| Biography                                                                   | 93 |

| Publications:                                                               | 93 |

| Životopis                                                                   | 95 |

### 1. INTRODUCTION TO AN INTEGRATED POWER MANAGEMENT SYSTEMS

#### **Power Management**

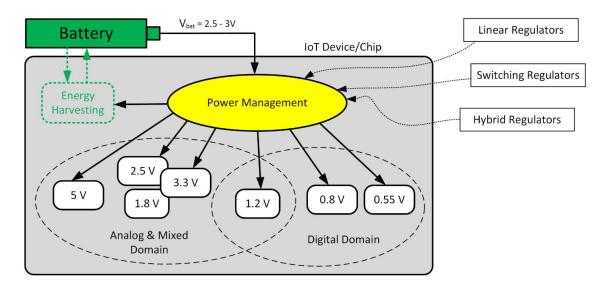

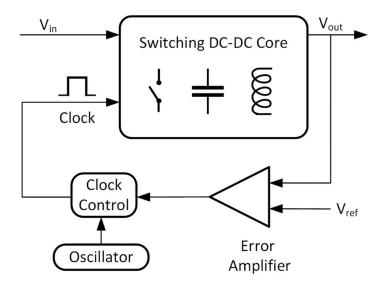

The rapid advancement of Internet-of-Things (IoT) devices has pushed the boundaries of System-on-Chip (SoC) solutions, leading to a higher demand for stable on-chip power supplies. An integrated IoT device typically requires multiple voltage levels to be generated from a single external energy source. The digital domain supply voltages range from 0.5 to 1.2V, while analog circuits need a slightly higher voltage to operate (1.2V to 5V). However, the external energy source is often unstable, with temperature, noise, power consumption, and other factors influencing voltage variations. For instance, the voltage level of a battery can vary depending on its charge. Yet, the circuits inside the chip usually require a stable voltage within a certain limit. Moreover, the use of energy harvesting within the system is becoming more prevalent due to the demand for self-sustaining, low-power devices. The primary function of a fully integrated power management unit, as depicted in Fig. 1.1, is to address all these requirements while ensuring high energy efficiency, speed, and stability.

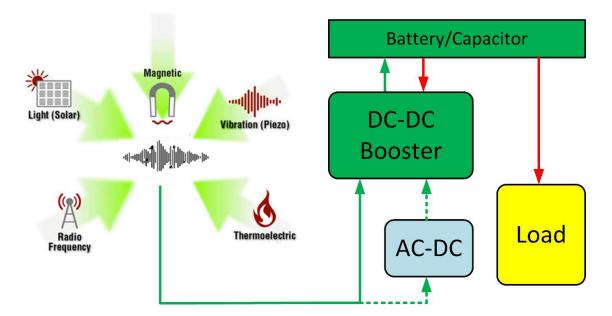

Fig. 1.1. Power Management for IoT Devices.

Energy-efficient power management is of utmost importance as it directly influences the energy efficiency of the entire system, thereby significantly extending the life of the battery (or alternative energy source). A power management unit for cutting-edge IoT devices typically comprises several interconnected voltage regulators that work in tandem to produce voltage supplies based on the system's requirements, highlighting the benefits of energy-efficient power management.

#### Voltage Regulators

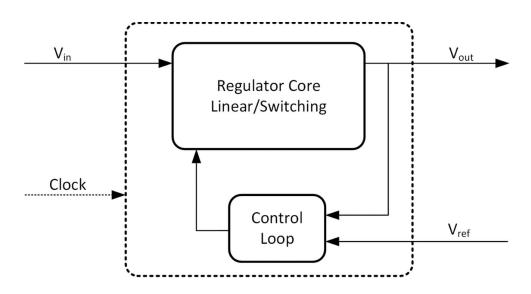

The primary function of a voltage regulator, a key component in power management, is to convert electrical energy from the input voltage level (Vin) to the output voltage level (Vout), as demonstrated in Fig. 1.2. This process is crucial in maintaining a stable and regulated power supply for the system.

Fig. 1.2. Voltage regulator.

The input voltage level is typically expected to be unstable and unpredictable. In contrast, the output voltage level needs to be regulated and stable within a certain tolerance. Depending on the type of regulator, the system may or may not need an input clock signal. Voltage reference  $(V_{ref})$  is considered a constant voltage level that, in theory, is not affected by other factors. In practice,  $V_{ref}$  usually has some very small dependence on the temperature, supply voltage level, noise, load, etc. It is used as a reference point for the regulation of the output voltage.

Depending on the regulator configuration,  $V_{out}$  can aim to be equal to  $V_{ref}$  or equal to  $V_{ref}$  multiplied by some constant factor.

One of the main parameters for every voltage regulator is power efficiency ( $\eta$ ), and it is defined as

$$\eta = \frac{P_{out}}{P_{in}} \tag{1.1}$$

where the output power is  $P_{out}$  and the input power is  $P_{in}$ . When integrated regulators are considered, Power-Density (PD) becomes an important parameter since the silicon area determines the price of the chip. It is defined as

$$PD = \frac{P_{out}}{A} \tag{1.2}$$

where *A* stands for the active area of the regulator on silicon. Since voltage regulators can operate with a variety of different input and output voltages, a parameter called Voltage-Conversion-Ratio (VCR) is introduced as

$$VCR = \frac{V_{out}}{V_{in}} \tag{1.3}.$$

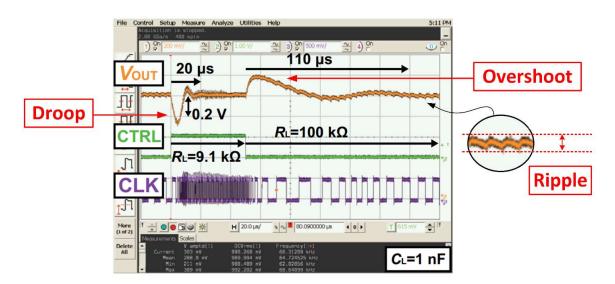

Output voltage ripple ( $V_{ripple}$ ) is used to describe peak-to-peak variations of the output voltage during the static conditions, while output voltage variations in the dynamic conditions could be observed as voltage droop and overshoot. The main trigger for droops or overshoots is a fast transient output current ( $I_{out}$ ) change. Proportions of both  $V_{ripple}$  and droops/overshoots are mainly determined by the regulator speed and capacitance of the decoupling capacitor ( $C_{out}$ ). To illustrate the described parameters, a previously published transient response of the fully integrated DC-DC converter is shown in Fig. 1.3 [1]. Significant droop and overshoot events in  $V_{out}$  can be observed during the transient load changes (the load resistance is varied from 100 k $\Omega$  towards 9.1 k $\Omega$  and back to 100 k $\Omega$ ). Also, in static conditions, when the load resistance is constant, an output voltage ripple is visible. The clock signal waveform shows that the output power regulation is conducted by the clock frequency change.

Fig.1.3. Ripple, droop, and overshoot.

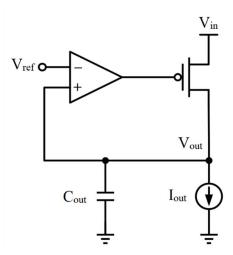

Two main categories of voltage regulators are linear and switching DC-DC converters. Figure 1.4 shows an example of a Low-Drop-Out (LDO) linear regulator where the simple regulation loop is implemented with an operation amplifier.

Fig. 1.4. Low-Drop-Out (LDO) linear regulator.

The resistance of the PMOS transistor is regulated so that  $V_{out}$  always tends to follow  $V_{ref}$ . It can be observed that the power loss will always be proportional to the difference between  $V_{in}$  and  $V_{out}$ . This fact results in the main limitation of the efficiency regarding the linear voltage regulators:

$$\eta_{max} = VCR \tag{1.4}.$$

Regardless of this limitation factor, linear regulators are widely used whenever possible due to simplicity, reliability, and superior performance in all areas except efficiency for low VCR. Another limitation of the linear voltage regulators is the inability to produce  $V_{out}$  higher than  $V_{in}$ . The solution for both limitations is provided by switching DC-DC converters. The block diagram of the generic DC-DC converter is presented in Fig. 1.5. The main reason for its nonlinear behavior originates from the DC-DC core that changes configuration over time (contains switches and reactive elements). The DC-DC converters require a clock signal and usually operate in two phases. During the first phase (charge phase), the charge is transported from the energy source ( $V_{in}$ ) and stored inside a reactive element (capacitor or inductor). In the second phase, the charge is delivered to the load ( $V_{out}$ ). The control loop of the DC-DC converter usually regulates output power by the clock frequency or duty cycle.

Fig. 1.5. Nonlinear (switching) regulator.

Following the development of the DC-DC converters, an additional Figure-Of-Merit (FOM) called Efficiency-Enhancement-Factor (EEF) is introduced to describe step-down DC-DC converters specifically. The reason for this lies in the fact that classical efficiency sometimes could be misleading because various VCRs are being implemented. Difficulty in achieving high efficiency is inversely proportional with converters VCR due to the complexity of the core (more switches and more reactive elements). Additionally, DC-DC converters with high VCR (close to 1) can be easily replaced with linear regulators, thus reducing their value in practical applications.

The EEF is an important parameter when comparing step-down (buck) DC-DC converters, as it considers both the efficiency and the VCR [2]. EEF is defined as

$$EEF = 1 - \frac{\eta_{lin}}{\eta_{sw}} \tag{1.5}$$

where  $\eta_{\text{lin}}$  is the efficiency of an ideal LDO, and  $\eta_{\text{sw}}$  is the efficiency of the DC-DC converter under consideration. For instance, a DC-DC converter with a VCR of 0.8 and an efficiency of 80% may not be useful, as it is similar to an LDO, resulting in an EEF of 0. Conversely, a DC-DC converter with an efficiency of 50% but a VCR of 0.2 would have an EEF of 60%, indicating superior performance over an LDO. The VCR used for EEF calculation is the actual achieved ratio between V<sub>out</sub> and V<sub>in</sub>, which is slightly lower than the topology VCR determined by the number of flying capacitors. The reason for that lies in the fact that "real" VCR takes into account additional IR drop that always exists at the output voltage.

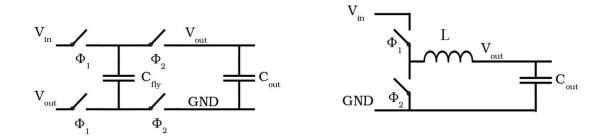

Fig. 1.6. Simple concept of the capacitive and inductive DC-DC converter [2].

Depending on the type of reactive element, two groups of DC-DC converters can be distinguished: capacitive and inductive (Fig. 1.6). The main difference is that capacitive converters store energy in the form of voltage on the capacitor (Cfly), while inductive converters store energy in the form of current through the inductor (L). Table 1.1 shows a general comparison between the two types of integrated DC-DC converters [3].

|                             | Inductive type           | Capacitive type    |

|-----------------------------|--------------------------|--------------------|

| Energy Transfer             | Low Q-factor             | High Q-factor      |

| Inpact of Scaling           | No influence on Q-factor | Improving Q-factor |

| ΕΜΙ                         | EF radiated              | EF between plates  |

| Modeling                    | Finite element           | Spice              |

| $\eta_{	ext{theory}}$       | 100%                     | <100%              |

| $\mathbf{\eta}_{practical}$ | Low                      | High               |

| Flexibility                 | Broad I/O range          | Small I/O range    |

Table 1.1. Comparison between Inductive and capacitive DC-DC converter type

Unlike in the case of non-integrated converters, it can be observed that capacitive DC-DC converters are superior in many areas and thus have much more widespread usage. The reason for that is the difficulty in producing high-quality inductors in silicon. The quality of the reactive elements is quantified in the Quality factor (Q-factor) in the following equations:

$$Q_L = \frac{2\pi f L}{R} \tag{1.6}$$

$$Q_C = \frac{2\pi f C}{R} \tag{1.7}$$

where R stands for equivalent serial resistance of the considered reactive element while f represents the frequency of interest.

The main disadvantage of capacitive DC-DC converters is that their VCR depends on the Switch-Capacitor (SC) network configuration. Therefore, many different SC networks are used

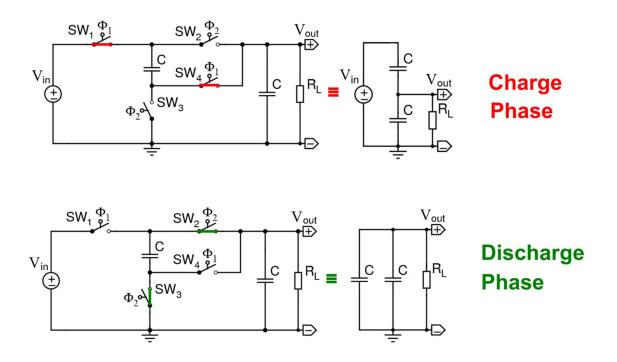

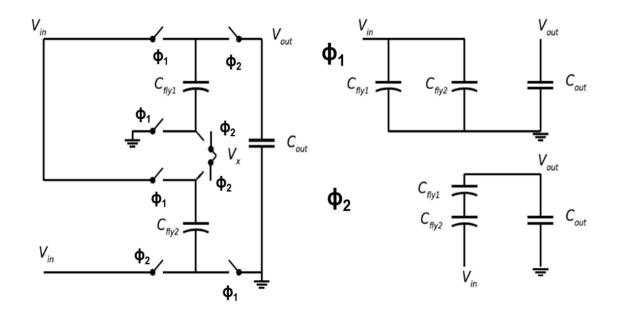

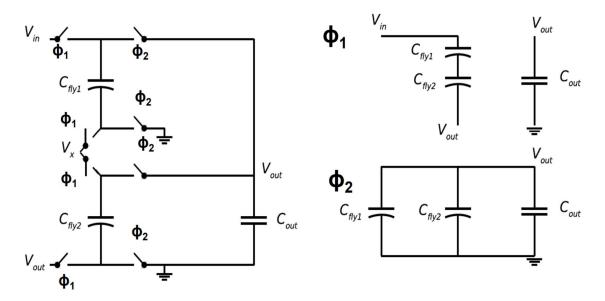

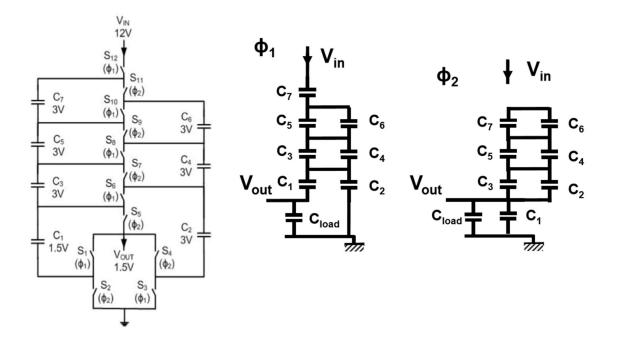

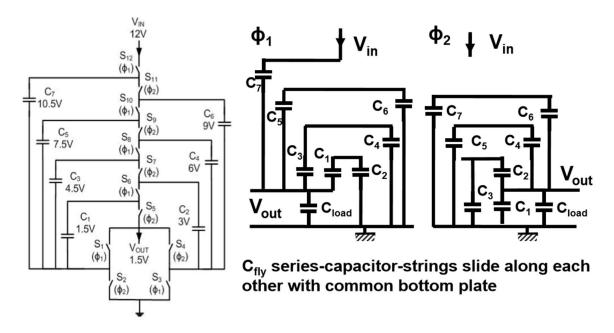

to achieve desired VCRs. Fig. 1.7 shows an example of a stacked SC network with charge and discharge phases including equivalent electrical circuits.

Fig. 1.7. Operating phases of the DC-DC converters [3].

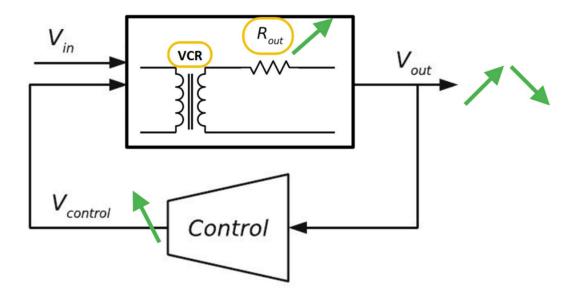

Even though the configuration VCR is a fixed number,  $\frac{1}{2}$  in this case, the output voltage can be regulated to some extent by changing the output resistance (R<sub>out</sub>) of the DC-DC converter, as shown in Fig. 1.8. The real ratio of the V<sub>out</sub> and V<sub>in</sub> is always going to be lower than topology VCR due to the voltage drop on the equivalent R<sub>out</sub>. The main factor that determines R<sub>out</sub> is switching frequency (clock frequency). With a higher switching frequency, the DC-DC converter is able to deliver more charge to the V<sub>out</sub>, and thus, the load sees a lower R<sub>out</sub>. The regulation loop aims to adjust the clock frequency depending on the load current.

Fig. 1.8. Output resistance control [3].

Figures 1.9 - 1.12 [3] show different SC networks that are used to accomplish various VCRs with equivalent circuits for both phases. Parallel-series SC network can be used in cases when VCR is greater than one, i.e., V<sub>out</sub> is greater than V<sub>in</sub> (Fig. 1.9). Ladder SC network, shown in Fig. 1.11, features all flying capacitors having the same voltage between the plates. This can be useful since the V<sub>in</sub> is divided, so each capacitor needs to sustain only a fragment of it. Ladder-star represents a variation where all bottom plates of the C<sub>fly</sub> are connected, thus reducing the effect of the parasitics (Fig. 1.12). The ladder-star SC network is particularly important in the case of integrated DC-DC converters since the parasitic capacitance of the C<sub>fly</sub> could be as large as 10% of the nominal capacitance value.

Fig. 1.9. Parallel-series SC network.

Fig. 1.10. Series-parallel SC network.

Fig. 1.11. Ladder SC network.

Fig. 1.12. Ladder-star SC network.

#### **Energy Harvesting**

The process by which electrical energy is derived from external sources (light, mechanical vibrations, heat, radiation, etc.) and used as a power supply for electrical circuits is called Energy Harvesting (EH). Harvested energy can be used as the sole power source of the system, or it can be utilized as a partial power source to prolong battery life [4]. Due to the trend of low-power, self-sufficient devices, energy harvesting is frequently implemented as a part of the power management system. Fully integrated IoT devices are especially interesting for energy harvesting since the low-power systems are easier to manufacture on-die, enabling harvested energy to become the main power source. Since the ambiental energy sources typically generate electric signals in a form unsuitable for a power supply (too low and unstable), the central task of the energy harvesting process revolves around the generation of output voltage levels suitable for further usage. The solution for this problem is usually another DC-DC converter with a VCR greater than one (boost DC-DC converter), as shown in Fig 1.13.

Fig 1.13. Energy Harvesting concept.

In case the harvested signal is AC, such as a radio wave, vibration from a piezoelectric sensor, etc., it must be first rectified and then boosted to the required voltage. Unlike the conventional DC-DC converter, where the power is regulated based on the load current, the DC-DC harvester needs to regulate its power based on the input charge [4]. This way, energy is harvested at maximum efficiency. The output voltage, in this case, is not so critical since it usually connects

to the large capacitor or battery, which makes it stable. The secondary regulation loop could sometimes be implemented to discharge the output node to the battery periodically.

The system can be self-sufficient if the average harvested energy exceeds the circuit's power consumption. However, some form of energy storage is almost always necessary because the harvested signal is unpredictable. Even if the average power consumption is lower than the average harvested power, it could be the opposite at some given moments, which would create system malfunction without energy storage.

#### **Low-Power Clock Generation**

A clock generator is an electric circuit that produces a clock signal used to synchronize the other circuits in the system. A clock generator is sometimes also called an oscillator, even though the term 'oscillator' has a wider definition, and some oscillators are unsuitable for producing clock signals (for instance, sine wave oscillator). Several important parameters must be considered to qualify and compare clock generators. In addition to basic parameters like supply voltage range and output frequency range, additional parameters such as power consumption, duty cycle, temperature coefficient, etc., need to be defined. In the field of integrated systems, area becomes an important parameter. Since the clock is used for a large variety of applications, the importance of the specific parameter depends on the application.

Simple power consumption (PC) expressed in Watts might sometimes be misleading since higher-frequency clocks are more likely to have higher power consumption. For that reason, an additional parameter called power efficiency is defined as the ratio of PC and frequency. The unit practical for integrated clock generators is  $\mu$ W/MHz. The same parameter is sometimes referred to as energy efficiency, and the unit used is pJ/cycle (both units are the same in value,  $\mu$ W/MHz = pJ/cycle). Power efficiency is one of the critical parameters for clock generators used in power management since the main purpose of power management is efficient energy usage.

Low-power IoT devices usually operate in standby mode for most of the time. A low activity factor means many sub-systems, including clock generators, must be activated and deactivated frequently. In such a scenario, startup time becomes an important parameter.

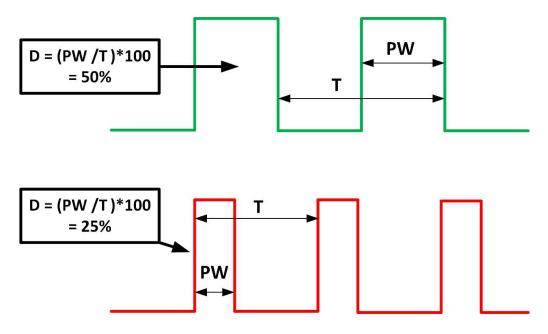

A square wave oscillator's duty cycle marks the pulse width (PW) to period (T) ratio. It is usually defined as a percentage or just a number between 0 and 1. A graphical explanation of the duty cycle is provided in Fig. 1.14.

Fig. 1.14. Duty cycle illustration.

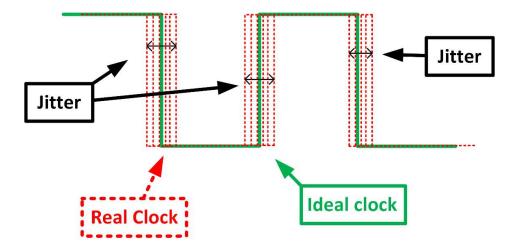

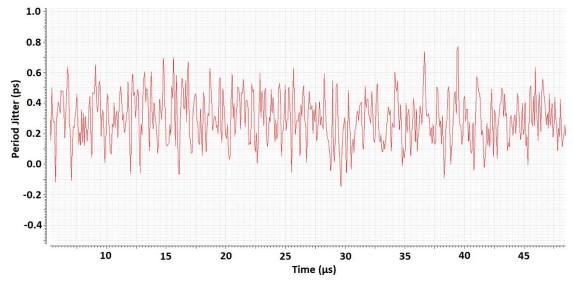

Period Jitter is the parameter that describes variations in the clock's period caused by thermal noise and other disturbing factors. It is usually expressed as a peak-to-peak (P2P) variation, RMS, or standard deviation over a large number of samples (10000 typically). Since Period Jitter is a type of noise, RMS can be estimated from peak-to-peak variations as Jitter<sub>RMS</sub>=Jitter<sub>P2P</sub>/8. It is sometimes useful to present Jitter as a percentage of the clock period so that a comparison between clock generators at different frequencies can be conducted. Figure 1.15 illustrates how peak-to-peak period jitter is measured.

Fig. 1.15. Peak-to-peak period Jitter.

As mentioned before, many parts of the power management system require a clock signal. In some cases, an external clock signal can be used. When dealing with fully integrated battery-

supplied IoT devices, a clock for power management needs to be generated on-die. Since power efficiency is one of the main quality indicators for any power management system, clock generators must function according to that fact. The tradeoff between power consumption and other parameters must be conducted in practice. When designing the clock generator for a power management system, the power consumption is minimized while keeping other parameters (area, duty cycle, jitter, temperature stability, etc.) within the system requirements [4].

#### Fractional-order elements in power management

In recent decades, fractional-order (FO) systems have emerged in interdisciplinary research as systems of the 21st century capable of representing continuous-time linear systems more efficiently than integer-order (IO) systems [5] [6]. Out of a large variety of applications such as control theory, material theory, diffusion theory, robotics, signal processing, viscoelasticity, etc., FO elements also find their usage in the field of power management. Switching-capacitor DC-DC converter, as an unavoidable part of state-of-the-art power management, has a significant limit of fixed VCR for a given SC Network topology (Table 1.1). Standard switching capacitors are very suitable when input voltage needs to be divided or multiplied by the integer number (VCR= 1, 2, 3, 1/2, 1/3, etc). However, when optimal VCR becomes a fraction that includes non-integer numbers, SC network topology becomes more complicated with an increasing number of switches and capacitors.

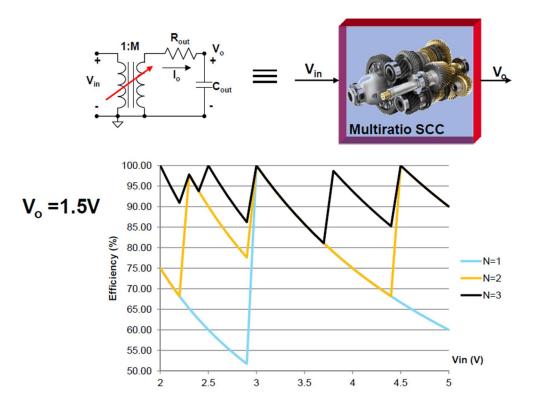

The research focused on conventional IO SC DC-DC converters attempted to solve the problem of fixed VCR by introducing the so-called gearbox of SC Networks, as depicted in Fig 1.16 [3]. This approach means that the number of different SC network cores must be implemented in the design, and it still does not provide a smooth transition between different VCRs. A possible solution to this problem might be to introduce a digitally controlled fractional-order capacitor instead of a standard, integer-order capacitor [7] [8]. That way, the transition between neighboring VCRs can be smoother without significant drops in Efficiency.

Even though FO elements provide an elegant and promising solution to this problem, further research needs to be conducted to investigate their value, especially for fully integrated DC-DC converters. Several main aspects of already existing FO systems need to be improved to make them suitable for DC-DC converters: power consumption, speed, and frequency range. Power consumption is especially critical since the FO capacitor is usually implemented with active components that consume current.

Fig. 1.16. Switching capacitor gearbox.

#### **Prior Art and Motivation**

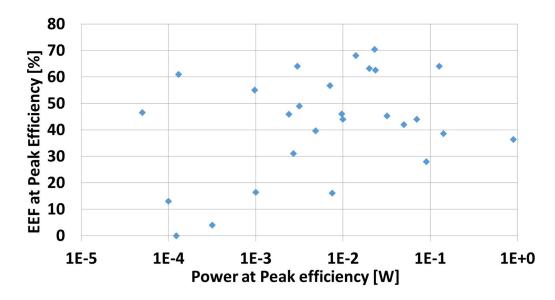

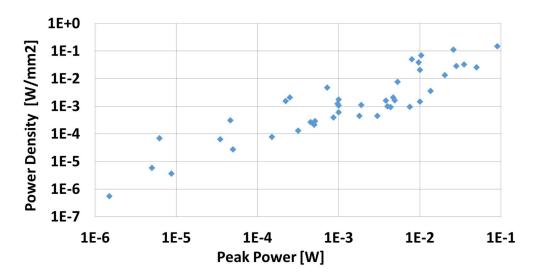

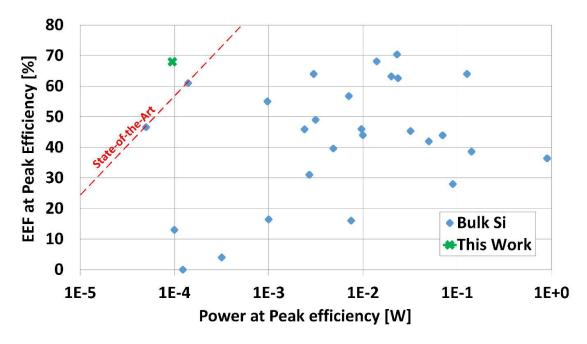

The prior art study concerning integrated power management shows that low-power areas are particularly challenging for achieving high energy efficiency, speed, and power density. The reason for that is a limited amount of available power that needs to be distributed amongst the subcircuits responsible for performing various tasks. A graphical presentation of the prior-art integrated DC-DC converters shows a very limited amount of research papers for sub-mW power. (Fig. 1.13, and Fig 1.14) [9].

Further analysis shows that the presented low-power DC-DC converters have problems with low efficiency, low power density, and slow transient response. They also often require a large decoupling capacitor at the output.

Fig. 1.13. Prior-art integrated switched-capacitor DC-DC converters - EEF.

Fig. 1.14. Prior-art integrated switched-capacitor DC-DC converters - Power Density.

The main focus of this PhD thesis is to improve power management in areas of energy efficiency and speed by introducing novel integrated circuits and techniques. For research purposes, four distinct fully integrated systems were designed, and the results were published in the form of 1 conference paper and 3 journal papers, with 2 additional publications expected in the future:

- (1) D. Zagouri\*, A. Rimer\*, E. Emanović\*, Y. Ninio\*, Y. Slezak, D. Jurišić, A. Fish, and J. Shor, "A Photovoltaic Energy Harvester/Image Sensor Platform With Event Detection Capability in 180 nm," in IEEE Solid-State Circuits Letters, vol. 7, pp. 62-65, 2024. \*Authors with equal contribution [4].

- (2) E. Emanović, J. Shor and D. Jurišić, "An Inverter-Based, Ultra-Low Power, Fully Integrated, Switched-Capacitor DC-DC Buck Converter," ESSCIRC 2021 - IEEE 47th European Solid State Circuits Conference (ESSCIRC), Grenoble, France, 2021, pp. 359-362 [10].

- (3) **E. Emanović**, D. Jurišić, J. Shor, "An Inverter-Based, Ultra-Low Power, Fully Integrated, Switched-Capacitor DC-DC Buck Converter," in IEEE Access [11].

- (4) E. Emanović, M. Vonić, D. Jurišić, C. Psychalinos, "Digitally Controlled Fractional-Order Elements Using OTA-C Structures," Electronics. 2024; 13(11):2066 [12].

- (5) **Expected additional publication:** "Boost DC-DC converter as part of the Image sensing platform" as an extension of the system paper [4].

- (6) Expected additional publication: "Temperature compensated low-power clock generator as part of the Image sensing platform" as an extension of the system paper [4].

Chapter 2 describes a step-down (buck) DC-DC converter fabricated in TSMC 65nm and published as a conference paper [10] with an extended journal version [11]. A boost DC-DC converter fabricated in TSMC 180nm as part of the image-sensing platform published as a journal paper [4] is presented in Chapter 3. A low-power clock generator (as part of the same image-sensing platform [4]) is illustrated in Chapter 4. An additional contribution to the area of fully integrated power management was implemented in the form of a digitally controlled fractional-order capacitor, designed in AMS 350nm, published as a journal paper [12], and described in Chapter 5.

### 2. SWITCHED-CAPACITOR DC-DC BUCK CONVERTER

#### Introduction

Internet-of-Things (IoT) devices at the edge are required to operate at ultra-low average power levels of 10's of  $\mu$ W and lower [13]. To conserve power, IoT chips operate at a very low activity factor in most of the computing circuits. However, always-on circuits, such as wakeup circuits, reference voltages, real-time clocks, and digital circuits controlling them, can be a dominant energy consumer in the system despite the fact they are low-power. The main voltage regulators of the IC active circuits may have very poor efficiency at such light loads. Although a Low-Drop-Out linear regulator (LDO) could sometimes be utilized for such low powers, the main limitation lies in the fact that the LDO's efficiency is limited by the ratio of output and input voltages. Therefore, an efficient on-die DC-to-DC converter is essential to regulate the power of the battery voltage for these low-power domains. In always-on applications, digital domains operate at or near the threshold voltage (V<sub>th</sub>), typically 0.5-0.6V, while analog circuits require higher voltages (1.2-1.8V). Research works on on-die switched capacitor DC-DC converters in the 10-100 $\mu$ W domain are limited [1], [13], [14], [15], [16], [17]. In the low-voltage domain, the speed of the DC-DC converter is crucial because any voltage droop caused by current surges can affect digital speed paths.

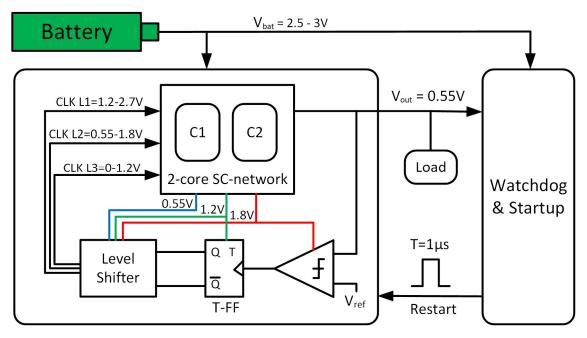

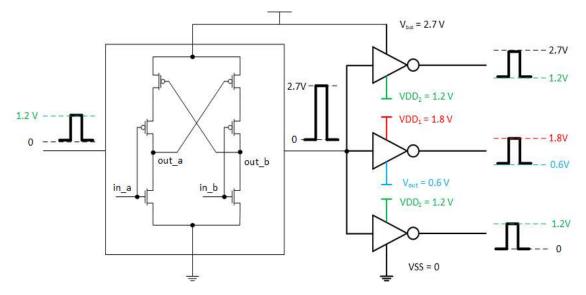

This chapter describes a switched capacitor DC-DC converter for low power always-on domains, and it is an extension of the work reported in [10]. An inverter-based amplifier was used for loop regulation due to its low-power, high-speed nature, which limited droops and overshoots during load transients. Additionally, the fast regulation loop enables the circuit to operate even with an output capacitance as low as 50 pF. The DC-DC converter operates at battery voltage levels,  $V_{bat}$  of 2.5-3 V. The main output voltage ( $V_{out}=0.55V$  nominally) is generated for the digital circuitry, as well as intermediate voltage levels ( $VDD_1=1.8V$  and  $VDD_2=1.2V$ ), which can be utilized for analog circuits. Combining several analog techniques (counter-phase cores, floating well circuit, and multi-level clocking) with a novel way of output voltage detection (inverter-based comparator) the proposed topology was able to achieve contribution in terms of EEF and Power Density. Additionally, a very fast transient response was accomplished.

#### Architecture and Circuit Design

#### Control Loop and Clock Generation

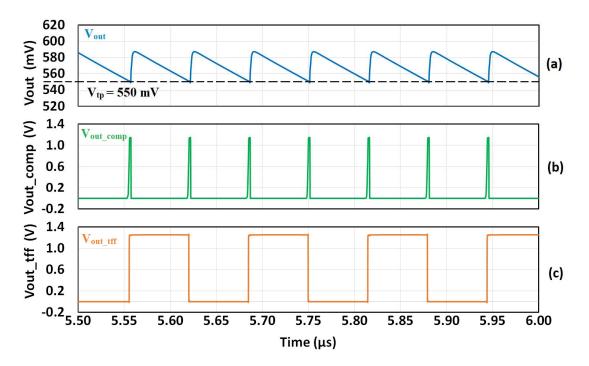

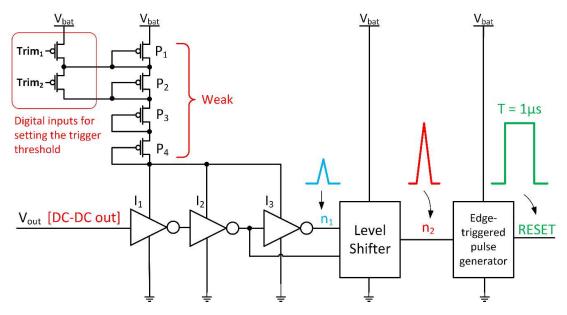

Figure 2.1 illustrates a simplified block diagram of the DC-DC converter. Vout is monitored by

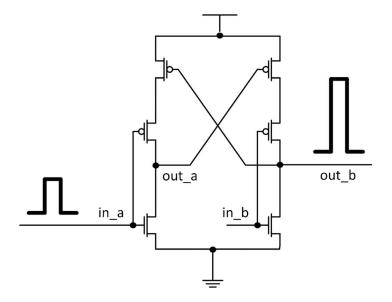

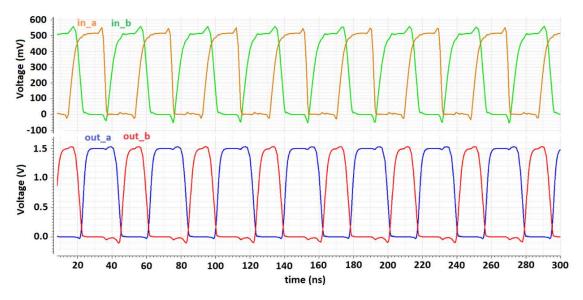

an inverter-based comparator, which generates a rising edge when it detects that  $V_{out} < V_{ref}$ . Simulated waveforms of  $V_{out}$  and comparator output (V<sub>1</sub>) are shown in Fig. 2.2(a) and Fig. 2.2(b) respectively, where output current (I<sub>out</sub>) is set to 50µA. This rising edge changes the output state of the T-flip-flop (V<sub>2</sub>), as shown in Fig 2.2(c), and the clock signal is level-shifted and fed into the dual-core Switched-Capacitor (SC) network (Vtp represents the trip point of the inverter used as a comparator). The SC network operates using clocks at three different voltage levels (L1, L2, and L3) for switching purposes. When the rising or falling edge of the clock triggers the SC network, a new package of charge is delivered to V<sub>out</sub>, which elevates it above V<sub>ref</sub>, thus resetting the V<sub>1</sub>. A Watchdog circuit is included as a failsafe feature, which could also serve as a startup mechanism and is in standby mode during regular DC-DC operation, consuming only 135 nW. If a malfunction is detected, such as overcurrent, the watchdog kicks in and restarts the whole system. Since the DC-DC converter requires internally generated intermediate voltage levels (1.2 and 1.8 V), the reset signal generates the required voltages as needed.

Fig. 2.1. Block diagram.

Fig. 2.2. Simulated waveforms of the clock generation mechanism at nominal conditions and  $I_{out}$ = 50uA. (a)  $V_{out}$ , (b)  $V_1$ , (c)  $V_2$ .

### Switched-Capacitor Network

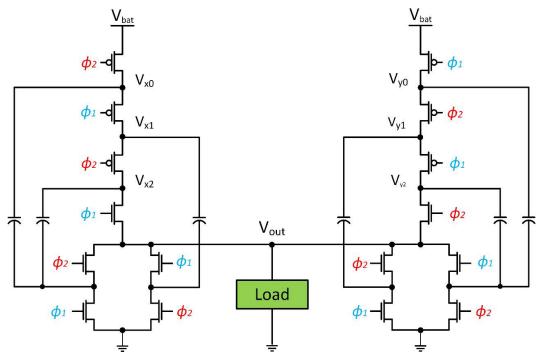

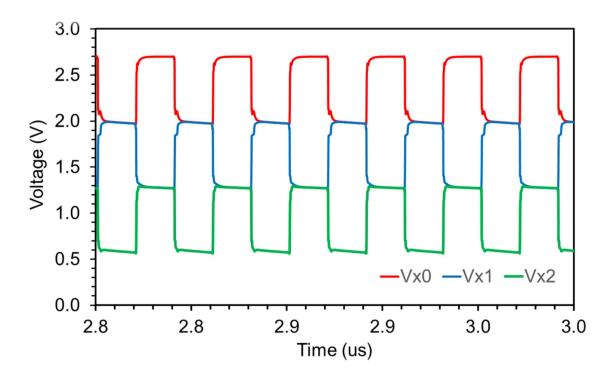

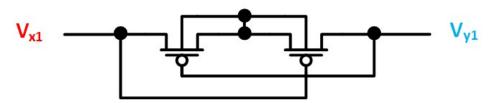

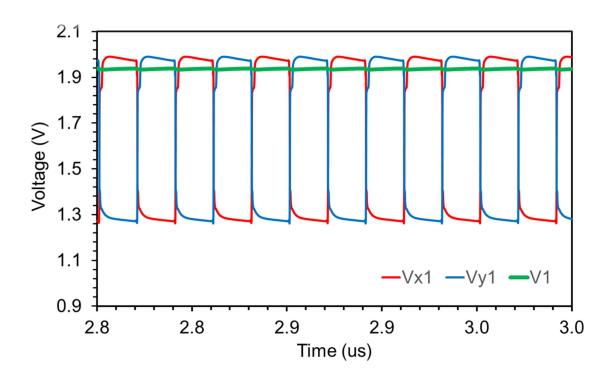

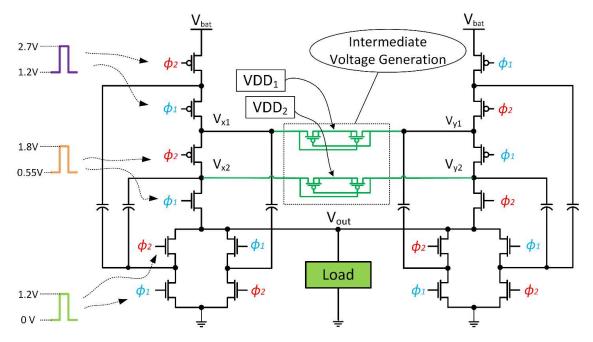

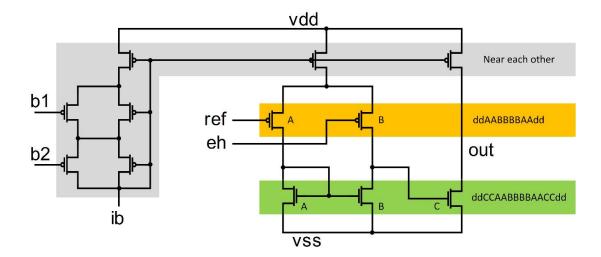

The architecture utilized to achieve the necessary Voltage-Conversion-Ratio (VCR) is a dualcore Ladder-Star [3] (also known as Dickson or Dickson Star [18]), as illustrated in Fig. 2.3. Each core's flying capacitors ( $C_{fly}$ ) comprise three 5pF Metal-Insulator-Metal capacitors (MIMCAP). The two cores operate at opposite clock phases, which enables lower ripple and provides access to intermediate voltage levels. Internal voltages of the one core ( $V_{x0}$ ,  $V_{x1}$ , and  $V_{x2}$ ) are shown in Fig. 2.4. Since the second core's internal voltages are the same in every aspect except the opposite phase, a floating well circuit (Fig. 2.5) can be used for intermediate voltage generation in accordance with the following equations:  $VDD_1 = max(V_{x1}, V_{y1})$ ,  $VDD_2 =$  $max(V_{x2}, V_{y2})$ . The voltage supplies,  $VDD_1$  (~1.8V) and  $VDD_2$  (~1.2V), are produced by providing the opposite-phase internal voltages ( $V_{x1}$ ,  $V_{x2}$ ,  $V_{y1}$ , and  $V_{y2}$ ) to the intermediate voltage generation circuit. A waveform of  $VDD_1$ , generated from  $V_{x1}$  and  $V_{y1}$ , is presented in Fig. 2.6 as an example.  $VDD_2$  is generated in a similar manner. The intermediate voltages, along with the main output voltage ( $V_{out}$ ), are employed for generating three distinct clockvoltage levels that are applied to the corresponding NMOS and PMOS switches (see Fig. 2.7).

Fig. 2.3. Two core Ladder-Star architecture.

Fig. 2.4. Simulated waveforms of one bank at a 130uA load.

The signal  $V_2$  is first level shifted up to the battery voltage level ( $V_{bat} = 2.7V$ ). After that, in order to reduce the charging losses, the clock signal is driven into three buffers which charge

the stages L3, L2, and L1 from 0 to 1.2V, 0.6V to 1.8V, and 1.2V to 2.7V respectively. Thus, each stage in the DC-DC can be driven to exactly the voltage required for the conversion. A detailed illustration of both DC-DC cores including the intermediate voltage generation and clock levels used for each stage is shown in Fig. 2.8. Note that each switch is toggled between its required minimum and maximum voltage levels.

# $V_1 = max(V_{x1}, V_{y1})$

Fig. 2.5. Intermediate voltage generator.

Fig. 2.6. Simulated waveforms of the intermediate voltage generator.

Fig. 2.7. Level shifting concept.

Fig. 2.8. Two core Ladder-Star with intermediate voltages and clock voltage levels.

#### Inverter-based Comparator

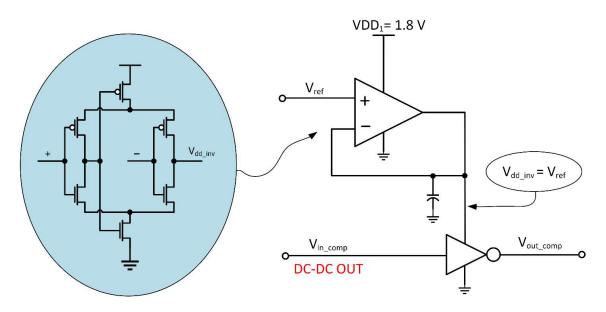

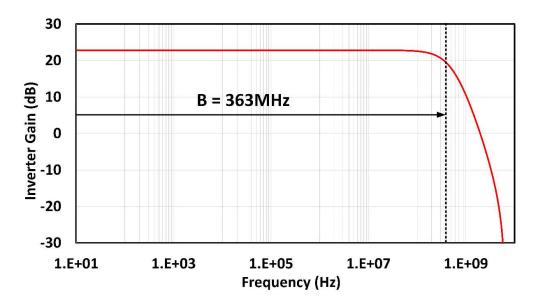

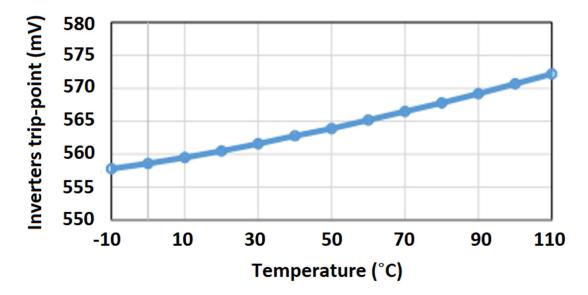

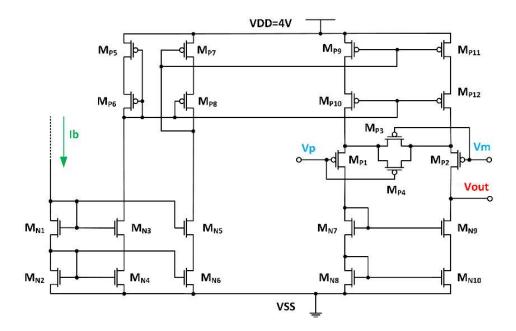

Inverter-based amplifiers are commonly used for their high-speed and low-power properties. However, they are subject to issues such as process-dependence and supply-voltage-dependent trip points. Despite these challenges, an inverter-based amplifier can be implemented as an efficient comparator if its disadvantages can be overcome. To address this, the supply voltage  $(V_{dd_{inv}})$  of the inverter is regulated such that its trip point is always at a fixed voltage level, as depicted in Fig. 2.9a. The voltage reference  $(V_{ref})$  is supplied to the input of the Unity Gain Buffer (UGB), whose output is utilized as the supply voltage for the inverter. Therefore, the trip point of the inverter  $(V_{tp})$  is approximately  $V_{ref}/2$ , based on the ratio of the NMOS and PMOS. The control loop causes  $V_{out}$  to track  $V_{tp}$ , and fine-tuning of  $V_{ref}$  enables digital control of the output voltage. This feature can be accomplished with trimmable subthreshold reference voltage circuits that consume nW or sub-nW level power, such as the 2T based reference in [19], which can operate directly off  $V_{bat}$ . It can be observed that the inverter, when used as an analog circuit, has a bandwidth of 363 MHz (Fig. 2.9b) which enables a very fast response to the transient load changes. The  $V_{tp}$  point is nearly temperature independent, as seen in simulations (Fig. 2.10). Since the UGB does not require very high-speed operation, it can function with very low bias currents (~1.4  $\mu$ A).

Fig. 2.9a. Comparator with UGB.

Fig. 2.9b. Inverter Bandwidth.

Fig. 2.10. Inverter trip-point vs Temperature.

### Watchdog Mechanism

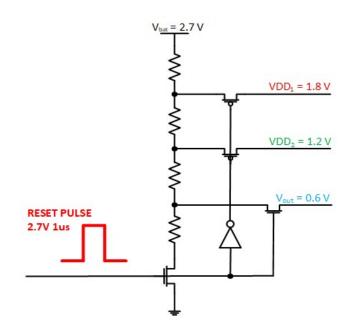

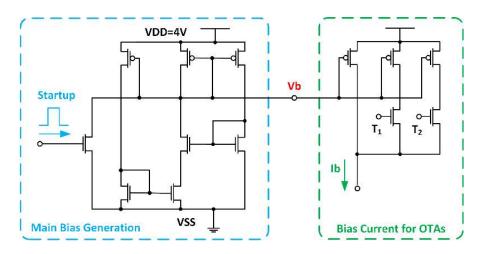

A Watchdog mechanism was designed to reset the DC-DC converter in case of malfunction caused by overvoltage and excessive current, but it could be utilized also as a trigger for the startup mechanism. A startup circuit using a resistor divider between  $V_{bat}$  and VSS, as depicted in Fig. 2.11, is used to initialize VDD<sub>1</sub>, VDD<sub>2</sub>, and  $V_{out}$ , and it could be enabled by the external startup pulse or by the watchdog pulse. The simplicity of the circuit provides a great level of reliability and robustness since the functions of reset and startup are crucial parts of the circuit's

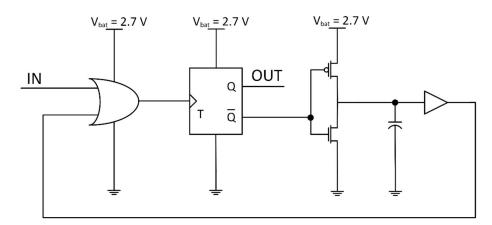

normal operation as well as the fail-safe mechanism. In order to secure the required voltage levels (VDD<sub>1</sub>, VDD<sub>2</sub>, and V<sub>out</sub>), the startup circuit needs to be enabled for roughly 1 $\mu$ s. Thus, the required length of the reset pulse is generated with the Watchdog circuit as illustrated in Fig. 2.12. Inverter I<sub>1</sub> has a lower trip point than V<sub>tp</sub> (Fig. 2.9) and is thus used to detect a situation where V<sub>out</sub> is too low. The supply of I<sub>1</sub> is generated by weak PMOS devices P<sub>1</sub>-P<sub>4</sub> which operate off Vbat. Digital inputs Trim<sub>1</sub> and Trim<sub>2</sub>, determine the voltage level at which a malfunction may be detected. If the DC-DC converter operates normally, V<sub>out</sub> will be above this trip point, and the watchdog will consume minimal power. However, if V<sub>out</sub> drops too low, a rising edge at node n<sub>1</sub> is generated, which is level-shifted to the battery voltage level at node n<sub>2</sub> and fed to the Edge-Triggered-Pulse-Generator (ETPG) that generates a restart pulse (T=1µs). The restart pulse sets the voltage levels at the DC-DC core back to the normal range, resulting in falling edges at nodes n<sub>1</sub> and n<sub>2</sub>. If the malfunction is due to a temporary glitch or current spike, the DC-DC converter will continue to operate normally. The Edge-Triggered-Pulse-Generator is shown in Fig. 2.13.

Fig. 2.11. Startup circuit.

Fig. 2.12. Watchdog circuit.

Figure 2.13. Edge-triggered pulse generator.

#### Internal load setup

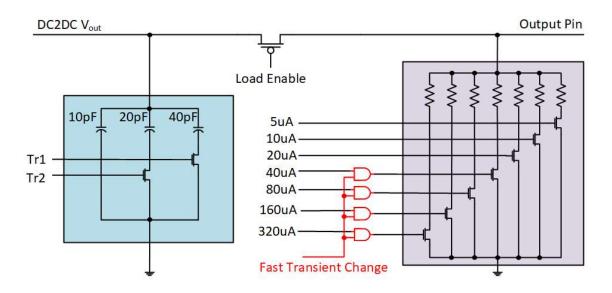

In order to measure the parameters of the DC-DC converter in an environment that is as close as possible to realistic operating circumstances, an internal load circuit (Fig. 2.14) was implemented on silicon next to the DC-DC converter. This setup enabled measurement of circuit operation with load capacitance as low as 50pF (including the oscilloscope probe). It also has a tunable resistor load across the required current range and enables a fast internal current transient. This internal current step could be much quicker than an external step, which would be strongly affected by any parasitic package inductances and capacitors.

Figure 2.14. Internal load setup.

# **Simulated Results**

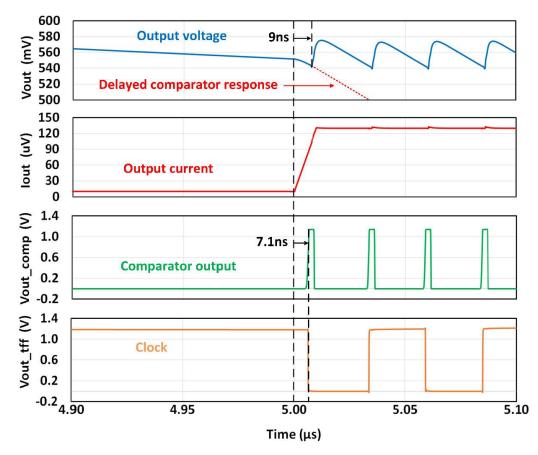

Due to the complexity of the whole system and the limited capabilities of silicon measurements in different corners, the simulation results represent an important aspect for performance analysis. The results of the transient analysis, that simultaneously depict the Vout, Iout, as well as other relevant waveforms, are presented in Fig. 2.15a, Fig. 2.15b, and Fig 2.16. A fast response without voltage droops or overshoots can be observed in cases of fast transient load change (Fig. 15a and Fig. 15b). Figure 15b presents waveforms of signals relevant to the speedy transient response (Vout, Iout, Comparator output, and T-flipflop output) right around the moment of transient load change. It can be observed that the response from the comparator takes only 7.1ns from the load change (due to the inverter's high bandwidth). The pulse from the comparator results in an almost immediate change in the clock frequency which enables output voltage to spike up 9ns after load change, thus, preventing voltage droop or malfunction. A dashed red line presents a slope of Vout in case of delayed response from the comparator.

Fig. 2.15a. Simulated transient load.

Fig. 2.15b. Relevant waves in the moment of transient load change.

Fig. 2.16. Simulated startup and Watchdog kick-in.

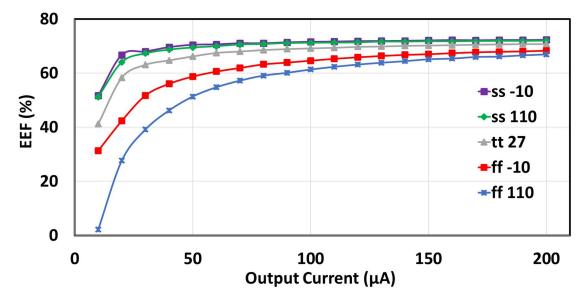

Fig. 2.17. Measured EEF vs  $I_{out}$  at  $V_{in} = 2.7V$ , nominal and extreme (ss -10 ss 110, ff -10, ff 110)

Figure 2.17 shows simulated extreme cases of the EEF dependence on the  $I_{out}$  (process corners combined with extreme temperatures). As expected, a certain drop of efficiency goes with the

fast corner due to the leaky MOSFET switches. It can be observed that even for the worst-case scenario (ff, T=110 °C), the DC-DC converter can be efficiently utilized over the entire operating range as indicated by the positive EEF.

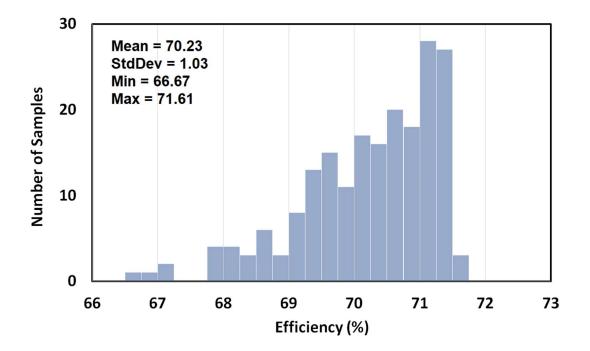

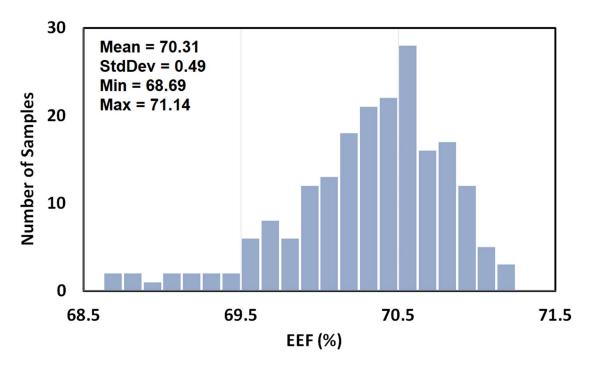

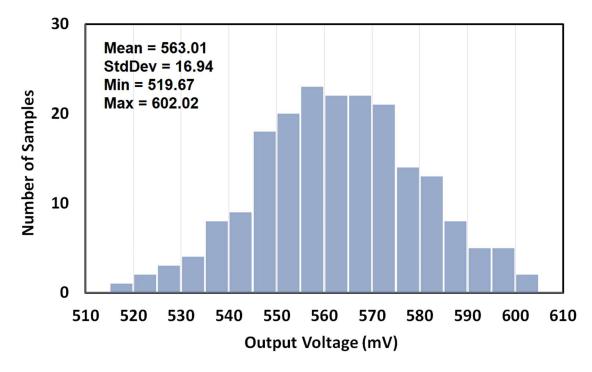

Figures 2.18-2.20 show Monte Carlo variations (process and mismatch) on Efficiency, EEF, and  $V_{out}$  for nominal circumstances and  $I_{out}$ =160µA. Both Efficiency and EEF have very low dispersion with standard deviations equaling 1.03% and 0.49% respectively. Even though  $V_{out}$  shows a slightly larger standard deviation of 16.94 mV, it does not represent the problem since it can be canceled by the trimmable  $V_{ref}$ .

Figure 2.18. Monte Carlo Efficiency at  $I_{out} = 160 \mu A$ , 200 samples.

Fig. 2.19. Monte Carlo EEF at  $I_{out} = 160 \mu A$ , 200 samples.

Fig. 2.20. Monte Carlo  $V_{out}$  at  $I_{out} = 160 \mu A$ , 200 samples.

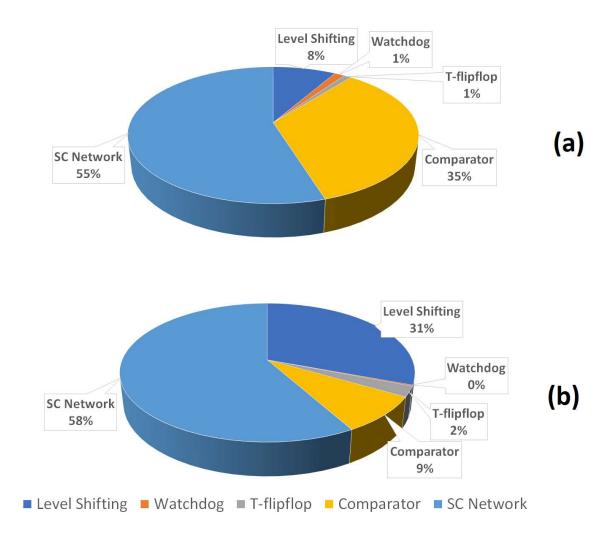

The energy consumption by the individual sub-circuits is analyzed for two different scenarios, minimum power (Fig. 2.21(a)) and maximum power (Fig. 2.21(b)). The results show that the dominant energy consumer for both scenarios is the switched capacitor network, which is

another indicator of the relatively consistent efficiency over the entire operating range. The main difference between minimum and maximum power in energy consumption contribution can be observed in Comparator and Level Shifter. This happens since the Comparator has power consumers that are not dependent on the clock frequency. For low-current converters, the overhead circuits contribute a larger percentage of the total power budget, as compared to high-power converters. This is why the efficiency and EEF are reduced at very low output currents (see Fig 17).

Fig. 2.21. Simulated sub-circuit energy consumption at  $P_{min}$  (a) and  $P_{max}$  (b).

## **Measured Results**

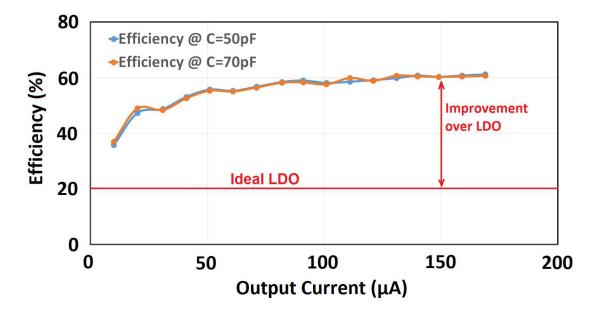

The DC-DC converter was fabricated using TSMC's 65nm technology node. In Fig. 2.22, the measured efficiency as a function of output current (I<sub>out</sub>) is presented for a nominal output

voltage of  $V_{out}=0.55V$ . The efficiency exhibits a peak value of 62% at the maximum  $I_{out}$  and remains close to the peak value over most of the operating range.

Fig. 2.22. Measured Efficiency vs. Iout.

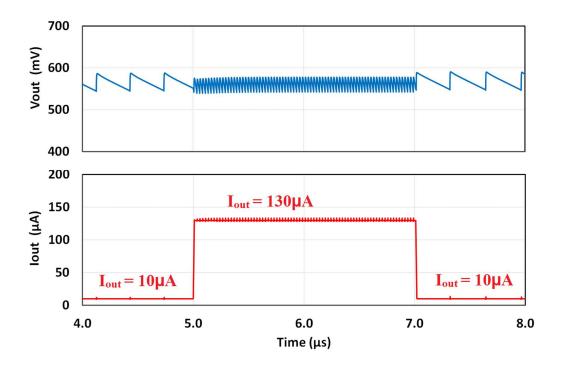

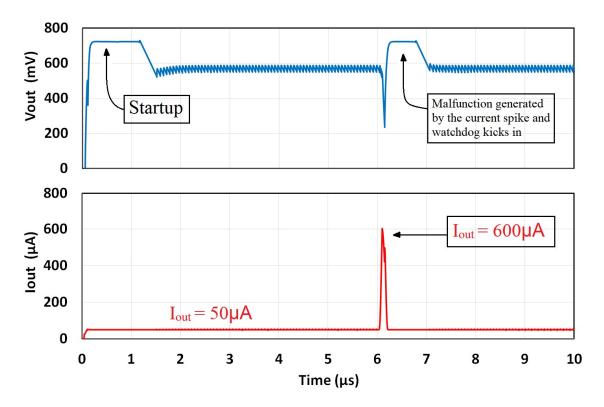

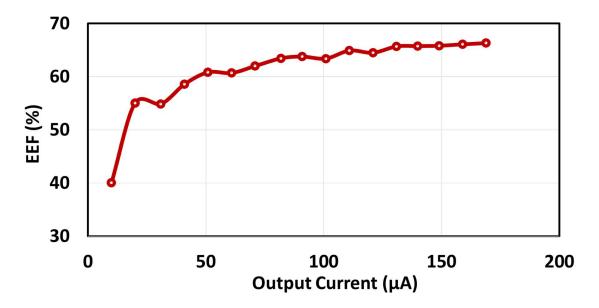

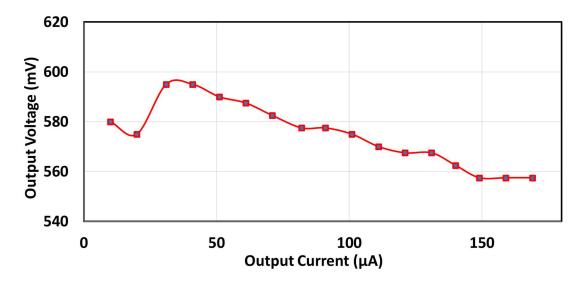

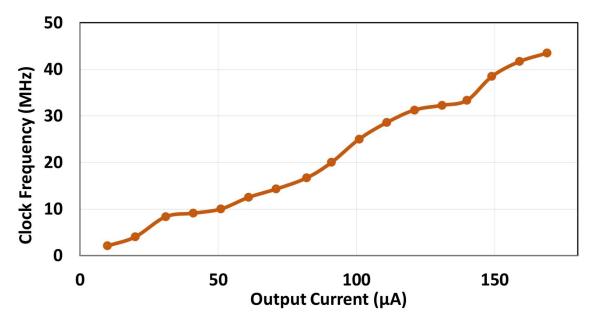

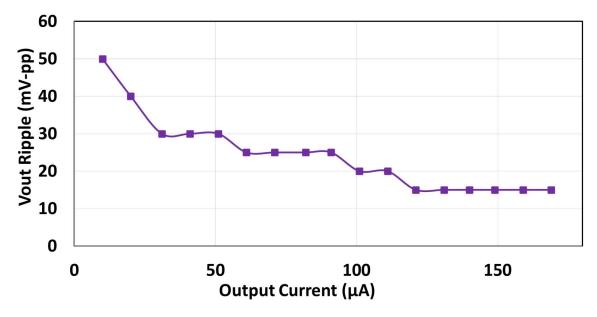

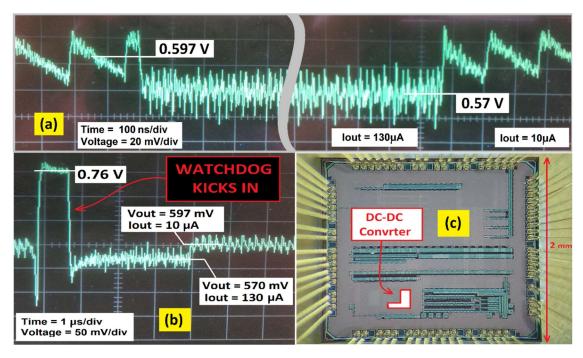

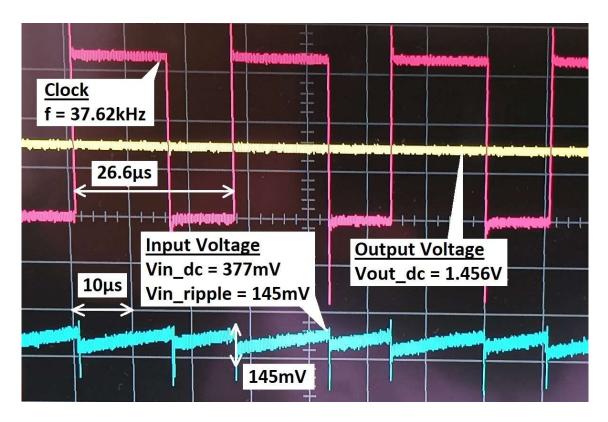

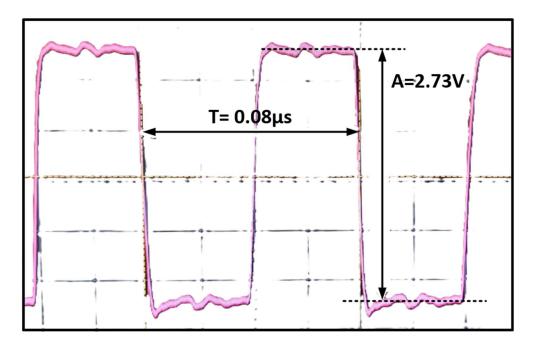

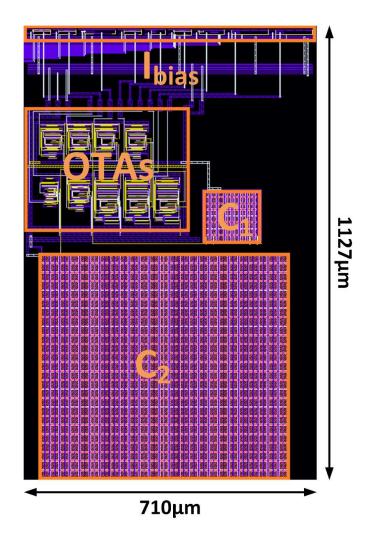

The relationship between the energy efficiency factor (EEF) and I<sub>out</sub> is illustrated in Fig. 2.23, and it also displays good consistency over the range. The nearly linear dependence of the clock frequency on I<sub>out</sub> (Fig. 2.24) enables relatively high efficiency and EEF over the range. The V<sub>out</sub> ripple is plotted against the output current in Fig. 2.25, assuming an output capacitance of 50 pF. Figure 2.26 shows the DC level of V<sub>out</sub> versus I<sub>out</sub>. A DC load line of 37.5 mV is observed over the entire operating range which is mainly associated with the delay of the boosting after the comparator's trip. The ripple difference between light and heavy loads also contributes to the DC load-line to some extent since the regulated value is not a DC component of the V<sub>out</sub> but the minimum V<sub>out</sub>. In Fig. 2.27(a), the transient response of the converter is depicted as the current is suddenly changed from 10uA to 130uA and back to 10uA. Due to the fast speed of the inverter-comparator, no droops or overshoots are observed, despite the small Cout. A DC load-line of 27 mV can be observed here as well. The activation of the watchdog circuit during an overcurrent event is also shown in Fig. 2.27(b). After approximately 1µs of reset time, the DC-DC converter resumes normal operation. Figure 2.27(c) represents the silicon die photo with corresponding dimensions and the DC-DC converter's location.

Fig. 2.23. Measures EEF vs. Iout

Fig. 2.24. Measured Vout vs. Iout.

Fig. 2.25. Measured Clock Frequency vs. Iout.

Fig. 2.26. Measured Vout Ripple vs. Iout.

Fig. 2.27. (a) Measured Load transient - 10uA -> 130uA -> 10uA, (b) Load transient as well as a watchdog operation, (c) Die photo.

# Discussion

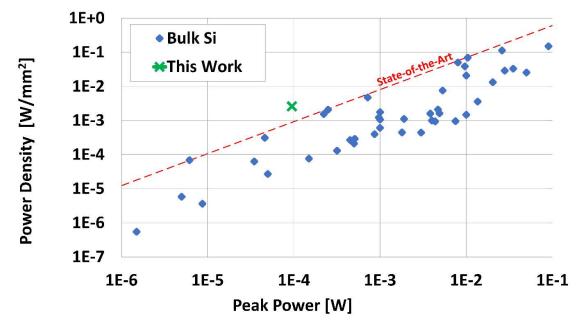

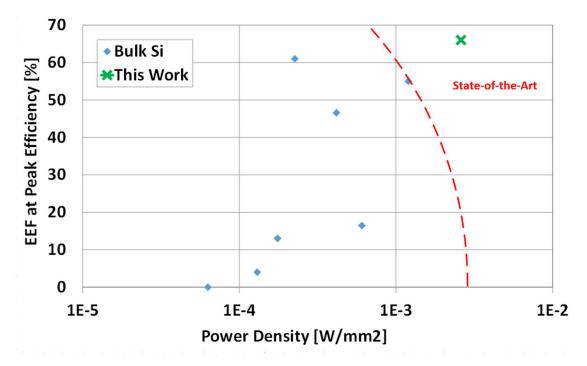

Table 2.1 presents a comparison of the proposed on-die switched capacitor DC-DC converter with previous sub-mW DC-DC converters. Figures 2.28(a,b,c) show a graphical comparison of power density and energy efficiency factor (EEF) for bulk Si switched-capacitor DC-DC converters presented in [4]. The efficiencies and EEFs reported in Table 2.1 were evaluated near or at peak power, where they are typically at the optimal point. It can be observed from [9] that both power density and EEF degrade at very low power, which may be partially attributed to current consumption in the regulation and support circuitry. The proposed DC-DC converter exhibits the best EEF and power density among sub-0.5mW DC-DC converters and is even competitive with converters whose power is two orders of magnitude higher. A graphical presentation of the prior art's power density (Fig. 2.28(b)) clearly indicates that achieving higher power density becomes increasingly harder in low-power domains, which is also the case with other indicators of quality. For this reason, only DC-DC converters in a similar power area should be compared or the parameters should be scaled with power. Figure 2.28(c) illustrates the joined contribution of EEF and Power Density plotted on the graph for sub-mW DC-DC converters. The upper right corner indicates higher performance. It can be observed that the proposed topology scores better than reported prior art DC-DC converters.

|                                     | This Work                                   | [1]                                               | [14]                                                  | [15]                                           | [16]        | [17]                                          |

|-------------------------------------|---------------------------------------------|---------------------------------------------------|-------------------------------------------------------|------------------------------------------------|-------------|-----------------------------------------------|

| Tech Node                           | 65nm                                        | 180nm                                             | 180nm                                                 | 65nm                                           | 130nm       | 180nm                                         |

| Actual VCR (topology VCR)           | 0.2 (1/4)                                   | 0.23 (1/3)                                        | 0.225 (1/4)                                           | 0.83                                           | 0.32 (2/5)  | (1/3)                                         |

| C_fly                               | MIM 6x5pF                                   | -                                                 | -                                                     | MIM 445pF                                      | 800pF       | MIM                                           |

| Power Density (mW/mm <sup>2</sup> ) | 2.56                                        | 1.2                                               | 0.266                                                 | 1.3                                            | 0.055       | 0.038                                         |

| Efficiency                          | 62%                                         | 54%                                               | 58%                                                   | 78%                                            | 65%         | 81%                                           |

| EEF                                 | 66%                                         | 57%                                               | 61%                                                   | -7%                                            | 51%         | 44%                                           |

| Vin                                 | 2.5 – 3 V                                   | 4.2 V                                             | 3.8 – 4.2 V                                           | 1.2 V                                          | 2.7 – 3.3 V | 0.9 – 4 V                                     |

| Vout                                | 0.55/1.2/1.8 V                              | 0.98 V                                            | 0.9/1.2/1.5 V                                         | 1 V                                            | 1.05 V      | 0.6/1.2/3.3 V                                 |

| Max Power (mW)                      | 0.095                                       | 0.97                                              | 0.45                                                  | 0.35                                           | 0.1         | 9.7                                           |

| Area (mm²)                          | 0.037                                       | 0.79                                              | 1.7                                                   | 0.27                                           | 1.82        | 0.25                                          |

| Ripple peak-to-peak                 | 15mV – 50mV                                 | 20 mV                                             | -                                                     | 40 mV                                          | 200 mV      | -                                             |

| C out                               | 50 - 70 pF                                  | 1nF                                               | -                                                     | 1050 pF                                        | -           | 3 nF                                          |

| Droop Response                      | No Droops or<br>Overshoots<br>10μΑ -> 130μΑ | Droop = 230mV<br>Overshoot=200mV<br>10µA -> 100µA | Droop = 200mV<br>Overshoot =<br>200mV<br>10μΑ -> 50μΑ | Droop = 50mV<br>No overshoots<br>10µA -> 250µA | -           | Droop=150mV<br>Overshoot=150mV<br>10nA -> 1µA |

Table 2.1. Comparison to other on-die low power switched capacitor converters.

Fig. 2.28(a). Power Density vs. Peak Power for Bulk Si switched capacitor buck and boost DC-DC converters [9].

Fig. 2.28(b). EEF vs. Power at Peak Efficiency for Bulk Si switched capacitor Buck DC-DC converters [9].

Fig. 2.28(c). Combined contribution of EEF and Power Density (EEF vs Power Density) for sub-mW converters.

# Conclusion

The proposed topology employs a supply-regulated inverter, which is the foundation of a highly energy-efficient, high-speed comparator. Regulation is achieved by adjusting a reference voltage that determines the supply voltage of the inverter. This reference can be operated directly from  $V_{bat}$ , as it is assumed to consume nW-level power, similar to other adjustable references available in the literature [19]. Despite being low power, the inverter enables a fast response, allowing the proposed DC-DC converter to exhibit the best transient recovery among the circuits in Table 2.1, despite the small load capacitor. This prevents voltage droops that could result in timing failures. As the DC-DC converter is self-clocked, the efficiency and EEF remain relatively stable over most of the operating range. The main output voltage of 0.55V is suitable for always-on digital domains operating at near-Vth. Additionally, voltage domains of 1.2V and 1.8V are available for analog circuits, and the DC-DC converter uses internally generated voltages to power its own circuits. The State-of-the-Art performance in terms of efficiency, speed, and power density of the proposed DC-DC converter makes it a promising solution for always-on circuits in IoT devices.

# 3. A PHOTOVOLTAIC ENERGY HARVESTER AS PART OF THE IMAGE SENSOR PLATFORM

### Introduction

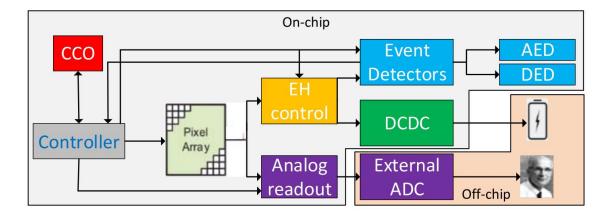

This chapter focuses on a fully integrated energy harvester as part of the image sensor platform [4]. Photodiodes can be utilized for both image sensing and energy harvesting but at opposite polarity. Numerous research works have attempted to create a self-powered imager by flipping the diodes and harvesting them. However, the integration cycle in the image sensing (IS) process is very long, and the chip cannot be harvested while in this mode. In the presented platform, an event detector (ED) function is implemented, whereby the voltage across the photodiode is monitored during harvesting. If there is a significant change in this voltage, then an event is detected, and the chip can take a picture.

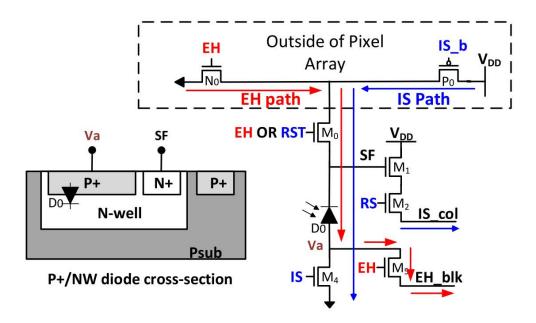

Low-power image sensors are used in a large variety of IoT platforms. There have been several works which used the photodiode of the image sensor as a photovoltaic cell in an energy harvesting (EH) mode, to facilitate self-powered image sensors [20], [21], [22], [23], [24], [25]. These could be very useful in remote "edge" applications where it is inconvenient to switch a battery. However, in an image sensor, the photodiode needs to be reverse biased, while an EH photodiode operates at forward bias. Thus, during the long integration time of the image sensor and its readout (10's to 100's of ms), the diodes cannot extract energy. For self-powered image sensors, this "dead time" would be significantly extended since much lower frequencies are used. For many such applications it is not the static image, which is of interest, but rather significant changes in the background, requiring event detection (ED) during EH. A good example of this would be a remote security fence, where any breach or prowler would need to be detected, but frequent changing of the battery is inconvenient or dangerous. In this system, ED is demonstrated during EH mode, whereby the voltages across sections of the forwardbiased photodiode array are monitored for changes. If a change is detected, then the chip will flip the diodes and take a photo. In this manner, the chip could be harvesting for a much larger percentage of the time, and the power-consuming imager would take a picture only during relatively unusual events. In [25], motion detection and IS were proposed using two different diodes during EH. However, this required a triple-well process, which is a cost-adder. In this system, the same P+/Nwell photodiode is used for IS, ED, and EH (Fig. 3.1) to utilize a standard (nontriple well) CMOS process.

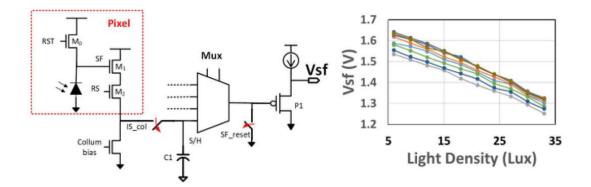

Fig. 3.1. Pixel during EH and IS mode.

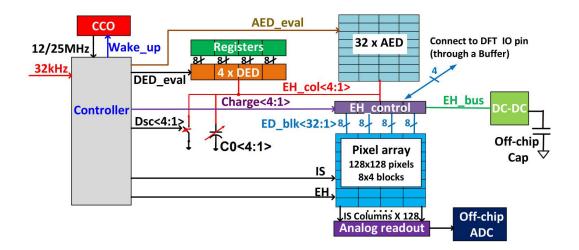

Fig. 3.2. System block diagram.

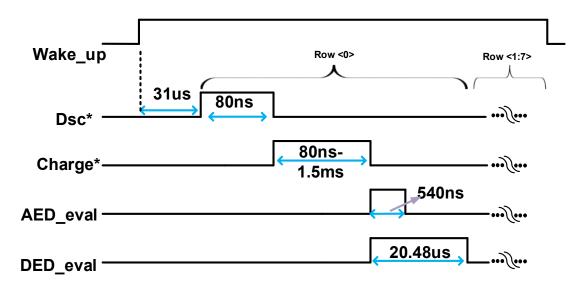

# **System Architecture**

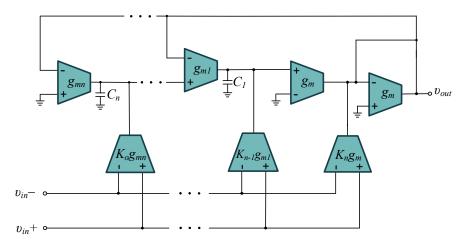

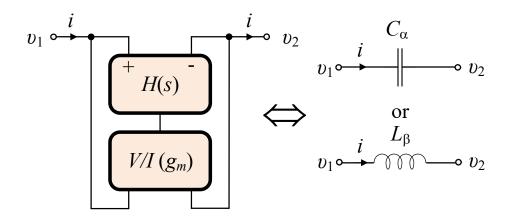

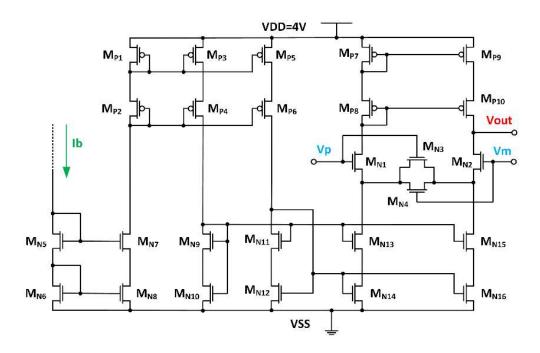

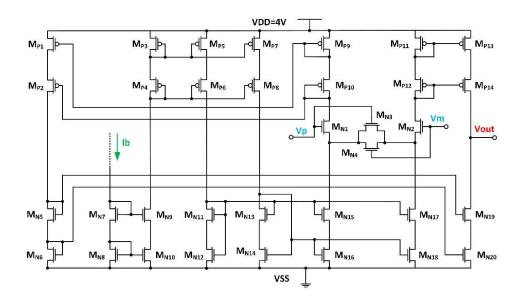

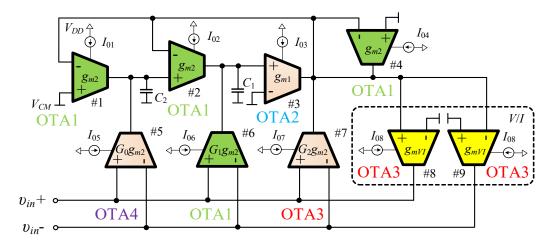

Fig. 3.1 shows the proposed reversible Pixel which was used for this design. Two power gates outside the array (P0 and N0) apply either Vdd or Vss to the drain of M0. During IS, the signal (IS) is asserted, the pixel is reverse biased, and the cathode of the photodiode discharges SF after reset (RST). The source follower, M1, drives the output to the sensing column (IS\_col) for it to be sensed by an ADC for rows selected by the row select (RS) signal. During event