# Relaxation oscillator architectures with delay and offset-voltage compensation

Mikulić, Josip

**Doctoral thesis / Disertacija**

2023

Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Zagreb, Faculty of Electrical Engineering and Computing / Sveučilište u Zagrebu, Fakultet elektrotehnike i računarstva

Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:168:114925

Rights / Prava: In copyright/Zaštićeno autorskim pravom.

Download date / Datum preuzimanja: 2025-03-19

Repository / Repozitorij:

FER Repository - University of Zagreb Faculty of Electrical Engineering and Computing repozitory

### FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Josip Mikulić

# RELAXATION OSCILLATOR ARCHITECTURES WITH DELAY AND OFFSET-VOLTAGE COMPENSATION

**DOCTORAL THESIS**

### FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

Josip Mikulić

# RELAXATION OSCILLATOR ARCHITECTURES WITH DELAY AND OFFSET-VOLTAGE COMPENSATION

**DOCTORAL THESIS**

Supervisor: Professor Adrijan Barić, PhD

### FAKULTET ELEKTROTEHNIKE I RAČUNARSTVA

Josip Mikulić

### ARHITEKTURE RELAKSACIJSKOGA OSCILATORA S KOMPENZACIJOM KAŠNJENJA I NAPONA POMAKA

**DOKTORSKI RAD**

Mentor: prof. dr. sc. Adrijan Barić

Zagreb, 2023.

This doctoral thesis was completed at the University of Zagreb, Faculty of Electrical Engineering and Computing, Department of Electronics, Microelectronics, Computer and Intelligent Systems.

| Supervisor: Professor Adrijan Barić, PhI | ) |

|------------------------------------------|---|

| This doctoral thesis contains 181 pages. |   |

|                                          |   |

Doctoral thesis No.: \_\_\_\_\_

### **About the Supervisor**

Adrijan Barić was born in Zagreb in 1958. He received the Dipl. Ing. degree in 1982 and the M.Sc. degree in 1985 from the University of Zagreb (UniZag), Faculty of Electrical Engineering and Computing (FER), Croatia. He received the PhD degree in 1995 from the Dublin City University, Ireland. He has been employed by FER since 1984. He was a visiting researcher at the Rutherford Appleton Laboratory, England, and at the Ghent University, Belgium. He was promoted to Full professor in 2013. He was a principal investigator of two projects funded by the Ministry of Science, Education and Sports of Croatia, one BICRO project, and he coordinated the FER research team in one EU FP6 project, one EU FP7 project, and several bilateral and multilateral projects with European companies and universities. He presently coordinates the project "Sensor Fusion" funded by ams-OSRAM AG, Austria, and the project "Fast switching converters based on GaN devices and resonant architectures" funded by the Croatian Science Foundation. He published over 100 papers in scientific journals and scientific conference proceedings in the area of integrated circuits and electromagnetic compatibility. He was the President of the Committee for Research, Development and Technology of the UniZag from 2008 to 2011 and the President of the Council of Technical Faculties of the UniZag from 2013 to 2017. He was a General Chair or Co-Chair of two IEEE conferences, the Finance Chair of one IEEE conference, and the Technical Programme Chair of the IEEE conference EMC Compo 2011. He is a member of IEEE, HD MIPRO, KoREMA, and AMAC-FER societies. In 2015, he received the Gold Plaque "Josip Lončar" from FER.

### O mentoru

Adrijan Barić rođen je u Zagrebu 1958. Diplomirao je 1982. i magistrirao 1985. na Fakultetu elektrotehnike i računarstva (FER) Sveučilišta u Zagrebu (SuZ). Doktorirao je 1995. na Dublin City University, Irska. Na FER-u radi od 1984. Bio je gostujući istraživač na Rutherford Appleton Laboratory, Engleska te na Ghent University, Belgija. Za redovitog profesora u trajnom zvanju izabran je 2013. Bio je glavni istraživač na dva projekta MZOS-a, jednom BICRO projektu te je vodio FER-ov tim u jednom EU FP6, jednom EU FP7 projektu te više bilateralnih i multilateralnih projekata s europskim tvrtkama i sveučilištima. Trenutno vodi projekt HRZZ-a "Brzi prekidački pretvornici zasnovani na GaN elementima i rezonantnim arhitekturama" te projekt "Sensor Fusion" s tvrtkom ams-OSRAM AG, Austrija. Objavio je više od 100 radova u znanstvenim časopisima i zbornicima znanstvenih konferencija iz područja integriranih sklopova i elektromagnetske kompatibilnosti. Bio je predsjednik Odbora za istraživanje, razvoj i tehnologiju SuZ-a od 2008. do 2011. te predsjednik Vijeća tehničkog područja SuZ-a od 2013. do 2017. Bio je predsjedatelj ili supredsjedatelj dviju IEEE konferencija, financijski voditelj jedne IEEE konferencije te voditelj programa IEEE konferencije EMC Compo 2011. Član je udruga IEEE, HD MIPRO, KoREMA i AMAC-FER. Godine 2015. primio je FER-ovu Zlatnu plaketu "Josip Lončar".

### **Preface**

This PhD thesis was done within the *High Precision Oscillator* project funded and supported by ams OSRAM in cooperation with the ZEMRIS department at the Faculty of Electrical Engineering and Computing (FER), University of Zagreb. Over the last seven years (2016–2022), the research driven primarily by industry requirements has delivered a number of considerable improvements and contributions in almost all relevant aspects: from modeling and design to manufacturing and test development. The most important scientific contributions were published in several journals, conferences, and patents and eventually compiled within this thesis.

And what a journey it was. Unquestionably, it began long before the PhD project itself, as it was not only the time spent in front of the screen or in the lab that counted, but also the knowledge, belief, and determination at the onset of such an endeavor. Therefore, I must feel grateful to my family, especially my parents and sisters, who had seemingly done something to raise my stubborn side to the full potential that just refuses to give up. I'm also beyond grateful to my wife Antonija – you believed in me even when I didn't. To my dear professor Adrijan, who's been there for my entire academic and professional career – I can't thank you enough. Deepest gratitude to my supervisors who conceived this project and made everything possible: Josi, thank you for the relentless support, and Gregor, thank you for teaching me how to be an engineer. Special thanks must go to my ams OSRAM colleagues, especially the BASE IP office, the CGB group, and the coffee machine - it was, and still is, a pleasure being there. Two Ivans from Austria – thanks for the jokes, and everything else. All the colleagues from the third floor of the FER D-building, the place that always feels like home – thank you. I will also never forget the experience from the student exchange at KU Leuven – it was the year that placed the foundations of my scientific and engineering career. To my irreplaceable friends and colleagues, Marko, Vlatko, Tomo, and Tomislav – thanks for being the inspiration and always having my back. Big thanks to my online gaming party – good game, well played. Also, thank you Ivan for the standard coffee break at nine o'clock. In the end, my deepest gratitude goes to all the others that helped either personally or professionally during this incredible voyage.

> Josip Mikulić May 2023

### **Abstract**

This thesis presents the detailed theoretical analysis, measurements, and performance comparison of several novel relaxation oscillator architectures, having the main focus on the compensation of the propagation delay and offset voltage of the comparator stage. The first architecture introduces two replica comparators that imitate the behavior of the sensing comparators and compensate for their influence on the timing. Next, a further enhancement of the relaxation oscillator core architecture is proposed, comprising a self–compensating chopped comparator pair that entirely cancels the propagation delay and offset voltage of the comparators while being more efficient in power consumption and area. The third architecture introduces additional integrating unit that is used for measurement and compensation of the propagation delay, being compatible with low supply environments and advanced technology nodes. Furthermore, the fourth relaxation oscillator core architecture comprises replica chopped comparator, providing an efficient delay and offset cancellation with minimal influence on power, area, and signal integrity. Eventually, a cost–efficient methodology for a post–manufacturing temperature calibration that significantly reduces the temperature drift of the output frequency is proposed and demonstrated on a manufactured self–sustaining oscillator prototype.

**Key words**: relaxation oscillator, offset voltage, delay cancellation, temperature calibration, process calibration, on–chip design

### Prošireni sažetak

Arhitekture relaksacijskoga oscilatora s kompenzacijom kašnjenja i napona pomaka

Ubrzani rast industrije mobilnih i nosivih uređaja nameće standard minijaturizacije električnog sklopovlja, što u većini slučajeva podrazumijeva potpunu integraciju sustava na silicijske pločice. Dodatni zahtjevi odnose se na što duže trajanje baterijskog napajanja i nisku cijenu proizvodnje. Posljedično, kristalni oscilatori visoke preciznosti rijetko su prihvatljivi u takvim sustavima zbog potrebe za vanjskom komponentom relativno velikih dimenzija. Slično vrijedi i za oscilatore s LC i MEMS rezonatorima koji su kompatibilni s integracijom na silicij, ali nerijetko ih karakterizira visoka potrošnja energije i skupa ugradnja. Nasuprot tome, relaksacijski oscilatori prikladna su rješenja za potpuno integrirane sustave zbog njihove karakteristične male potrošnje, malih dimenzija i jednostavnosti implementacije. Također, pokrivaju jako širok raspon snaga (nW do mW) i frekvencija (Hz do MHz), imaju kratko vrijeme stabilizacije te su primjenjivi pri ekstremnim uvjetima napajanja (< 1 V) i temperatura ( $< -40 \,^{\circ}\text{C}$  i  $> 150 \,^{\circ}\text{C}$ ). Međutim, njihova preciznost uvjetovana je brojnim tehnološkim ograničenjima, od kojih su najznačajniji kašnjenje i napon pomaka komparatora te temperaturna varijacija referentnih elemenata (otpornika i kondenzatora). Poboljšanje preciznosti relaksacijskih oscilatora eliminacijom utjecaja komparatora može se provesti na različite načine što je predočeno rezultatima brojnih znanstvenih istraživanja koja uključuju: korištenje preklopnih komparatora, repliciranje dijelova sklopa, integraciju pogreške frekvencije s povratnom vezom te korištenje digitalnih kompenzacijskih petlji, dok se dodatno poboljšanje nakon izrade čipova postiže temperaturnom kalibracijom sustava i implementacijom naponskog regulatora. U krajnjem slučaju, frekvencija RC relaksacijskih oscilatora određena je vremenskom konstantom referentnog otpornika i kondenzatora čija se temperaturna ovisnost može dodatno ograničiti ugradnjom preciznih elemenata uz povećanu cijenu proizvodnje.

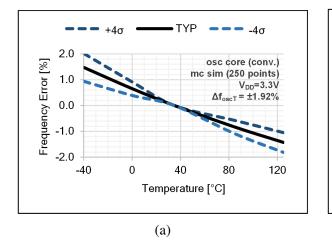

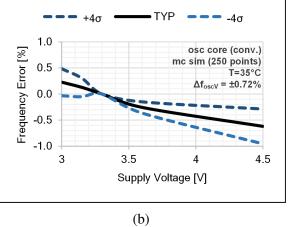

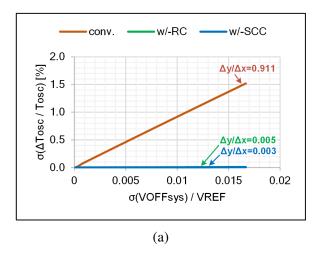

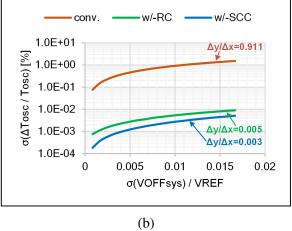

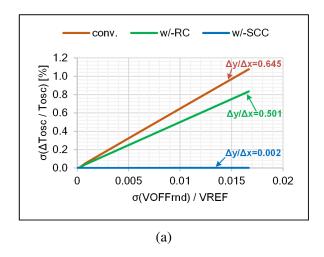

Utjecaj kašnjenja i napona pomaka komparatora predočen je na konvencionalnoj topologiji relaksacijskoga oscilatora, gdje simulacije provedene na prototipu jezgre oscilatora izvedene u 350 nanometarskoj tehnologiji predviđaju relativni pomak frekvencije takta od nekoliko postotaka. Iako je moguće reducirati utjecaj komparatora povećanjem iznosa struje i dimenzija tranzistora, nije ga moguće potpuno otkloniti zbog čega se nameće potreba sklopovske kompenzacije. Prva predložena arhitektura jezgre relaksacijskog oscilatora s replicirajućim komparatorima (eng. *relaxation oscillator core with replica comparators*) kompenzaciju kašnjenja i napona pomaka zasniva na dva dodatna replicirajuća komparatora koja procjenjuju utjecaj očitavajućih komparatora na period izlaznog signala. Mjerenje utjecaja komparatora izvedeno je kombinacijom suprotnog nagiba integracijskog signala i protufaze dvaju ulaza replicirajućih

komparatora, pri čemu se točnost mjerenog signala zasniva na usklađenosti kašnjenja i napona pomaka očitavajućih i replicirajućih komparatora. Nadalje, izmjereni utjecaj se kompenzira povratnom vezom, odnosno privremenim ubrzavanjem integracije referentnog signala u integratoru aktiviranjem dodatnog strujnog izvora.

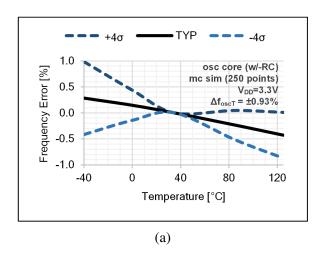

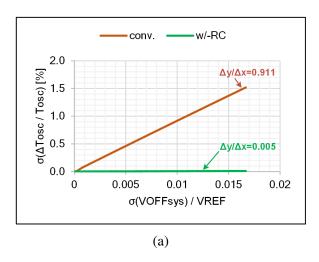

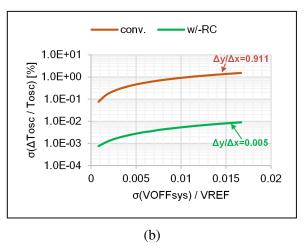

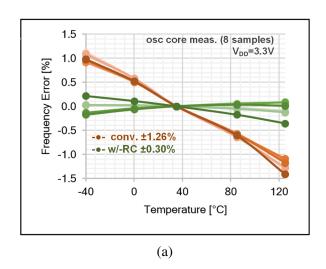

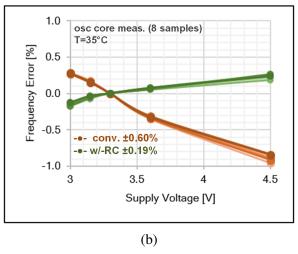

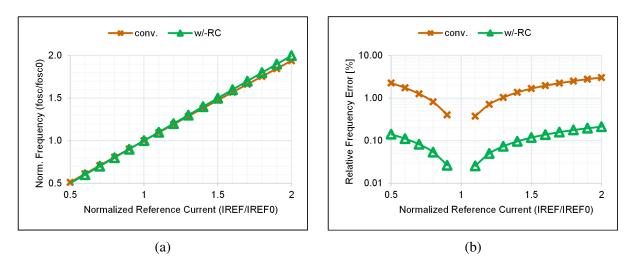

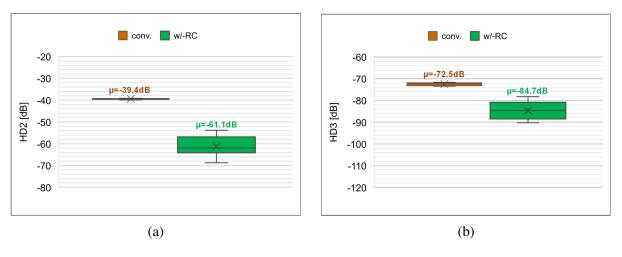

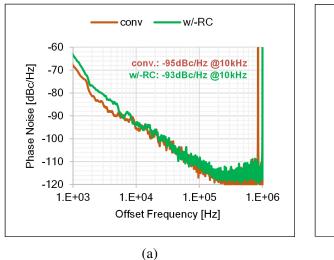

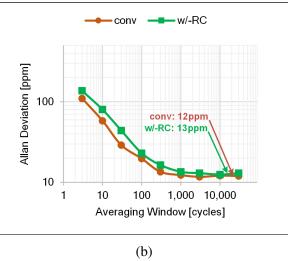

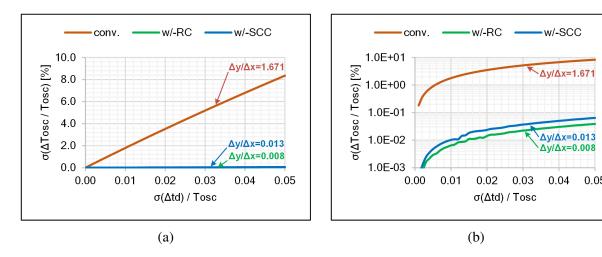

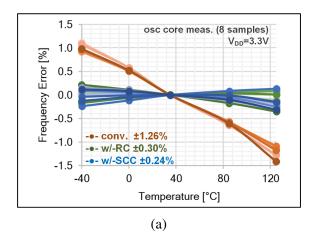

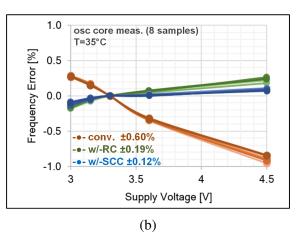

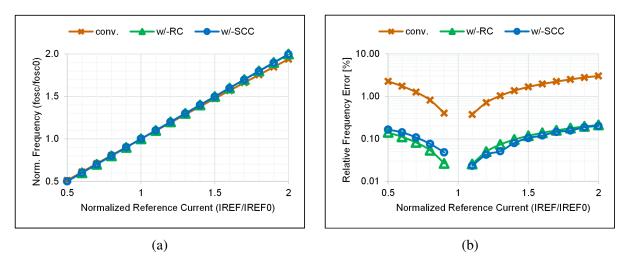

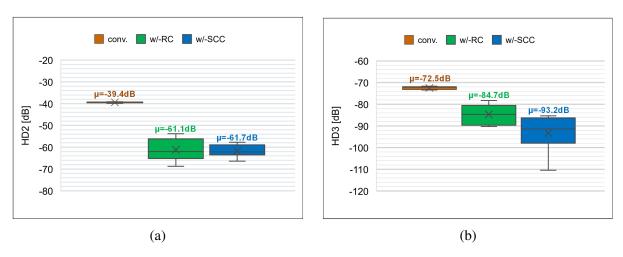

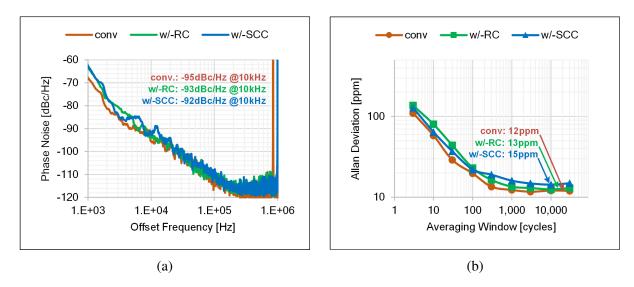

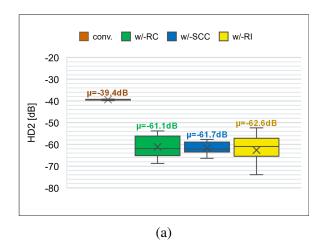

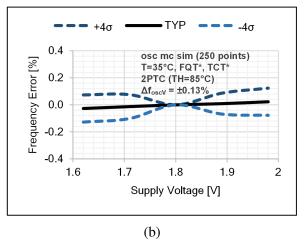

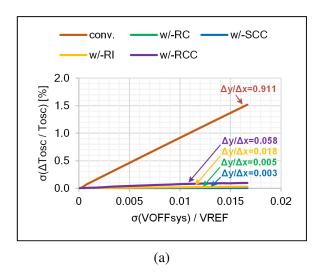

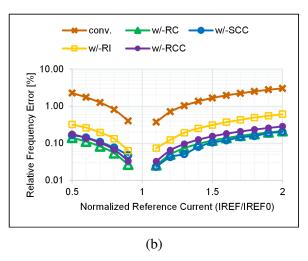

Prototip arhitekture jezgre relaksacijskog oscilatora s replicirajućim komparatorima izrađen je u 350 nanometarskoj tehnologiji s nominalnom frekvencijom takta od 1 MHz. Prilikom mjerenja, referentni napon i referentna struja doveđeni su izvana. Izmjerena je temperaturna ovisnost na osam uzoraka prototipa jezgre  $\pm 0,30$  % u rasponu temperature od -40 °C do 125 °C, što ukazuje na značajno poboljšanje preciznosti frekvencije od oko četiri puta u odnosu na konvencionalnu jezgru, dok je izmjerena ovisnost o naponu napajanja poboljšana oko tri puta te iznosi  $\pm 0,19$  % pri napajanju od 3,0 V do 4,5 V. Dodatno, simulacije osjetljivosti na kašnjenje i sustavni napon pomaka ukazuju na poboljšanje od preko 100 puta, međutim, osjetljivost na napon pomaka uslijed slučajnih efekata nije značajno promijenjena. Predložena arhitektura ima i mnogo bolju linearnost frekvencije prilikom modulacije ulazne referentne struje ( $HD_2 = -61,1$  dB i  $HD_3 = -84,7$  dB, pri  $\Delta f_{osc} = 500$  kHz) te slične parametre šuma ( $\mathcal{L}(f) = -93$  dBc/Hz pri  $f_m = 10$  kHz,  $\sigma_{Tosc} = 230$  ppm te  $\sigma_y = 13$  ppm) u odnosu na konvencionalnu arhitekturu. S druge strane, površina na siliciju (0,04 mm²) i potrošnja (210  $\mu$ W uz  $V_{DD} = 3,3$  V) unaprijeđene jezgre nešto su veće zbog prisustva dvaju dodatnih komparatora unutar sklopa.

Druga unaprijeđena arhitektura jezgre oscilatora sa samokompenzirajućim preklopnim parom komparatora (eng. relaxation oscillator core with self—compensating chopped comparator) donosi daljnja poboljšanja u odnosu na prvu predloženu arhitekturu jezgre s replicirajućim komparatorima. U ovoj arhitekturi, par komparatora implementiran je unutar preklopnog sklopa od kojih je jedan očitavajući komparator, a drugi replicirajući komparator pomoću kojeg se mjeri utjecaj očitavajućeg komparatora na stabilnost frekvencije. Slično kao i u prvoj arhitekturi, mjerenje utjecaja izvedeno je kombinacijom suprotnog nagiba integracijskog signala i protufaze dvaju ulaza replicirajućeg komparatora u odnosu na očitavajući komparator. Dakle, metoda preklapanja komparatora u svakoj poluperiodi izmjenjuje replicirajući i očitavajući komparator, čime se u potpunosti eliminira utjecaj komparatora na frekvenciju signala, uključujući napon pomaka i kašnjenje.

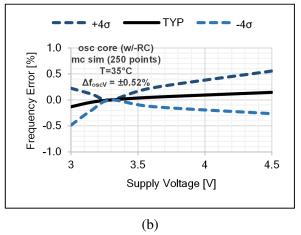

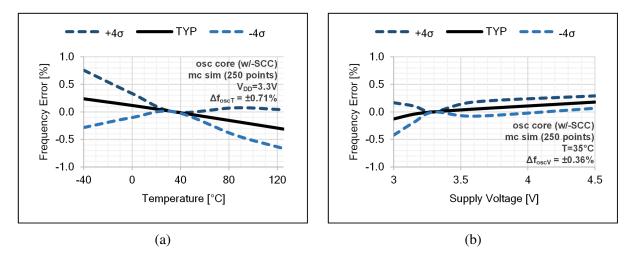

Prototip jezgre relaksacijskog oscilatora sa samokompenzirajućim preklopnim parom komparatora izrađen je u 350 nanometarskoj tehnologiji s nominalnom frekvencijom takta od 1 MHz. Prilikom mjerenja, referentni napon i referentna struja dovedeni su izvana. Mjerenja izvedena na osam testnih uzoraka oscilatora ukazuju na značajno poboljšanje stabilnosti frekvencije

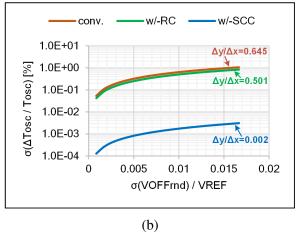

takta, postižući oko pet puta veću preciznost prilikom promjene napona napajanja i temperature u odnosu na konvencionalnu jezgru, pri čemu je varijacija frekvencije jednaka  $\pm 0,24$  % za temperaturni raspon od -40 °C do 125 °C, dok pomak frekvencije u odnosu na promjene napona napajanja iznosi  $\pm 0,12$  % za napone od 3,0 V do 4,5 V. Simulirana osjetljivost na kašnjenje i napon pomaka poboljšani su više od 100 puta, uključujući i slučajne efekte, što ukazuje na to da, za razliku od jezgre s replicirajućim komparatorima, preciznost oscilatora ne ovisi o usklađenosti dvaju komparatora. Linearnost pri modulaciji frekvencije također je dodatno poboljšana, gdje parametri distorzije iznose  $HD_2 = -61,7$  dB i  $HD_3 = -93,2$  dB uz  $\Delta f_{osc} = 500$  kHz, dok su parametri šuma ( $\mathcal{L}(f) = -92$  dBc/Hz pri  $f_m = 10$  kHz,  $\sigma_{Tosc} = 235$  ppm te  $\sigma_y = 15$  ppm) slični kao i kod konvencionalnog oscilatora. Za razliku od prve jezgre, predložena je arhitektura neosjetljiva na neslaganje komparatora te ne zahtijeva znatno veću površinu (0,032 mm²) i potrošnju (160 µW uz  $V_{DD} = 3,3$  V) u odnosu na konvencionalnu jezgru.

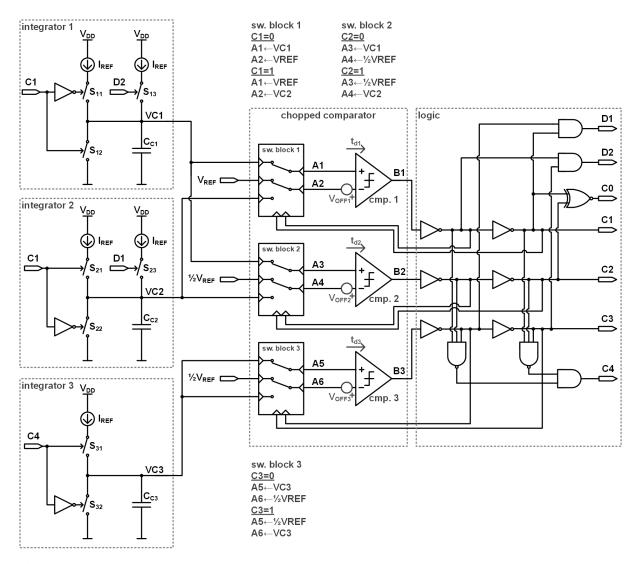

Treća predložena arhitektura jezgre relaksacijskog oscilatora s replicirajućim integratorom (eng. relaxation oscillator core with replica integrator) prilagođena je manjim naponima napajanja (< 1,2 V) i naprednijim tehnološkim procesima (< 100 nm) gdje je izraženiji utjecaj komparatora. Za razliku od prve dvije jezgre oscilatora, strujni izvori unutar integratora u predloženoj arhitekturi imaju identičan smjer što omogućuje neometano funkcioniranje sklopovlja pri niskim naponima napajanja, posebice uz nisku razinu signala referentnog napona. Jezgra predloženog relaksacijskog oscilatora sastoji se od dvaju referentnih integratora čiji se signali uspoređuju s referentnim naponom i polovicom referentnog napona te trećim, replicirajućim integratorom, čiji se signal uspoređuje s polovicom referentnog napona. Nadalje, tri komparatora integracijskih signala jezgre implementirani su s preklapajućim sklopovima. Replicirajući integrator mjeri kašnjenje očitavanja komparatora, što se zasniva na usklađenosti brzine integracije dvaju referentnih integratora i replicirajućeg integratora te međusobnoj usklađenosti kašnjenja triju komparatora. Povratnom se vezom ubrzava integracija referentnog signala aktivirajući dodatni strujni izvor unutar integratora, čime se kompenzira utjecaj kašnjenja komparatora na stabilnost frekvencije. S druge strane, preklopno sklopovlje komparatora osigurava kompenzaciju napona pomaka.

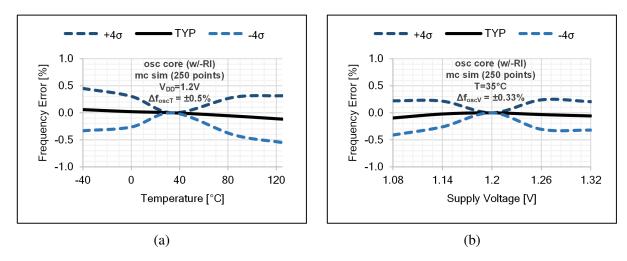

Prototip jezgre relaksacijskog oscilatora s replicirajućim integratorom dizajniran je u 110 nanometarskoj tehnologiji s nominalnom frekvencijom takta od 2 MHz. Simulirana je preciznost prototipa jezgre s replicirajućim integratorom  $\pm 0,50$  % uslijed promjena temperature u rasponu od -40 °C do 125 °C te  $\pm 0,33$  % uslijed promjena napona napajanja u rasponu od 1,08 V do 1,32 V. Potiskivanje kašnjenja (> 20 puta) i napona pomaka komparatora (> 10 puta) te linearnost frekvencije pri modulaciji ( $HD_2 = -62,6$  dB i  $HD_3 = -98,3$  dB pri

$\Delta f_{osc} = 500$  kHz) također su značajno unaprijeđeni u odnosu na konvencionalnu jezgru oscilatora, dok je šum ( $\sigma_{Tosc} = 1100$  ppm) povećan u odnosu na prethodne jezgre zbog izrazito manjeg raspona integracijskog napona. Površina je jezgre oscilatora 0,045 mm², a snaga pri naponu od  $V_{DD} = 1,2$  V iznosi 39,6  $\mu$ W.

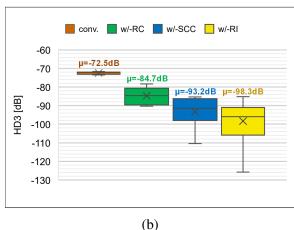

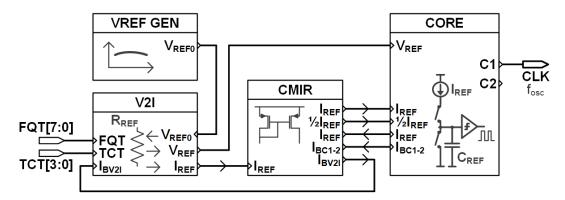

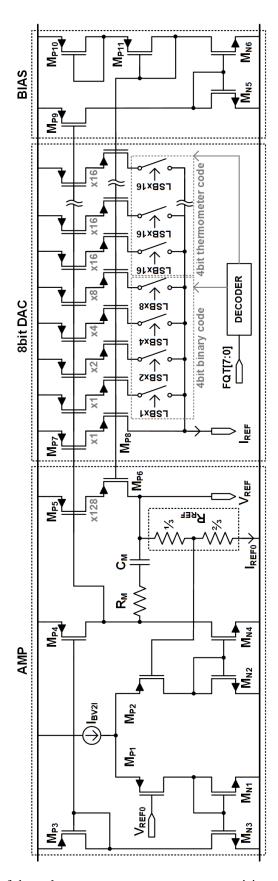

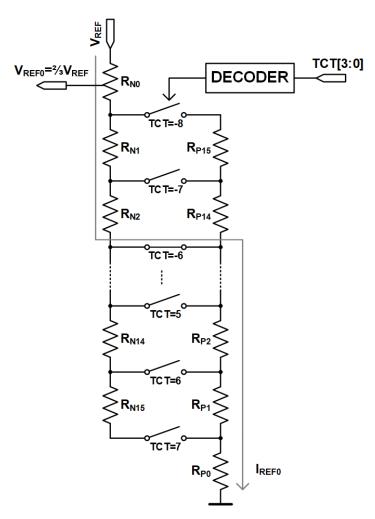

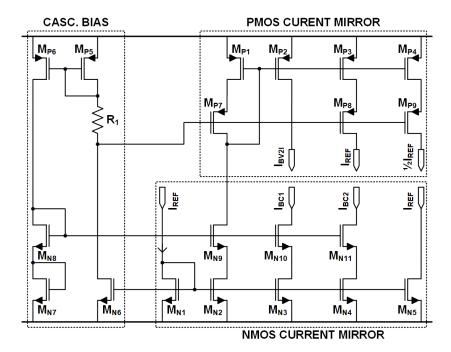

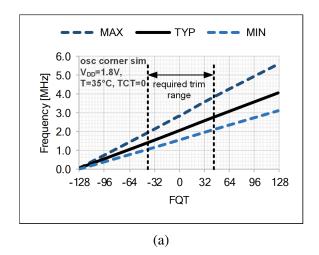

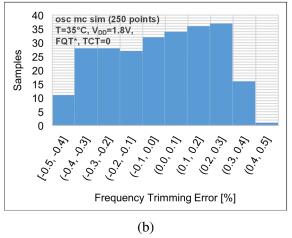

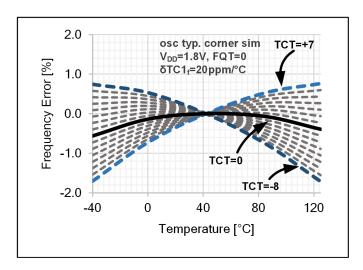

Zatim, predložen je dizajn relaksacijskog oscilatora u 180 nanometarskoj tehnologiji s mogućnošću namještanja nominalne vrijednosti i temperaturnog koeficijenta izlazne frekvencije. Prototip oscilatora sastoji se od referentnih blokova (generatora referentnog napona, naponskostrujnog pretvarača i strujnog zrcala) te jezgre relaksacijskog oscilatora s replicirajućim preklopnim komparatorom (eng. relaxation oscillator core with replica chopped comparator). Generator referentnog napona sastoji se od generatora struje proporcionalne apsolutnoj temperaturi te generatora struje obrnuto proporcionalne apsolutnoj temperaturi, koje su nadalje kombinirane u jednu struju s niskom temperaturnom ovisnošću, čime se preko izlaznog otpora dobiva referentni napon. Naponsko-strujni pretvarač, čiji je ulaz izlazni napon generatora referentnog napona, definira odnos izlaznog referentnog napona i referentne struje pomoću referentnog otpornika. Uz to, unutar naponsko-strujnog pretvarača moguće je dodatno namještati iznos referentne struje pomoću strujnog DA pretvornika, čime je omogućeno posredno podešavanje nominalne vrijednosti frekvencije takta oscilatora. Također, promjenjivi temperaturni koeficijent referentnog otpornika unutar naponsko-strujnog pretvarača izveden je pomoću upravljivih segmenata dvaju otpornika s različitim temperaturnim koeficijentima prvog reda, čime je omogućeno posredno ugađanje temperaturnog koeficijenta frekvencije. Najzad, strujno zrcalo replicira referentnu struju u tri različite struje koje su, uz referentni napon, potrebne za rad jezgre. Posljedično, frekvencija jezgre definirana je referentnim otporom unutar strujno-naponskog pretvornika i referentnim kapacitetom unutar jezgre ( $f_{osc} = 1/2R_{REF}C_{REF}$ ). Oscilator pri radu ne zahtijeva ulazne referentne napone i struje, već samo napajanje i digitalne ulazne kodove za podešavanje nominalne frekvencije i temperaturne karakteristike.

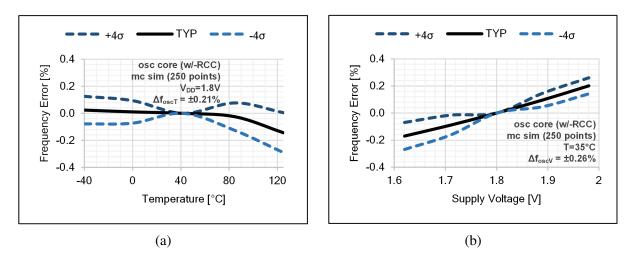

Slično kao i u prethodnim arhitekturama, jezgra s replicirajućim preklopnim komparatorom kompenzira kašnjenje komparatora mjerenjem utjecaja očitavajućeg komparatora koje se zasniva na usklađenosti s replicirajućim komparatorom, dok se napon pomaka kompenzira pomoću preklopnog sklopa. Nominalna je frekvencija prototipa jezgre oscilatora 2 MHz, površina je jednaka  $0.021~\text{mm}^2$ , a snaga pri naponu od  $V_{DD}=1.8~\text{V}$  iznosi  $116.8~\mu\text{W}$ . Simulirana je preciznost frekvencije  $\pm 0.21~\%$  uslijed promjena temperature od -40~°C do 125~°C te  $\pm 0.33~\%$  uslijed promjena napona napajanja od 1.62~V do 1.98~V. Potiskivanje kašnjenja i napona pomaka komparatora veće je od deset puta te su parametri distorzije značajno bolji u odnosu na konvencionalnu jezgru ( $HD_2=-65.9~\text{dB}$  i  $HD_3=-95.9~\text{dB}$  pri  $\Delta f_{osc}=500~\text{kHz}$ ), uz nešto veće podrhtavanje takta ( $\sigma_{Tosc}=320~\text{ppm}$ ).

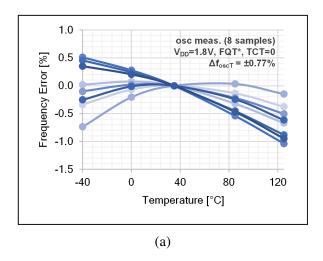

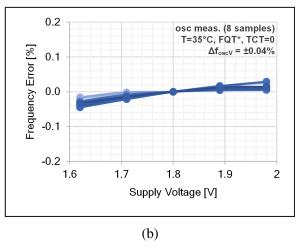

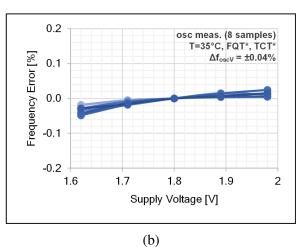

Nadalje, prototip oscilatora s mogućnošu namještanja temperaturnog koeficijenta frekvencije izrađen je u 180 nanometarskoj tehnologiji. Nominalna je frekvencija oscilatora 2 MHz, površina iznosi 0,075 mm², dok je ukupna potrošnja  $185~\mu W$  pri naponu napajanja od 1,8 V. Pomak je frekvencije takta  $\pm 0.77~\%$  uz temperaturne promjene od  $-40~^{\circ}C$  do  $125~^{\circ}C$  te  $\pm 0,04~\%$  uslijed promjena napona napajanja od 1,62~V do 1,98~V, mjereno na osam uzoraka bez temperaturne kalibracije. Ukupno vrijeme pokretanja oscilatora iznosi  $5,5~\mu s$ , a podrhtavanje takta  $\sigma_{Tosc} = 476~ppm$ .

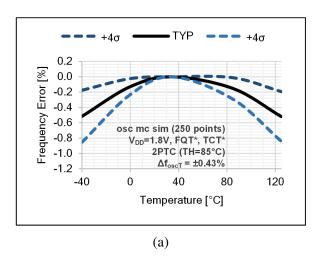

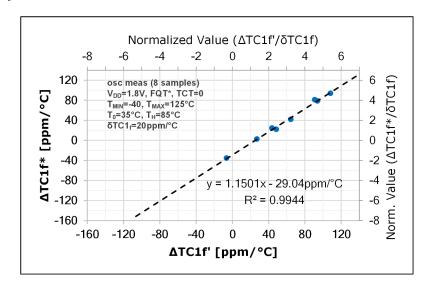

U sustavima koji zahtijevaju veću preciznost frekvencije poželjno je implementirati regulator napona kako bi se gotovo u potpunosti eliminirala ovisnost frekvencije takta o napajanju te provesti temperaturnu kalibraciju oscilatora kako bi se dodatno smanjila varijacija s temperaturnim promjenama. Pri tome, nakon izrade potrebno je izvršiti mjerenja sustava na nekoliko različitih temperatura kako bi se odredila temperaturna karakteristika frekvencije. Međutim, dodatna temperaturna mjerenja uvode značajne sporedne troškove u fazi testiranja, što se posebice odnosi na mjerenja temperatura nižih od sobne temperature ( $T < 27\,^{\circ}$ C). Sukladno tomu, predložena je metoda kalibracije relaksacijskih oscilatora koja se zasniva na mjerenju frekvencije na samo dvije proizvoljne temperature, čime se ograničava porast pripadajućih troškova proizvodnje.

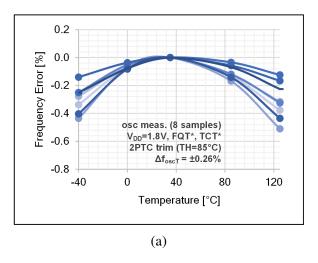

Pošto se temperaturna ovisnost frekvencije kod relaksacijskih oscilatora u pravilu može aproksimirati polinomom drugog reda, za ispravnu karakterizaciju potrebna su minimalno tri mjerenja na različitim temperaturama. Međutim, na primjeru prototipa oscilatora demonstrirano je kako su dovoljne samo dvije točke za približan izračun optimalne vrijednosti podešavanja temperaturnog koeficijenta zbog relativno stabilne vrijednosti koeficijenta drugog reda temperaturne karakteristike. Premda u idealnom slučaju mjerenje pri manjim temperaturnim razlikama ( $\Delta T < 30~^{\circ}$ C) rezultira boljom aproksimacijom, uslijed šuma i ostalih ograničenja mjernog sustava, potrebno je povećati temperaturni raspon mjerenja. Predložena metoda kalibracije temperaturne karakteristike oscilatora s dva temperaturna mjerenja (na  $T=35~^{\circ}$ C i  $T=85~^{\circ}$ C), predočena je na osam testnih uzoraka oscilatora, čime je postignuta oko tri puta veća stabilnost frekvencije ( $\pm 0.26~\%$ ) uslijed promjena temperature.

**Ključne riječi**: relaksacijski oscilator, napon pomaka, kašnjenje, temperaturna kalibracija, kalibracija procesnih parametara, potpuno integrirani sklopovi

### **Contents**

| 1. | Intro | oduction | n                                                                 | 1  |

|----|-------|----------|-------------------------------------------------------------------|----|

|    | 1.1.  | Overvi   | iew                                                               |    |

|    | 1.2.  | Contril  | bution of This Work                                               |    |

|    | 1.3.  | Outline  | e of the Dissertation                                             |    |

| 2. | Rela  | xation ( | Oscillator Core with Replica Comparators                          | 7  |

|    | 2.1.  | Motiva   | ntion                                                             |    |

|    | 2.2.  | Conve    | ntional Relaxation Oscillator Core                                |    |

|    | 2.3.  | Analys   | sis of Comparator Non–Idealities                                  |    |

|    |       | 2.3.1.   | Offset Voltage                                                    |    |

|    |       | 2.3.2.   | Propagation Delay                                                 |    |

|    | 2.4.  | Relaxa   | ation Oscillator Core with Replica Comparators                    |    |

|    |       | 2.4.1.   | Core Architecture                                                 |    |

|    |       | 2.4.2.   | Core Prototype                                                    |    |

|    |       | 2.4.3.   | Reference Circuitry                                               |    |

|    | 2.5.  | Simula   | ation Results                                                     |    |

|    |       | 2.5.1.   | Temperature and Supply Variation                                  |    |

|    |       | 2.5.2.   | Sensitivity to Offset Voltage                                     |    |

|    |       | 2.5.3.   | Sensitivity to Propagation Delay                                  |    |

|    | 2.6.  | Measu    | rement Results                                                    |    |

|    |       | 2.6.1.   | Temperature and Supply Variation                                  |    |

|    |       | 2.6.2.   | Control Linearity                                                 |    |

|    |       | 2.6.3.   | Noise Performance                                                 |    |

|    | 2.7.  | Summa    | ary                                                               |    |

| 3. | Rela  | xation ( | Oscillator Core with Self-Compensating Chopped Comparator 3       | 37 |

|    | 3.1.  | Motiva   | ation                                                             |    |

|    | 3.2.  | Relaxa   | ation Oscillator Core with Self–Compensating Chopped Comparator40 |    |

|    |       | 3.2.1.   | Core Architecture                                                 |    |

|    |      | 3.2.2.   | Core Prototype                                                       |

|----|------|----------|----------------------------------------------------------------------|

|    |      | 3.2.3.   | Reference Circuitry                                                  |

|    | 3.3. | Simula   | ation Results                                                        |

|    |      | 3.3.1.   | Temperature and Supply Variation                                     |

|    |      | 3.3.2.   | Sensitivity to Offset Voltage                                        |

|    |      | 3.3.3.   | Sensitivity to Propagation Delay                                     |

|    | 3.4. | Measu    | rement Results                                                       |

|    |      | 3.4.1.   | Temperature and Supply Variation                                     |

|    |      | 3.4.2.   | Control Linearity                                                    |

|    |      | 3.4.3.   | Noise Performance                                                    |

|    | 3.5. | Summa    | ary                                                                  |

| 4. | Rela | xation ( | Oscillator Core with Replica Integrator                              |

|    | 4.1. | Motiva   | ntion                                                                |

|    | 4.2. | Relaxa   | tion Oscillator Core with Replica Integrator                         |

|    |      | 4.2.1.   | Core Architecture                                                    |

|    |      | 4.2.2.   | Core Prototype                                                       |

|    |      | 4.2.3.   | Reference Circuitry                                                  |

|    | 4.3. | Simula   | ation Results                                                        |

|    |      | 4.3.1.   | Temperature and Supply Variation                                     |

|    |      | 4.3.2.   | Sensitivity to Offset Voltage                                        |

|    |      | 4.3.3.   | Sensitivity to Propagation Delay                                     |

|    |      | 4.3.4.   | Control Linearity                                                    |

|    | 4.4. | Summa    | ary                                                                  |

| 5. | Rela | xation ( | Oscillator Post–Manufacturing Process and Temperature Calibration 75 |

|    | 5.1. | Motiva   | ntion                                                                |

|    | 5.2. | Oscilla  | ntor Architecture                                                    |

|    |      | 5.2.1.   | Voltage Reference Generator                                          |

|    |      | 5.2.2.   | Voltage to Current Converter                                         |

|    |      | 5.2.3.   | Reference Resistor                                                   |

|    |      | 5.2.4.   | Current Mirror                                                       |

|    |      | 5.2.5.   | Core Architecture                                                    |

|    |      | 5.2.6.   | Oscillator Prototype                                                 |

|    |      | 5.2.7.   | Test Bench                                                           |

|    | 5.3. | Calibra  | ation Method                                                         |

|    |      | 5.3.1.   | Center Frequency Calibration                                         |

|    |      | 5.3.2.   | Temperature Calibration                                              |

|     | 5.4.   | Simula  | tion Results                                      |

|-----|--------|---------|---------------------------------------------------|

|     |        | 5.4.1.  | Temperature and Supply Variation                  |

|     |        | 5.4.2.  | Sensitivity to Offset Voltage                     |

|     |        | 5.4.3.  | Sensitivity to Propagation Delay                  |

|     |        | 5.4.4.  | Control Linearity                                 |

|     | 5.5.   | Measu   | rement Results                                    |

|     |        | 5.5.1.  | Frequency Trimmed Oscillator Performance          |

|     |        | 5.5.2.  | Temperature Trimmed Oscillator Performance        |

|     | 5.6.   | Summa   | ary                                               |

| 6.  | Conc   | clusion |                                                   |

| •   |        |         | ew of Proposed Core Architectures                 |

|     | 6.2.   |         | urison of Published RC Oscillators                |

|     | 6.3.   | -       | mes of the Dissertation                           |

|     | Ann    | andiv   | Analysis of Compositor Non-Idealities             |

| Α.  |        |         | Analysis of Comparator Non-Idealities             |

|     | A.1.   |         | Systematic Offset Voltage                         |

|     |        |         | Random Offset Voltage                             |

|     | Λ 2    |         | gation Delay                                      |

|     | 11.2.  |         | Differential Pair in Strong Inversion             |

|     |        |         | Differential Pair in Weak Inversion               |

|     |        |         |                                                   |

| B.  |        |         | Sensitivity Analysis                              |

|     | B.1.   | Sensiti | vity to Offset Voltage                            |

|     |        |         | Conventional Core                                 |

|     |        |         | Core with Replica Comparators (w/–RC)             |

|     |        |         | Other Cores (w/–SCC, w/–RI, and w/–RCC)           |

|     | B.2.   |         | vity to Propagation Delay                         |

|     |        |         | Conventional Core                                 |

|     |        |         | Core with Replica Comparators (w/–RC)             |

|     |        | B.2.3.  | Other Cores (w/–SCC, w/–RI, and w/–RCC)           |

| C.  | App    | endix – | <b>Analysis of Temperature Calibration Method</b> |

|     | C.1.   | Tempe   | rature Dependency of the Output Frequency         |

|     | C.2.   | Three-  | Point Temperature Calibration                     |

|     | C.3.   | Two-P   | Point Temperature Calibration                     |

| Bib | oliogr | aphy .  |                                                   |

| List of Symbols       | <br> | <br> | • |      | • | <br>• | • | • |   | <br>• |  |  | • |   | • |   | • | • | • | • | <br>• | 165 |

|-----------------------|------|------|---|------|---|-------|---|---|---|-------|--|--|---|---|---|---|---|---|---|---|-------|-----|

| List of Abbreviations |      | <br> |   |      |   | <br>• |   |   | • | <br>• |  |  |   |   |   |   |   |   |   |   |       | 171 |

| List of Figures       | <br> | <br> |   |      |   | <br>• |   |   |   | <br>• |  |  |   |   | • |   |   | • |   | • | <br>• | 173 |

| List of Tables        | <br> | <br> |   |      |   | <br>• |   |   |   | <br>• |  |  |   |   |   |   |   |   |   |   | <br>• | 177 |

| Biography             | <br> | <br> |   | <br> |   | <br>• |   |   | • | <br>• |  |  | • | • |   | • |   |   |   | • | <br>• | 179 |

| Životopis             | <br> | <br> |   | <br> |   |       |   |   |   |       |  |  |   |   |   |   |   |   |   |   |       | 181 |

## **Chapter 1**

## Introduction

### 1.1 Overview

Over the recent decade, the ever–increasing industry of mobile and wearable devices has developed essential requirements for fully integrated circuits. The targeted electronic products cover a broad application space, including but not limited to wearable devices, internet of things (IoT), wireless sensor networks (WSN), biomedical sensors, implantable biomedical devices, environmental monitoring systems, microcomputers, high–speed interfaces, and radio frequency identification (RFID) [1–30]. In most cases, such systems are intended to provide long battery life and small form–factor while simultaneously having a low manufacturing cost [13, 26, 31]. This became a vital consideration for the clock generation in SoCs (Systems–on–Chip), where precise crystal–based oscillators are no longer feasible since they feature a bulky external crystal resonator component [9–12, 24–28]. Moreover, the use of silicon–based high–performance time references, specifically LC [32, 33] and MEMS [34–36] resonators, remains limited due to their high power consumption, increased cost, and complexity of implementation [1, 9].

Accordingly, relaxation oscillators [1–24, 37–46] have become a favorable option for full on-chip devices, achieving an excellent trade-off between the physical area, implementation cost, power consumption, start-up time, and accuracy [14, 47]. They also offer considerable design flexibility, covering an extensive range of operating frequencies, specifically from Hz [37] to tens of MHz [4, 5], and also being scalable to low power and voltage levels [14, 39]. Furthermore, relaxation oscillators have an inherent advantage over ring oscillators [48, 49] in terms of frequency accuracy and start-up time [14, 47], although having a disadvantage in terms of phase noise [18–20, 50]. On the other hand, their accuracy is usually limited to the range of several percentage points by various process-related non-idealities [2, 4, 10]. First, the temperature dependency of the RC reference elements, namely the resistor and capacitor, directly affects the temperature drift of the output frequency. While most CMOS processes feature relatively stable Metal-Insulator-Metal (MIM) capacitors [16, 38], the standard polysilicon and diffusion resistors have significant first-order and second-order temperature coefficients. Here, the systematic influence of the resistor's first-order temperature coefficient can be mitigated using a composite resistor with opposing temperature coefficients [2–4, 10–13, 51], while the second-order temperature coefficient compensation requires advanced trimming techniques, such as demonstrated in [23, 27]. Nevertheless, a temperature coefficient of a composite resistor consisting of two different resistor types is susceptible to process variations [26], especially in high-volume production, which may be resolved using a non-standard precision resistor [8], usually available at an increased cost of processing. Furthermore, significant deterioration of the oscillator accuracy is caused by the propagation delay and offset voltage of the comparator stage [11, 12]. Here, the temperature dependency of the propagation delay is particularly significant since the offset voltage can be compensated by employing a chopped comparator [8, 9], and the eventual supply dependency of the comparator can be minimized using a voltage regulator [8]. On the contrary, the propagation delay of the comparator is strongly temperature dependent [3, 8], where it is required to supply a disproportionate amount of current to the comparator to effectively minimize its influence on the timing [2, 4, 5]. Additionally, in terms of post–manufacturing sources of frequency shift, relaxation RC oscillators may suffer from package stress [27] and aging over lifetime [1–3, 52].

Accordingly, substantial research over the recent years has resulted in several different approaches to overcome the fundamental limitations of the relaxation oscillators. First, implementing the integrated error feedback loop that actively adapts the reference voltage considerably reduces the influence of the comparators at the price of an increased start-up time [1-5], where the accuracy of the output frequency becomes limited primarily by the drift of the reference resistor. Similar is presented in [6, 7], where a digital compensation improves the accuracy of the oscillator. On the other hand, employing a chopper in the comparator stage, as presented in [8, 9], eliminates the comparator's offset voltage and reduces the close-in phase noise, but standalone does not influence the propagation delay, similar to the self-clocked offset cancellation scheme published in [10]. Another approach is presented in [11, 12], where portions of the oscillator circuit are replicated to measure and cancel the undesirable influence of the comparators at the cost of increased area and power consumption. Furthermore, relaxation oscillators with current-mode comparators, published in [13-15], are capable of low voltage operation within the sub-microwatt region with relatively good accuracy. Also, [17] presents a relaxation oscillator capable of high-temperature operation, while works published in [18–22] present techniques for noise reduction in relaxation oscillators. Alternatively, in [24–28], post– manufacturing temperature calibration of RC oscillators significantly improves the performance but imposes significant cost overhead, requiring measurements at temperatures lower than the room temperature, together with complex circuitry that substantially increases circuit area.

This thesis further extends the research of the advanced relaxation oscillator cores, presenting several novel architectures [53–57] that minimize the influence of the comparator stage on the oscillation frequency. The proposed architectures compensate for the propagation delay by measuring the effective delay using replica circuitry, which, combined with chopper architecture, also cancels the offset voltage of the comparator. In order to enable a further enhancement of the oscillator's performance, a cost–efficient temperature calibration method of a self–referenced relaxation oscillator is proposed, compatible with high–volume production. Ultimately, combining the delay and offset–compensated relaxation oscillator architecture with a sample–to–sample process and temperature calibration eliminates the predominant sources of the frequency drift, eventually leading to clock accuracy significantly below the 1% range.

### 1.2 Contribution of This Work

The scientific contributions of the research presented within this thesis are:

- •Architecture of the relaxation oscillator with replica comparators that compensates the delay and systematic offset voltage of the comparators,

- •Architecture of the relaxation oscillator with chopped comparator pair that compensates the delay and offset voltage of the comparators, including the mismatch effects,

- •Architecture of the delay and offset voltage compensated relaxation oscillator with ultra low voltage capability,

- •Methodology for the post–manufacturing trim of the output frequency and its first order temperature coefficient.

### 1.3 Outline of the Dissertation

Chapter 2 presents a detailed analysis of the conventional relaxation oscillator architecture, including the influence of the comparator's non-idealities (propagation delay and offset voltage). Furthermore, an improved relaxation oscillator core architecture with replica comparators is proposed within this chapter, including the simulation and measurement results of the core prototype.

Chapter 3 proposes a further improved relaxation oscillator architecture with self-compensating chopped comparator pair, including the simulation and measurement results of the core prototype.

Chapter 4 presents the improved relaxation oscillator core architecture with replica integrator, suitable for low voltage operation in advanced technology nodes, together with the simulations of the proposed core prototype.

Chapter 5 presents a self–sustaining relaxation oscillator with replica chopped comparator core. Furthermore, a cost–efficient post–manufacturing process and temperature calibration procedure is presented, requiring two–point measurement at arbitrary temperatures. Eventually, the simulation and measurement results of the test–case relaxation oscillator are presented, demonstrating the proposed post–manufacturing process and temperature compensation method.

Chapter 6 presents the overview and comparison of relevant published RC oscillator designs, also including the outcomes of the Dissertation.

## **Chapter 2**

# **Relaxation Oscillator Core with Replica Comparators**

### 2.1 Motivation

Clock references based on RC relaxation oscillators have considerable advantages for wearable and battery—operated electronic applications, such as low power consumption [13–16], fast start—up [11, 14], linear tuning gain [10, 18, 19], and low cost due to compact size and compatibility with monolithic implementation [26]. Nevertheless, conventional relaxation oscillators are featured with several inherent weaknesses that limit their overall accuracy, typically to a range of a few percentage points. First, comparators' delay and offset voltage substantially contribute to the output frequency drift with temperature, supply voltage, and process variations [10, 14, 40]. Likewise, the oscillation frequency necessarily depends on the temperature drift of the reference elements, primarily the reference resistor [8]. Other timing error sources include the propagation delay of the logic blocks [4], switching non–idealities [26], mismatch between the devices [6, 15], aging [2], and packaging stress [27].

Accordingly, this chapter presents a detailed analysis of a conventional relaxation oscillator core, having an emphasis on the propagation delay and offset voltage of the comparator stage. Moreover, an advanced core architecture is proposed within this chapter [53] that compensates for the comparator's non–idealities. The core introduces two additional replica comparators that estimate the timing error and enable the delay and offset cancellation within the core integrator. Eventually, the core prototype is manufactured in 0.35–µm CMOS technology, oscillating with sub–1% accuracy and achieving a considerable performance improvement compared to the conventional core.

### 2.2 Conventional Relaxation Oscillator Core

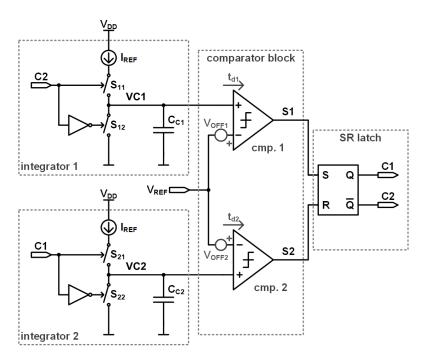

The schematic of the conventional relaxation oscillator core is shown in Fig. 2.1 [3, 5, 41]. The oscillator core consists of two identical integrator blocks, two comparators, and an SR latch. Each integrator block includes a reference current source  $I_{REF}$ , two counter–phase operated switches controlled by the output signals of the SR latch (C1 and C2), and the capacitor having the capacitance value  $C_{REF}$ . The reference current ( $I_{REF}$ ) and reference voltage ( $V_{REF}$ ) are presumed to be generated within the reference generator, not shown in the schematic.

**Figure 2.1:** The schematic of the conventional relaxation oscillator core comprising two integrator blocks, two comparators, and an SR latch.

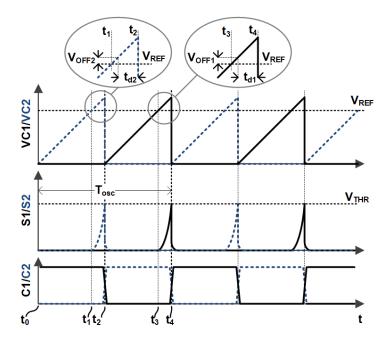

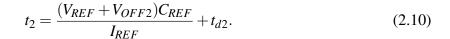

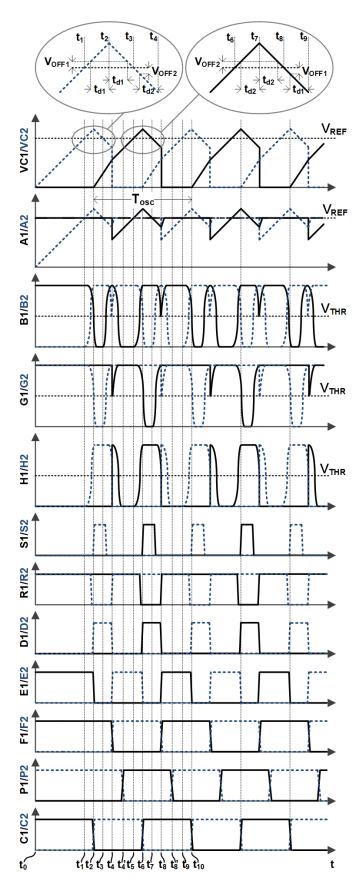

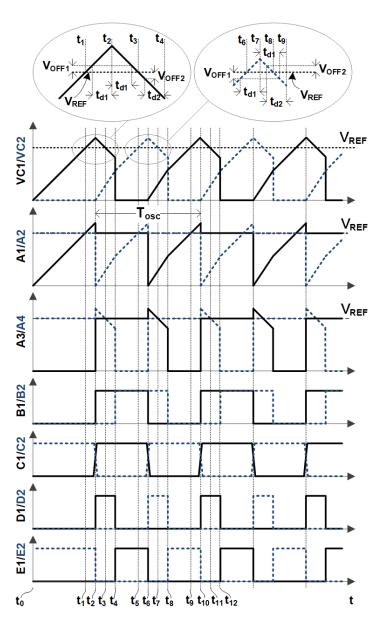

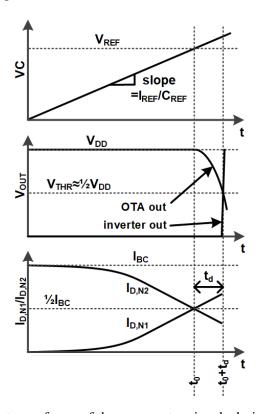

The operation of the conventional relaxation oscillator core in Fig. 2.1 is described with reference to the signal waveforms shown in Fig. 2.2. At an initial time ( $t = t_0$ ) it is presumed that all the signals are set to the initial state by a start-up circuit (not shown in the schematic). Initially, the integration occurs within the second integrator in the time interval from  $t_0$  to  $t_2$ . The integrating signal VC2 rises linearly, having the slope determined by the ratio of the charging current  $I_{REF}$  and the capacitor  $C_{C2}$ , specifically  $\Delta VC2/\Delta t = I_{REF}/C_{REF}$ . Meanwhile, the first integrator block remains idle as the integration node VC1 is shorted to the ground reference node  $V_{SS}$  by the switch  $S_{12}$ . At a subsequent time,  $t = t_1$ , the integrating signal VC2 becomes equal to the reference voltage  $V_{REF}$ . Nevertheless, the output of the second comparator S2 changes state to high at  $t = t_2$  as a result of the non-ideal characteristics of the second comparator, namely the propagation delay  $t_{d2}$  (time required for charging the capacitances on the internal nodes of the comparator up to the digital threshold voltage  $V_{THR}$ ) and the offset voltage  $V_{OFF2}$  (effectively superimposed on the reference voltage  $V_{REF}$ ). Following the positive pulse of the

Figure 2.2: The signal waveforms of the conventional relaxation oscillator core.

second comparator output S2 and change of the control signals C1 and C2, after  $t=t_2$ , the integration starts within the first integrator. The integrating signal VC1 rises linearly, having the slope determined by the ratio of the charging current  $I_{REF}$  and the capacitor  $C_{C1}$ , specifically  $\Delta VC1/\Delta t = I_{REF}/C_{REF}$ . Meanwhile, the second integrator block is idle as the integration node VC2 is shorted to the ground reference node  $V_{SS}$  by the switch  $S_{22}$ . At a subsequent time,  $t=t_3$ , the integrating signal VC1 becomes equal to the reference voltage  $V_{REF}$ . Nevertheless, the output of the first comparator S1 changes state to high at  $t=t_4$  as a result of the non-ideal characteristics of the first comparator, namely the propagation delay  $t_{d1}$  and the offset voltage  $V_{OFF1}$ .

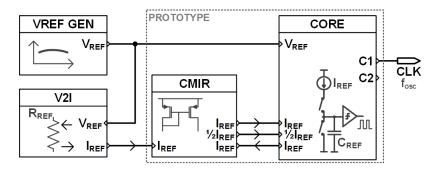

With this, a complete oscillation cycle is described from  $t_0$  to  $t_4$ , where the expression for the oscillation period  $T_{osc}$  is determined by the reference voltage  $V_{REF}$ , comparator offset voltages,  $V_{OFF1}$  and  $V_{OFF2}$ , slope of the integrating signals,  $\Delta VC/\Delta t = I_{REF}/C_{REF}$ , and propagation delay of the comparators,  $t_{d1}$  and  $t_{d2}$  [10, 15]:

$$T_{osc} = \frac{2(V_{REF} + \frac{1}{2}(V_{OFF1} + V_{OFF2}))C_{REF}}{I_{REF}} + t_{d1} + t_{d2}.$$

(2.1)

Consequently, together with the inherent drift of the references ( $V_{REF}$  and  $I_{REF}$ ), the primary sources of the frequency instability are the propagation delay and offset voltage of the comparators [40], along with other minor effects neglected within the analysis (e.g., delay of the logic gates, switching non-idealities, parasitics, and mismatch between integrator blocks). Here, the comparator propagation delay is a parameter strongly dependent on the temperature and supply voltage [11, 13], and also compromises the frequency tuning linearity of the oscillator [18].

The offset voltage, on the other hand, in addition to the drift versus temperature and supply voltage, can also suffer from aging effects [1–3, 52] and deteriorate the clock accuracy over the lifetime. The straightforward reduction of the offset voltage can be achieved by increasing the device area, whereas reducing the propagation delay demands a large amount of additional power [2, 4], as will be discussed in the continuation of this chapter. Accordingly, a more convenient architecture must be considered to maintain a reasonable level of power and area while improving the frequency stability and tuning linearity.

### 2.3 Analysis of Comparator Non-Idealities

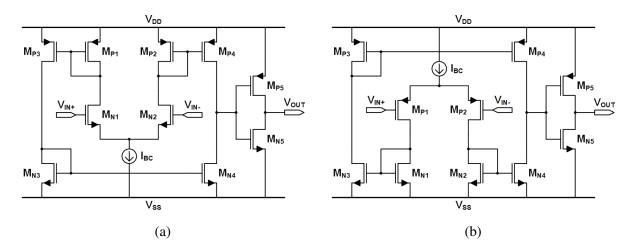

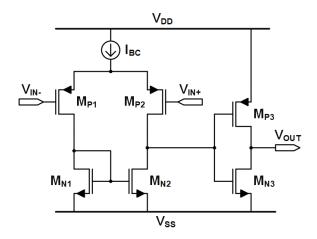

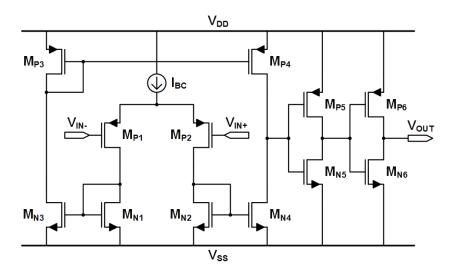

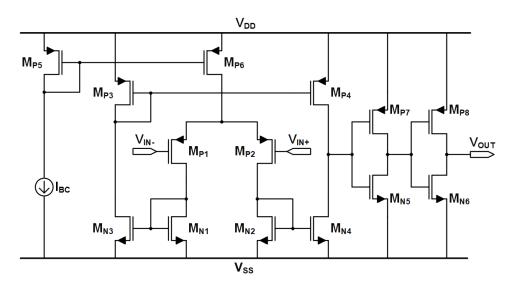

Following the expression for the oscillation period of the conventional relaxation oscillator core (2.1), the dominant influence on the frequency accuracy originates from the non-idealities of two sensing comparators [8], namely the propagation delay  $t_d$  and offset voltage  $V_{OFF}$ . Fig. 2.3 presents two common comparator architectures comprising a symmetrical operational transconductance amplifier – OTA ( $M_{N1-4}$  and  $M_{P1-4}$ ), and the output inverter ( $M_{N5}$  and  $M_{P5}$ ). Using the comparators with a symmetrical load of input transistors, such as the symmetrical OTA, is preferred over simpler comparator topologies since it ensures a smaller systematic offset voltage. The pMOS input pair variant (Fig. 2.3b) is assumed for the simulation of the propagation delay and offset voltage; nevertheless, all derived conclusions are also applicable to the variant with the nMOS input pair. The design parameters for the benchmark comparator designed in 0.35- $\mu$ m technology are shown in Table 2.1.

**Figure 2.3:** The schematic of the comparator (a) with nMOS input pair (b) with pMOS input pair. The comparators comprise a symmetrical OTA and an inverter stage.

| <b>Table 2.1.</b> The design barameters of the deficilitiate combarator with bivios indut b | <b>Table 2.1:</b> | The design paramete | rs of the benchmark co | omparator with pMOS input pa | ir. |

|---------------------------------------------------------------------------------------------|-------------------|---------------------|------------------------|------------------------------|-----|

|---------------------------------------------------------------------------------------------|-------------------|---------------------|------------------------|------------------------------|-----|

| Transistor      | <i>W</i> [μ <b>m</b> ] | $L$ [ $\mu$ m] | Device |

|-----------------|------------------------|----------------|--------|

| $M_{N1-4}[1:4]$ | 0.75                   | 3              | nmos3v |

| $M_{P1-2}[1:4]$ | 1.5                    | 3              | pmos3v |

| $M_{P3-4}[1:4]$ | 1.5                    | 3              | pmos3v |

| $M_{N5}$        | 1                      | 0.35           | nmos3v |

| $M_{P5}$        | 1.6                    | 0.35           | pmos3v |

W and L are single finger dimensions.

#### 2.3.1 Offset Voltage

The offset voltage of a comparator is usually divided into the systematic offset voltage  $V_{OFFsys}$  and random offset voltage  $V_{OFFrnd}$ , specifically

$$V_{OFF} = V_{OFFsys} + V_{OFFrnd}. (2.2)$$

The systematic offset voltage depends exclusively on the variation of the PVT (process, voltage, temperature) parameters rather than the device mismatch [59]. Therefore, all identically designed comparators subjected to the same process and environment conditions would have an equal systematic offset voltage. For the comparator with the nMOS input pair (Fig. 2.3a), the expression for the systematic offset voltage  $V_{OFF,sys}$ , derived in Appendix A.1.1, is

$$V_{OFFsys} = \frac{V_{GS,N3} - \frac{1}{2}V_{DD}}{g_{m,dp}(r_{ds,N4}||r_{ds,P4})}.$$

(2.3)

Here,  $V_{GS,N3}$  is the gate-source voltage of the nMOS mirror transistor  $M_{N3}$ ,  $g_{m,dp}$  is the transconductance of the differential pair transistors ( $M_{N1-2}$ ), while  $r_{ds,N4}$  and  $r_{ds,P4}$  are the dynamic resistances of the output transistors  $M_{N4}$  and  $M_{P4}$ , respectively. Similarly, for the comparator with the pMOS input pair (Fig. 2.3b), the expression for the systematic offset voltage  $V_{OFF,sys}$  is

$$V_{OFFsys} = \frac{V_{GS,P3} + \frac{1}{2}V_{DD}}{g_{m,dp}(r_{ds,N4}||r_{ds,P4})}.$$

(2.4)

Here,  $V_{GS,P3}$  is the gate–source voltage of the transistor  $M_{P3}$ ,  $g_{m,dp}$  is the transconductance of the differential pair transistors ( $M_{P1-2}$ ), while  $r_{ds,N4}$  and  $r_{ds,P4}$  are the dynamic resistances of the output transistors  $M_{N4}$  and  $M_{P4}$ , respectively. According to (2.3) and (2.4), the root cause of the systematic offset voltage is the imbalance in the bias voltages of the internal nodes in combination with the channel length modulation effect of the output transistors. Note that the denominators in (2.3) and (2.4) are equal to the gain of the OTA stage, indicating that a higher gain reduces the systematic offset voltage.

On the other hand, the random offset voltage of a comparator is primarily related to the device mismatch [58, 60]. As derived in Appendix A.1.2, the variance of the overall random offset voltage  $V_{OFFrnd}$  can be calculated as follows:

$$\sigma^{2}(V_{OFFrnd}) = \frac{\sum \sigma^{2}(\Delta I_{D})}{g_{m,dp}^{2}},$$

(2.5)

where the sum of the particular contributions  $\sigma^2(\Delta I_D)$  of the OTA transistors to the overall output current imbalance is evaluated and divided with the transconductance of the differential pair  $g_{m,dp}$ . Specifically, the particular contribution  $\sigma^2(\Delta I_D)$  for each transistor in strong inversion

region can be expressed as

$$\sigma^{2}(\Delta I_{D}) = I_{D}^{2} \frac{A_{KT}^{2}}{WL} + g_{m}^{2} \frac{A_{Vth}^{2}}{WL}$$

(2.6)

and for the transistor in weak inversion as

$$\sigma^2(\Delta I_D) = g_m^2 \frac{A_{Vth}^2}{WL}.$$

(2.7)

Here,  $A_{KT}$  and  $A_{Vth}$  are the mismatch proportionality parameters for the current factor and threshold voltage, having a constant value at a given process, W and L are the width and length of a transistor, and  $g_m$  is the transconductance. Equations (2.5)–(2.7) indicate that larger device area (WL) leads to smaller random offset voltage values. Similarly, a higher transconductance of a differential pair at a given current also reduces the offset voltage, specifically achievable in weak inversion.

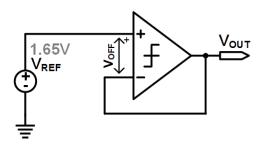

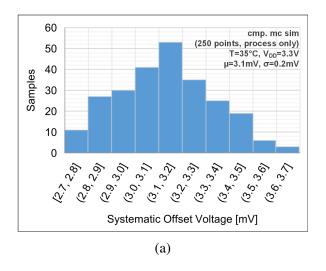

Finally, the systematic and random offset voltage of the benchmark comparator from Fig. 2.3b are simulated assuming the test bench from Fig. 2.4 and the design parameters from Table 2.1. The simulations are performed on 250 Monte Carlo points under the nominal conditions ( $T = 35^{\circ}$ C and  $V_{DD} = 3.3$  V). Here, the Monte Carlo simulations include only pro-

**Figure 2.4:** The test bench for the simulation of the offset voltage of the comparator.

**Figure 2.5:** The simulated offset voltage of the comparator (a) systematic offset voltage  $(V_{OFFsys})$  (b) random offset voltage  $(V_{OFFrnd})$ . The simulations are performed on 250 Monte Carlo points and the nominal environment conditions  $(T = 35^{\circ}\text{C}, V_{DD} = 3.3 \text{ V})$ .

cess variation (device mismatch excluded) for the systematic offset voltage simulation and mismatch (process variations excluded) for the random offset voltage simulation. The simulation results are shown in Fig. 2.5. For the systematic offset voltage, the mean value is  $\mu(V_{OFFsys}) = 3.1$  mV with  $\sigma(V_{OFFsys}) = 0.2$  mV, while for the random offset voltage, the mean value is  $\mu(V_{OFFrnd}) = 0$  mV (since the systematic offset is subtracted from the results) and  $\sigma(V_{OFFrnd}) = 7.1$  mV. Also, the systematic and random offset voltage of a comparator may have a dependency on temperature and supply voltage that needs to be considered during the design phase.

#### 2.3.2 Propagation Delay

The expression for the propagation delay  $(t_d)$  of the comparators from Fig. 2.3, assuming the setup from Fig. 2.6, can be approximated with

$$t_d = \sqrt{\frac{V_{DD}C_{out}}{\Delta V C/\Delta t \cdot \sqrt{2K_T I_{BC}}}}$$

(2.8)

for the input pair in strong inversion (derived in Appendix A.2.1) and

$$t_d = \sqrt{\frac{2nV_T V_{DD} C_{out}}{\Delta V C / \Delta t \cdot I_{BC}}} + \frac{\sqrt{2}}{3} \sqrt{\left(\frac{V_{DD} C_{out}}{4I_{BC}}\right)^3 \cdot \frac{\Delta V C / \Delta t}{nV_T}}$$

(2.9)

for the input pair in weak inversion (derived in Appendix A.2.2). Here,  $V_{DD}$  is the supply voltage,  $C_{out}$  is the effective capacitance of the output node of the OTA (input node of the inverter),  $I_{BC}$  is the comparator bias current,  $\Delta VC/\Delta t$  is the slope of the integrating voltage  $(\Delta VC/\Delta t = I_{REF}/C_{REF})$ ,  $K_T$  is the current factor ( $K_T = \frac{1}{2}\mu_c C_{ox}W/L$ ) of the input transistors, n is the subthreshold slope factor ( $n \approx 1.4 \sim 1.5$ ) [61], and  $V_T$  is the thermal voltage ( $V_T = kT/q$ ). It is also feasible to derive the expression for an input pair in a velocity saturation region, applicable for higher overdrive voltages of the input transistors [59]; nevertheless, since this region leads to very low power efficiency, it is rarely used and thus omitted from this analysis.

Figure 2.6: The test bench for the simulation of the comparator propagation delay.

When operating in the strong inversion (SI) region, as seen in (2.8), the delay is inversely proportional to the fourth root of the bias current  $I_{BC}$  ( $t_d \propto I_{BC}^{-1/4}$ ), meaning that a disproportionate amount of power must be provided to reduce the propagation delay. On the other hand, the weak inversion (WI) operation is much more appropriate regarding the power efficiency. As seen in (2.9), the expression consists of two terms: the first is inversely proportional to the square root of the bias current  $I_{BC}$  ( $\propto I_{BC}^{-1/2}$ ) and more prominent in a moderate inversion, whereas the second ( $\propto I_{BC}^{-3/2}$ ) term becomes dominant for smaller currents. Also, (2.8) and (2.9) reveal the dependency of the propagation delay  $t_d$  on the temperature and the supply voltage: voltage dependency is reflected by the presence of the  $V_{DD}$  factor in both equations, while the dominant contributors to the temperature drift are  $K_T$  for the first equation (due to the temperature dependency of the carrier mobility [62]) and thermal voltage  $V_T$  for the second equation.

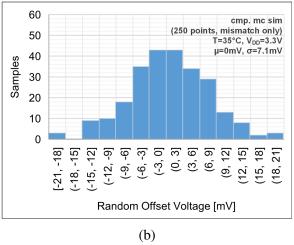

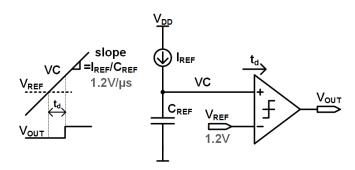

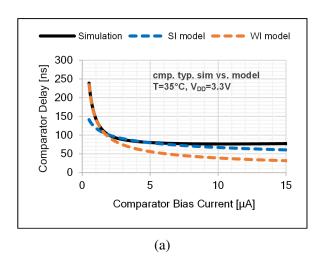

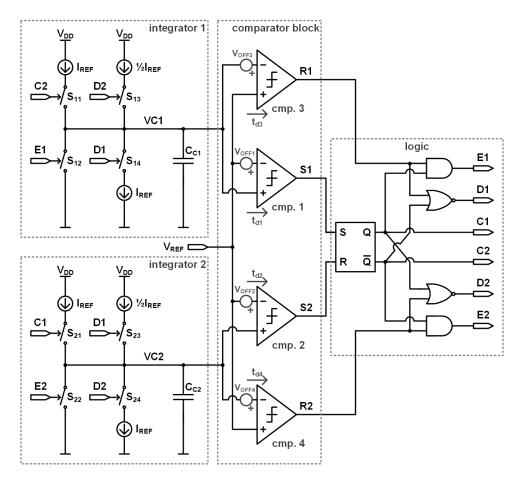

The two presented analytical models for the calculation of the comparator's propagation delay are compared with simulations using the test bench shown in Fig. 2.6, assuming the comparator with the pMOS input pair (Fig. 2.3b) and the design parameters from Table 2.1. The voltage ramp  $V_C$  is applied to the non–inverting input terminal, having the slope  $\Delta V C/\Delta t = 1.2 \text{ V/}\mu\text{s}$ , while the inverting input terminal is connected to the reference voltage  $V_{REF} = 1.2 \text{ V}$ . The fitted parameters  $K_T$ ,  $C_{out}$ , and n used in the model are obtained with the optimization of the process model data and parasitic extraction values.

The comparator delay  $t_d$  is plotted versus the bias current  $I_{BC}$  in Fig. 2.7, simulated for the typical corner under the nominal environment conditions ( $T = 35^{\circ}\text{C}$ ,  $V_{DD} = 3.3 \text{ V}$ ). From the figure, it is evident that a good correspondence between the simulation and the analytical models from (2.8) and (2.9) is achieved, specifically for the weak inversion model in the bias current range up to  $I_{BC} = 1.6 \, \mu\text{A}$  ( $\sim 110 \, \text{mV}$  overdrive voltage), and for the strong inversion model in

**Figure 2.7:** (a) The comparison of the simulated comparator delay  $t_d$  with strong inversion (SI) model and weak inversion (WI) model, plotted vs. comparator bias current  $I_{BC}$ . (b) The error of the analytical model relative to the simulated propagation delay. The simulations are performed at the nominal environment conditions ( $T = 35^{\circ}\text{C}$ ,  $V_{DD} = 3.3 \text{ V}$ ) and typical process corner.

the bias current range 1.6  $\mu$ A  $< I_{BC} < 10$   $\mu$ A. Note that for larger comparator bias currents, specifically  $I_{BC} > 10$   $\mu$ A (overdrive voltages larger than around 0.3 V), the strong inversion model eventually falls off as the input transistors enter the velocity saturation region. The best power versus delay tradeoff is achieved for the comparator bias currents around  $I_{BC} = 2$   $\mu$ A. Here, lower bias currents would result in a substantial delay increase, whereas increasing the power over the recommended levels would provide an insignificant reduction of the propagation delay, especially when going towards the velocity saturation region.

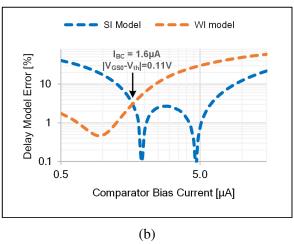

Next, the temperature dependency of the comparator's propagation delay  $t_d$  is simulated both for weak inversion and strong inversion using the bias current of  $I_{BC} = 1 \, \mu A$  and  $I_{BC} = 5 \, \mu A$ , respectively. The temperature range is from  $-40^{\circ} C$  to  $125^{\circ} C$ , and the supply voltage is  $V_{DD} = 3.3 \, V$ . The simulation results are shown in Fig. 2.8 and compared with the corresponding weak inversion (2.9) and strong inversion (2.8) model. Also, for the strong inversion model, it is assumed that the temperature dependency of the parameter  $K_T$  due to the carrier mobility ( $\mu_c$ ) temperature drift is  $K_T \propto T^{-1.5}$  [9, 17]. As seen from the figures, the strong inversion model achieves a nearly perfect fit to the simulation data. On the other hand, the weak inversion model shows a slight discrepancy, originating from the fact that the subthreshold slope factor n is considered constant over the entire temperature range, while in fact, it has a slight positive first–order temperature coefficient [61].

**Figure 2.8:** The comparison of the simulated comparator delay  $t_d$  with the analytical model (a) for weak inversion (WI) at  $I_{BC} = 1 \mu A$  (b) for strong inversion (SI) at  $I_{BC} = 5 \mu A$ ; plotted vs. temperature. The simulations are performed at the typical process corner and nominal supply voltage ( $V_{DD} = 3.3 \text{ V}$ ).

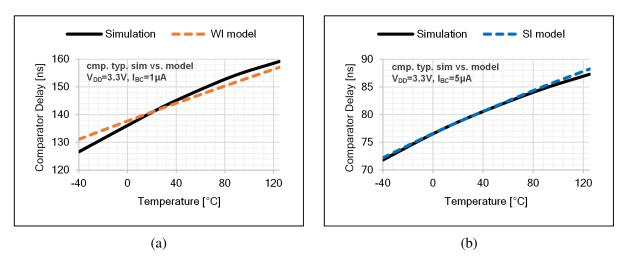

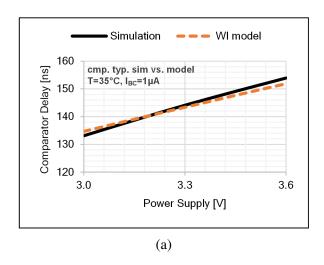

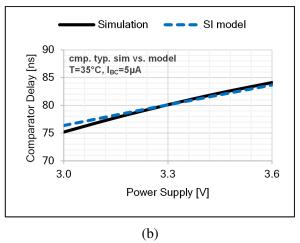

Similarly, the variation of the simulated propagation delay versus supply voltage is plotted in Fig. 2.9 and compared with the corresponding weak inversion (2.9) and strong inversion (2.8) model. The supply voltage range is from 3.0 V to 3.6 V, and the temperature is  $T = 35^{\circ}$ C. As seen from the figures, a considerably good match between the models and the simulation is achieved in both cases.

**Figure 2.9:** The comparison of the simulated comparator delay  $t_d$  with the analytical model (a) for weak inversion (WI) at  $I_{BC} = 1 \mu A$  (b) for strong inversion (SI) at  $I_{BC} = 5 \mu A$ ; plotted vs. supply voltage. The simulations are performed at the typical process corner and nominal temperature ( $T = 35^{\circ}$ C).

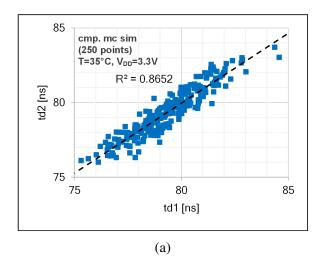

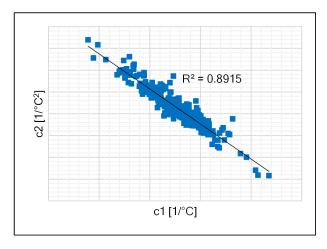

In the end, the simulation of the two comparators subjected to the same process variation and independent mismatch conditions is performed on 250 Monte Carlo points. The simulation results are presented in Fig. 2.10, where a substantial correlation between the propagation delays  $t_{d1}$  and  $t_{d2}$  of the two independent comparators is detected. This implies that the propagation delay of a comparator is primarily related to the process parameters rather than the mismatch. Therefore, it is expected for two identically designed comparators within the oscillator core to have an almost identical propagation delay, specifically  $t_{d1} \approx t_{d2}$ . This fact will be exploited in the continuation of this research, where replica comparators are implemented to cancel the propagation delay's influence on the oscillator timing.

**Figure 2.10:** The simulated propagation delay of two independent comparators subjected to identical process variation (a)  $t_{d1}$  vs.  $t_{d2}$  scatter plot (b) histogram showing the propagation delay difference  $(t_{d1} - t_{d2})$ . The simulations are performed on 250 Monte Carlo points and the nominal environment conditions  $(T = 35^{\circ}\text{C}, V_{DD} = 3.3 \text{ V})$ .

# 2.4 Relaxation Oscillator Core with Replica Comparators

### **2.4.1** Core Architecture

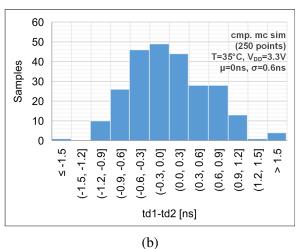

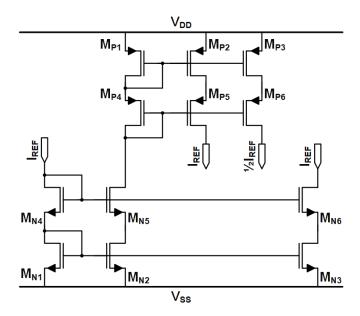

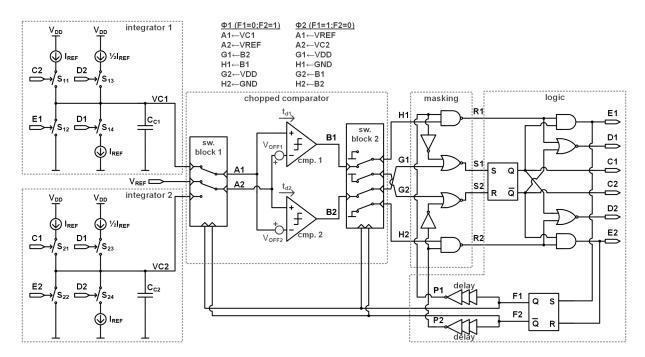

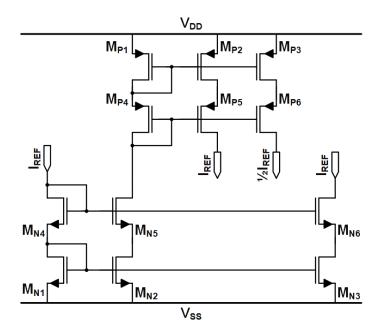

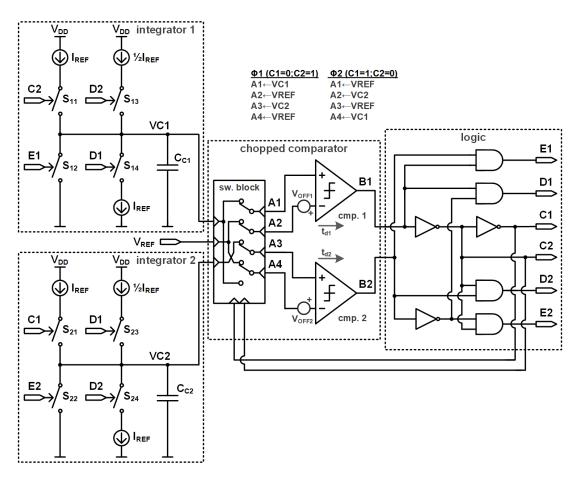

The schematic of the relaxation oscillator core with replica comparators [53] is presented in Fig. 2.11. The oscillator core consists of two integrator blocks, a comparator block, and a logic block. Each integrator block includes three current sources (the first and third having the reference current  $I_{REF}$  and the second one having half the reference current  $1/2I_{REF}$ ), four switches controlled by the output signals of the logic block, and the capacitor having the capacitance value  $C_{REF}$ . The comparator block consists of four identically designed comparators: two sensing comparators and two operating as replica comparators. The logic block processes the comparator outputs into the control signals, feeding them back to the integrator blocks, maintaining the oscillation in this way. Compared to the conventional relaxation oscillator topology from Fig. 2.1, the circuitry for the measurement and cancellation of the timing influence of the comparator stage is added, consisting of two counter–phase comparator replicas and two additional switched current sources inside the integrator blocks.

**Figure 2.11:** The schematic of the relaxation oscillator core with replica comparators, comprising two identical integrator blocks, a comparator block with two sensing and two replica comparators, and a logic block.

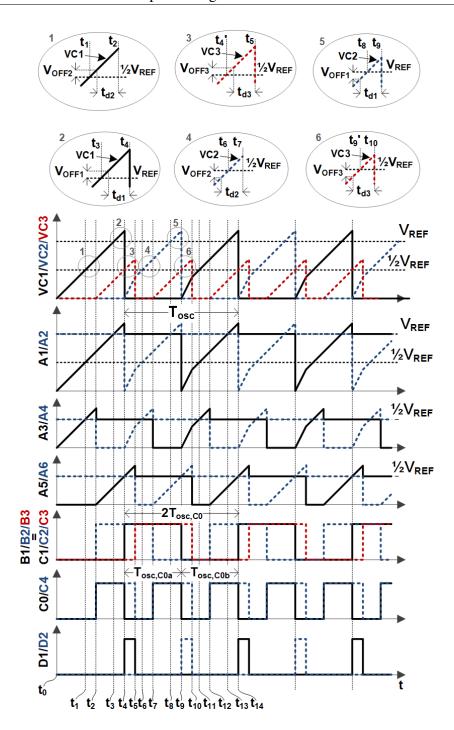

The operation of the relaxation oscillator core with replica comparators is described with reference to the corresponding signal waveforms in Fig. 2.12. At an initial time ( $t = t_0$ ), it is presumed that all the signals are set to the initial state by a start-up circuit (not shown in the schematic). Initially, the integration occurs within the second integrator in the time interval from  $t_0$  to  $t_2$ . The integrating voltage VC2 rises linearly, having the nominal slope  $\Delta VC2/\Delta t = I_{REF}/C_{REF}$ . Meanwhile, the first integrator block remains idle as the integration node VC1 is shorted to the ground reference node  $V_{SS}$  by the switch  $S_{12}$ . At a subsequent time,  $t = t_1$ , the integrating signal VC2 becomes equal to the reference voltage  $V_{REF}$ . Nevertheless, the output of the second comparator S2 changes state to high at  $t = t_2$  due to the non-ideal characteristics of the second comparator, namely the propagation delay  $t_{d2}$  and the offset voltage  $V_{OFF2}$ . The timing can be expressed as follows:

Figure 2.12: The signal waveforms of the relaxation oscillator core with replica comparators.

Following the change of the second comparator output S2, the logic block output signals C1, C2, and D2 also change to low, high, and high, respectively. Consequently, the integration starts within the first integrator block such that the integrating signal VC1 rises linearly, having the slope  $\Delta VC1/\Delta t = 1.5I_{REF}/C_{REF}$ . Meanwhile, the integrating signal VC2 starts to decrease, now having the opposite slope  $\Delta VC2/\Delta t = -I_{REF}/C_{REF}$ . Resulting from the combination of the counter–phase arrangement of the second and fourth comparator and the opposite slopes of the integrating voltage VC2 around the crossover points with the reference voltage  $V_{REF}$  ( $t = t_1$  and  $t = t_3$ ), the operation of the second (sensing) comparator in the time interval from  $t_1$  to  $t_2$  is replicated by the fourth (replica) comparator in the time interval from  $t_3$  to  $t_4$ . Specifically, at  $t = t_3$ , the integrating signal VC2 becomes equal to the reference voltage  $V_{REF}$ . Nevertheless, the output of the fourth comparator R2 changes to high at  $t = t_4$  due to the non–ideal characteristics of the fourth comparator, namely the propagation delay  $t_{d4}$  and the offset voltage  $V_{OFF4}$ . In this way, as a function of the comparator outputs S2 and R2, the logic block generates a positive pulse on the measurement signal D2 in the time interval from  $t_2$  to  $t_4$ , having the duration

$$t_{D2} = t_4 - t_2 = t_{d2} + t_{d4} + \frac{(V_{OFF2} + V_{OFF4})C_{REF}}{I_{REF}}.$$

(2.11)

The influence of the second comparator prior to  $t = t_2$  is compensated with a 50% increase in the slope of the integrating signal VC1 compared to the nominal  $(\Delta VC1/\Delta t = 1.5I_{REF}/C_{REF})$  for the measurement signal pulse duration  $t_{D2}$ . The voltage of the integration node VC1 at the time  $t = t_4$ , hereafter denoted  $VC1(t_4)$ , can be calculated as a function of the slope of the integrating signal  $(\Delta VC1/\Delta t = 1.5I_{REF}/C_{REF})$  and the measurement signal pulse duration  $t_{D2}$ , and can be represented as follows:

$$VC1(t_4) = \Delta VC1/\Delta t \cdot t_{D2} = \frac{3I_{REF}}{2C_{REF}}(t_{d2} + t_{d4}) + \frac{3}{2}(V_{OFF2} + V_{OFF4}). \tag{2.12}$$

After  $t = t_4$ , the integrating signal VC1 continues to rise linearly, having the nominal slope  $\Delta VC1/\Delta t = I_{REF}/C_{REF}$ . Meanwhile, the second integrator block is idle as the integration node VC2 is shorted to the ground reference node  $V_{SS}$  by the switch  $S_{22}$ . At a subsequent time,  $t = t_5$ , the integrating signal VC1 becomes equal to the reference voltage  $V_{REF}$ . Nevertheless, the output of the first comparator S1 changes state to high at  $t = t_6$  due to the non-ideal characteristics of the first comparator, namely the propagation delay  $t_{d1}$  and the offset voltage  $V_{OFF1}$ . The timing can be expressed as follows:

$$t_6 - t_4 = \frac{(V_{REF} + V_{OFF1} - VC1(t_4))C_{REF}}{I_{RFF}} + t_{d1}.$$

(2.13)

Following the change of the first comparator output S1, the logic block output signals C1, C2, and D1 also change to high, low, and high, respectively. Consequently, the integration starts

within the second integrator block such that the integrating signal VC2 rises linearly, having the slope  $\Delta VC2/\Delta t = 1.5I_{REF}/C_{REF}$ . Meanwhile, the integrating signal VC1 starts to decrease, now having the opposite slope  $\Delta VC1/\Delta t = -I_{REF}/C_{REF}$ . Resulting from the combination of the counter-phase arrangement of the first and third comparator and the opposite slopes of the integrating voltage VC1 around the crossover points with the reference voltage  $V_{REF}$  ( $t=t_5$  and  $t=t_7$ ), the operation of the first (sensing) comparator in the time interval from  $t_5$  to  $t_6$  is replicated by the third (replica) comparator in the time interval from  $t_7$  to  $t_8$ . Specifically, at  $t=t_7$ , the integrating signal VC1 becomes equal to the reference voltage  $V_{REF}$ . Nevertheless, the output of the third comparator R1 changes to high at  $t=t_8$  due to the non-ideal characteristics of the third comparator, namely the propagation delay  $t_{d3}$  and the offset voltage  $V_{OFF3}$ . In this way, as a function of the comparator outputs S1 and R1, the logic block generates a positive pulse on the measurement signal D1 in the time interval from  $t_6$  to  $t_8$ , having the duration

$$t_{D1} = t_8 - t_6 = t_{d1} + t_{d3} + \frac{(V_{OFF1} + V_{OFF3})C_{REF}}{I_{RFF}}.$$

(2.14)

The influence of the first comparator prior to  $t = t_6$  is compensated with a 50% increase in the slope of the integrating signal VC2 compared to the nominal  $(\Delta VC2/\Delta t = 1.5I_{REF}/C_{REF})$  for the measurement signal pulse duration  $t_{D1}$ . The voltage of the integration node VC2 at the time  $t = t_8$ , hereafter denoted  $VC2(t_8)$ , can be calculated as a function of the slope of the integrating signal  $(\Delta VC2/\Delta t = 1.5I_{REF}/C_{REF})$  and the measurement signal pulse duration  $t_{D1}$ , and can be represented as follows:

$$VC2(t_8) = \Delta VC2/\Delta t \cdot t_{D1} = \frac{3I_{REF}}{2C_{REF}}(t_{d1} + t_{d3}) + \frac{3}{2}(V_{OFF1} + V_{OFF3}). \tag{2.15}$$

After  $t = t_8$ , the integrating signal VC2 continues to rise linearly, having the nominal slope  $\Delta VC2/\Delta t = I_{REF}/C_{REF}$ . Meanwhile, the first integrator block is idle as the integration node VC1 is shorted to the ground reference node  $V_{SS}$  by the switch  $S_{12}$ . At a subsequent time,  $t = t_9$ , the integrating signal VC2 becomes equal to the reference voltage  $V_{REF}$ . Nevertheless, the output of the second comparator S2 changes state to high at  $t = t_{10}$  due to the non-ideal characteristics of the second comparator, namely the propagation delay  $t_{d2}$  and the offset voltage  $V_{OFF2}$ . The timing can be expressed as follows:

$$t_{10} - t_8 = \frac{(V_{REF} + V_{OFF2} - VC2(t_8))C_{REF}}{I_{REF}} + t_{d2}.$$

(2.16)

With this, a complete oscillation cycle is described from  $t_2$  to  $t_{10}$ . The duration of one oscillation period can be calculated by adding the time segments as follows:

$$T_{osc} = (t_4 - t_2) + (t_6 - t_4) + (t_8 - t_6) + (t_{10} - t_8), \tag{2.17}$$

resulting in

$$T_{osc} = \frac{2(V_{REF} + \frac{1}{2}\delta V_{OFF})C_{REF}}{I_{REF}} + \delta t_d, \qquad (2.18)$$

where

$$\delta V_{OFF} = \frac{1}{2} (V_{OFF1} + V_{OFF2} - V_{OFF3} - V_{OFF4})$$

(2.19)

and

$$\delta t_d = \frac{1}{2} (t_{d1} + t_{d2} - t_{d3} - t_{d4}). \tag{2.20}$$

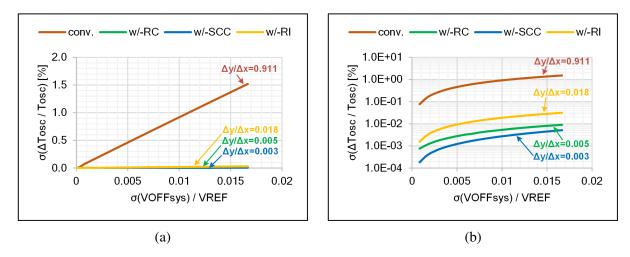

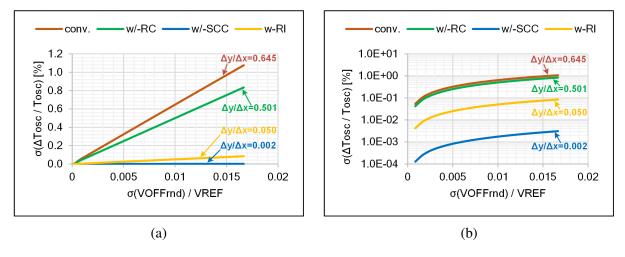

As concluded from (2.18)–(2.20), the oscillation period of the proposed core is primarily determined by the values of the references ( $V_{REF}$ ,  $I_{REF}$ ,  $C_{REF}$ ) since a non–zero value of the residual offset voltage  $\delta V_{OFF}$  and propagation delay  $\delta t_d$  is induced by the relative mismatch of the four comparators. This further implies that the influence of the systematic offset voltage of the comparators is fully compensated, whereas the random offset voltage is not addressed and can potentially compromise the performance. Moreover, in Section 2.3.2, it was demonstrated that the propagation delay variation is mainly related to the process parameters rather than mismatch, meaning that the residual delay  $\delta t_d$  is expected to be negligible. Other minor effects influencing the timing, such as the delay of the logic gates, switching non–idealities, parasitics, and mismatch between the integrator blocks, are neglected within this analysis.

### 2.4.2 Core Prototype

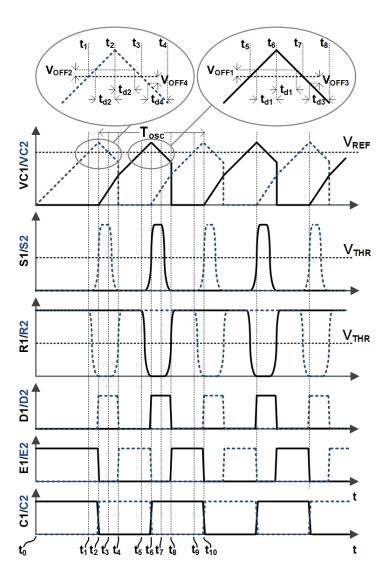

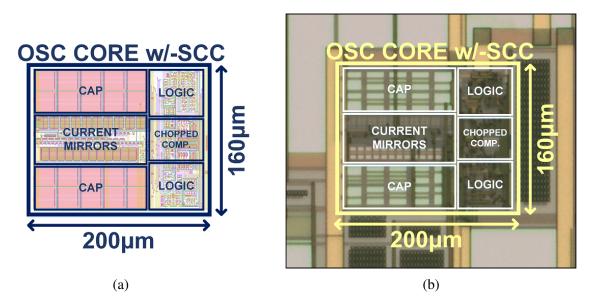

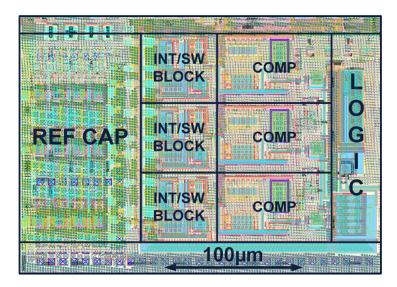

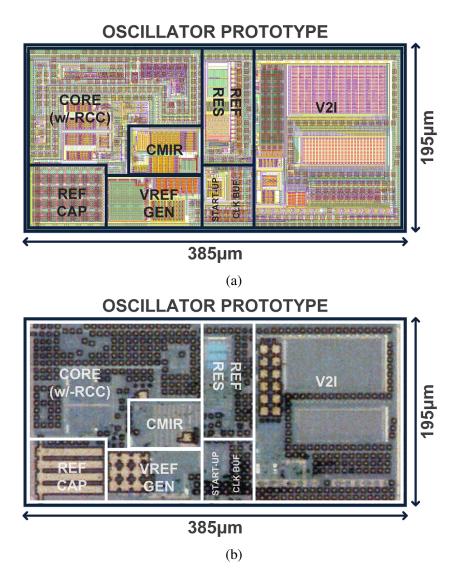

The 1–MHz prototype of the relaxation oscillator core with replica comparators from Fig. 2.11 is designed and manufactured in 0.35– $\mu$ m technology. The prototype layout and the corresponding micro–photography of a manufactured sample are shown in Fig. 2.13, having a total area of 220  $\mu$ m  $\times$  180  $\mu$ m (0.04 mm<sup>2</sup>).

The design parameters of the core prototype are shown in Table 2.2. The switches within the two integrator blocks ( $S_{11-14}$ ,  $S_{21-24}$ ), denoted as  $S_{int}$ , are identical and implemented with a single nMOS transistor. The two reference capacitors  $C_{C1-2}$  are polysilicon—insulator—polysilicon type (PIP). The schematic of four comparators used in the core is shown in Fig. 2.3b, comprising a symmetrical OTA ( $M_{P1-4}$  and  $M_{N1-4}$ ) and an inverter buffer ( $M_{N5}$  and  $M_{P5}$ ). The design parameters of the comparators are shown in Table 2.1.

Additionally, to compare the proposed core's performance to the conventional architecture, the core prototype includes the control circuitry which disables the operation of replica comparators. In this case, the oscillator architecture is reduced to the conventional relaxation oscillator (Fig. 2.1), having a nominal frequency of 0.85 MHz.

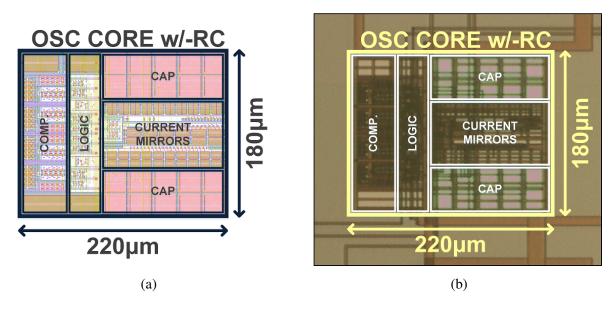

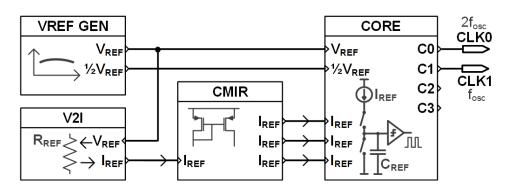

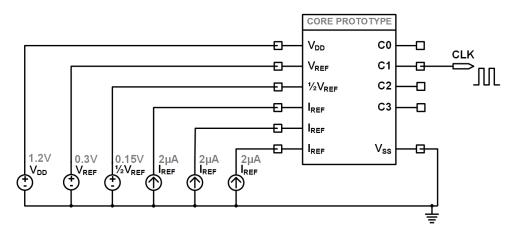

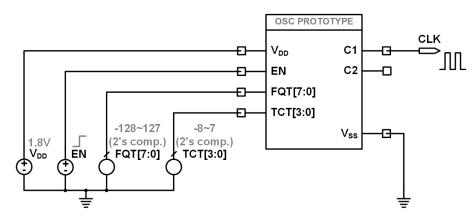

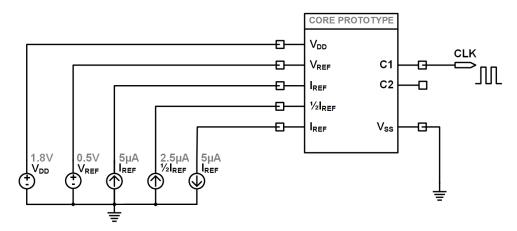

### 2.4.3 Reference Circuitry

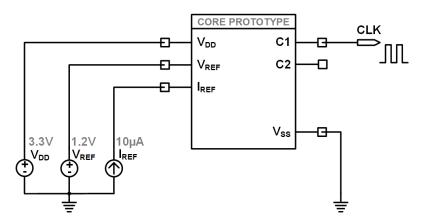

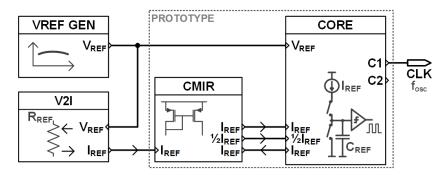

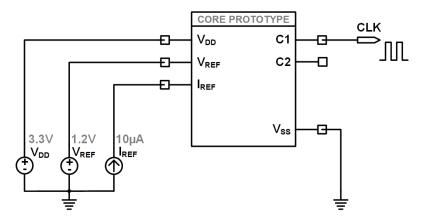

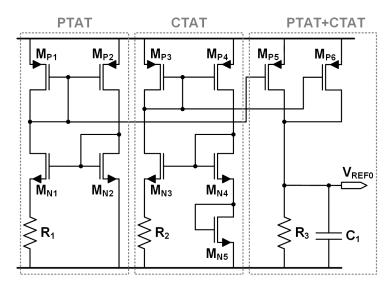

A typical implementation of the relaxation oscillator core with replica comparators (Fig. 2.11) within a self–sustaining clock generator is shown in Fig. 2.14. The core requires a reference voltage  $V_{REF}$ , typically generated within a reference generator (VREF GEN). Furthermore, three required currents (shared between the two integrators) may be generated within a voltage to current converter block (V2I), having the value determined by the ratio of the reference

**Figure 2.13:** The oscillator core with replica comparators prototype (a) layout (b) micro–photography. The core occupies an area of  $0.04 \text{ mm}^2$ .

**Table 2.2:** The design parameters of the relaxation oscillator core prototype with replica comparators.

| Switch           | W [μ <b>m</b> ] | <i>L</i> [μ <b>m</b> ] |          | Device |

|------------------|-----------------|------------------------|----------|--------|

| $S_{int}$        | 0.5             | 0.35                   |          | nmos3v |

| Capacitor        | W [μ <b>m</b> ] | <i>L</i> [μ <b>m</b> ] | Cap [pF] | Device |

| $C_{C1-2}[1:10]$ | 21.4            | 22.2                   | 4.16     | cpip   |

W and L are single finger dimensions. Cap is overall capacitance.

voltage  $V_{REF}$  and a reference resistance  $R_{REF}$ , further replicated within a current mirror block (CMIR). The current mirror block also provides the bias currents for the comparators (not shown in the schematic).

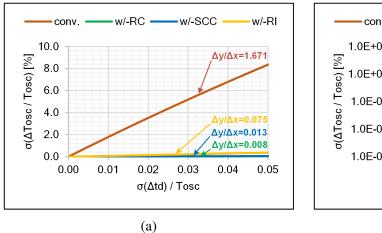

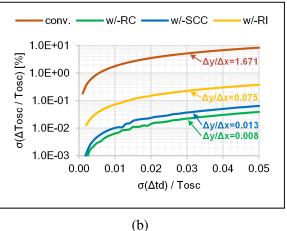

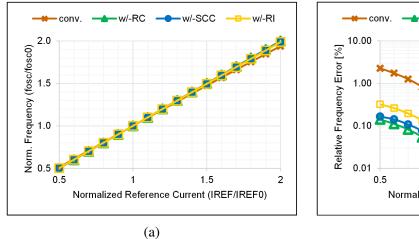

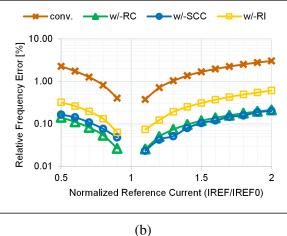

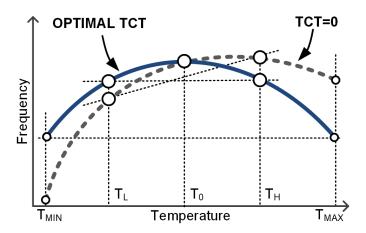

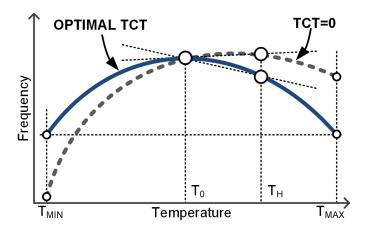

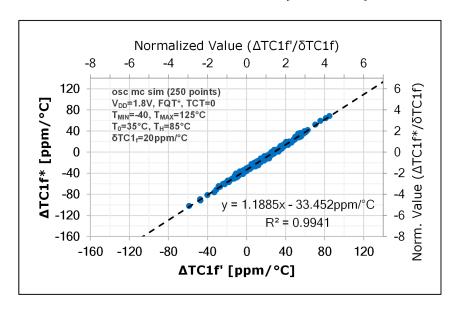

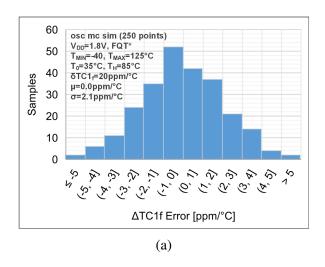

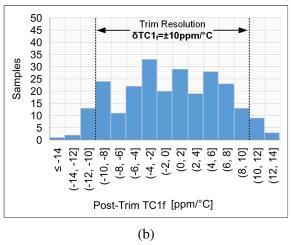

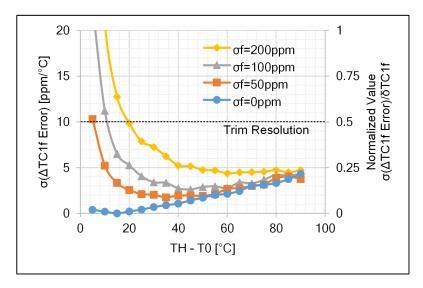

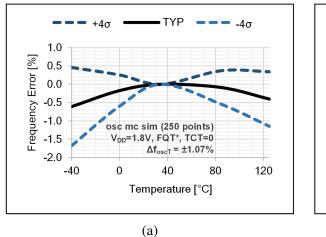

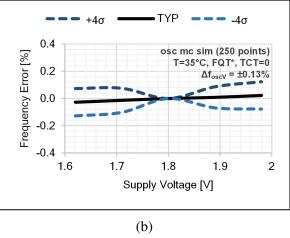

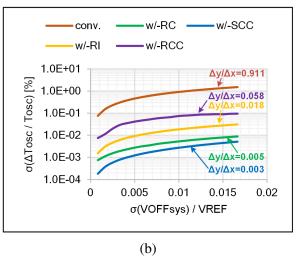

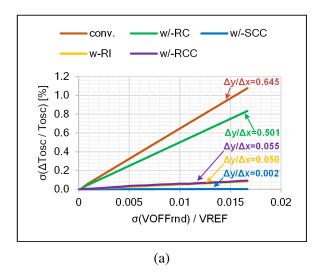

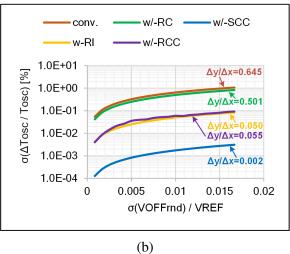

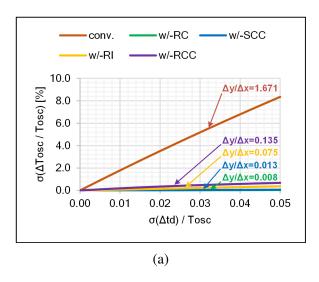

**Figure 2.14:** The diagram of the reference generation scheme, comprising the reference blocks (reference generator and voltage to current converter) and the current mirror block.